# CLAMP MODE에서 동작하는 ZVS-MRC FORWARD 콘버어터에 관한 연구

김희준 \*미스라시문 한 양 대 학 교 전 기 공 학 과

# THE CLAMP MODE FORWARD ZERO-VOLTAGE-SWITCHING MULTI-RESONANT-CONVERTER

Hee-Jun KIM \* Misri Simun

Department of Electrical Engineering Hanyang University

#### ABSTRACT

The clamp mode Zero-Volatge-Switched Multi-Resonant -Converter (ZVS-MRC) is proposed. In the converter, the performance of the conventional ZVS-MRC is improved by clamping the drain-to-source voltage of the power switch using a soft switching nondissipative active clamp network. The analysis for each stage of the converter operation modes is presented and is verified by experiments.

#### I. INTRODUCTION

The SMPS (Switch Mode Power Supply) by PWM (Pulse Width Modulation) has been successfully used for many years. However, there are some disadvantages for operating in high switching frequency, that is, parasitic reactance of the power circuit causes switching stress, power loss and noise. And the stored energy in the wiring and the transformer leakage inductance cause parasitic oscillation and voltage stress exists across drain-source of the power MOSFET (as a main switch) at turn off time.

The ZVS-QRCs have the capability of operating at high frequency, but also have two major limitation. One of the problems is excessive voltage stress at the switching transistor. This voltage stress is proportional to the load range, which make it difficult to implement ZVS-QRCs in applications where the load varies over a wide range. Other problem is caused by the parasitic junction capacitance of the rectifying diode. There are some parasitic oscillations of the resonant inductance and rectifier's capacitance occur in the circuit. If damped, these oscillation cause power dissipation. If undamped, they adversely effect the voltage gain of the converter, which makes the converter difficult to control [6].

ZVS-MRC can absorb all the major parasitic components, including transistor output capacitance, diode junction capacitance, and transformer leakage inductance into the resonant clouit. With these characteristics, ZVS-MRCs have the capability of handling a very wide load range with much reduced voltage stress compared to their CRC counterparts. However, the voltage stress across the MOSFET switch of the ZVS-MRCs is still high as it is compared to that of the PWM type converters. Typically, the voltage stress in ZVS-MRCs is four times the supply voltage. This limits the use of ZVS-MRCs in off-time applications. Furthermore, conduction loss of MOSFET is also increased due to the use of higer voltage rating devices.

This paper proposes a method of improving ZVS-MRC by employing a soft switching nondissipative active clamp network. Clamping action is obtaind by placing, in parallel with the power switch, a series combination of active switch and clamping capacitor, so that the voltage stress across the main switch is clamped to minimum value.

This paper presents the analysis for each stage of the converter operation modes and the experimental result on the converter.

#### II. FORWARD ZVS MRC

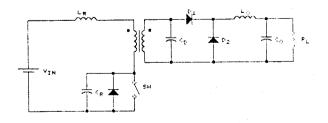

#### 1 FORWARD ZVS-MRC

The basic circuit of forward ZVS-MRC is shown in Fig.1, which operates with wide load range and automatic reseting of the transformer. The forward ZVS MRC is isolated between the primary and the secondary sides of transformer. There are three resonant components at the power circuit: a primary resonant inductor  $L_R$ , a primary resonant capacitor  $C_R$  in parallel with the main switch and a secondary resonant capacitor  $C_D$ . These resonant elements absorb the parasitic reactance of active, passive switches and leakage inductance of transformer. The junction capacitance  $C_{OBB}$  of power MCSFET is absorbed in  $C_R$ , the junction capacitance of rectifying diode is absorbed in  $C_D$ , and the leakage inductance of transformer is absorbed in  $L_R$  in series.

Because the peak voltage stress at turn off time is one of the problems in forward ZVS MRC, we must find the best way and new technique to reduce this voltage stress.

Fig.1 The basic circuit of Forward ZVS-MRC

# 2. THE CLAMP MODE FORWARD ZVS-MRC

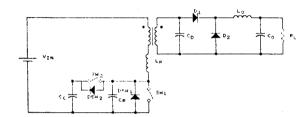

Fig.2 shows the CMF ZVS-MRC (Clamp Mode Forward Zero Voltage Switching Multi Resonant Converter), it also implements zero voltage switching and utilizes all parasitic reactance of the power circuit.

The converter is derived from the forward ZVS-MRC topologies by adding the clamp circuit to the primary side of power circuit. The clamp circuit components are: a clamp capacitor  $C_C$  placed at primary side, and the switch  $SW_2$  in series with the clamp capacitor, the clamp circuit is parallel with the primary resonant capacitor  $C_R$  and the main switch  $SW_1$ . The capacitor  $C_C$  and  $SW_2$  is activated for clamping peak voltage stress of the main switch  $SW_1$  at turn off time.

This proposed converter also has the capability such as the conventional ZVS-MRC. The leakage inductance of the transformer is absorbed into resonant inductor, the junction capacitance of SW2 into clamp capacitor  $C_c$ , and the junction capacitance of SW1 into the resonant capacitor  $C_R$ . Also,  $C_D$  provides automatic resetting of transformer.

Fig. 2 The Clamp Mode Forward ZVS MRC

## III. ANALYSIS OF THE CIRCUIT OPERATION

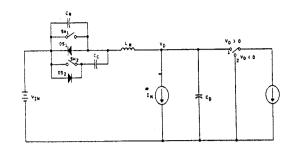

Fig.3 shows an equivalent circuit of the clamp mode forward ZVS-MRC.

- The following assumptions are used in the analysis:

a) the output filter inductance is sufficiently large to be approximated by a current source with a value equal to the output current lo;

- b) the transfomer turns ratio of the primary to the secondary side is unity (N=1);

- c) the magnetizing inductance of the power transfomer is large and can be represented by an equivalent current source, Im, whose magnitude depends on the operating condition but is constant over one switching cycle;

- d) The voltage drop across the conducting semiconductor switches (MOSFETs and diodes) is negligible, and all fundamental elements of circuit is ideal; and

- e) the active and the passive switch element at the semiconductor device are ideal, i.e each switching elements implement zero voltage switching.

To simplify the analysis further, the load current, Io, and the resonant capacitor  $C_D$ , are reflected to the primary side of the transformer and the rectifying diodes are replaced by a SPDT switch. When the voltage across  $C_D$ ,  $V_d$ , is positive, the forward diode  $D_1$  is ON and  $D_2$  is OFF, the switch is at position 1. When it is negative, diode  $D_1$  is OFF and  $D_2$  is ON, it is at position 2.

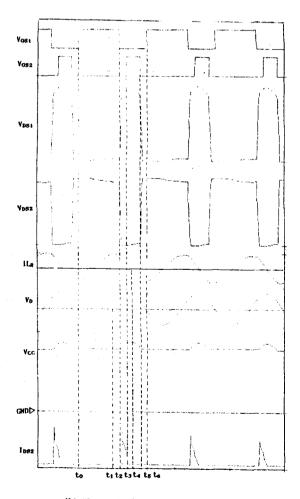

The topological stage of circuit diagrams during one cycle switcing are shown in Fig.4, where the converter can operate in six different modes. Each mode represents a different sequence of topological stages. The sequence at the topological stages is A-B-C-D-E-F. Fig.4(b) shows the waveforms of the clamp mode forward ZVS-MRC in various mode of operation.

The expressions of the resonant current for each topological stages are as follows:

Fig. 3 The eqivalent circuit diagram

$$\begin{split} I_{\bullet} &= \left\{ \begin{array}{ll} I_m & \text{for A} \\ I_{m} \! + \! I_o & \text{for A,B,C,D,E} \\ \text{for stages A and B} \\ \omega_n &= \frac{1}{\sqrt{L_R C_D}} & Z_n &= \sqrt{\frac{L_R}{C_D}} \end{array} \right. \end{split}$$

for stages C and F

$$C_o = \frac{C_D C_R}{C_R + C_D}$$

,  $\omega_o = \frac{1}{\sqrt{L_R C_o}}$  ,  $Z_o = \sqrt{\frac{L_R}{C_o}}$

and for stages D and E

$$Cs = \frac{C_D C_C}{C_C + C_D} \quad \omega_S = \frac{1}{\sqrt{L_R C_S}} \quad Z_S = \sqrt{\frac{L_R}{C_S}}$$

Stage A [ to  $\sim$  t<sub>1</sub> ]

During this stage switch  $SW_1$  and  $D_2$  are conducting (on), and  $SW_2$  and  $D_1$  is off and voltage  $V_D(t)$  across capacitor  $C_D$  is negative. Resonant inductor  $L_R$  and capacitor  $C_D$  cause  $i_LR(t)$  to increase. This stage ends at  $t=t_1$  when voltage  $V_D$  increase to zero, diode  $D_1$  turn on and  $D_2$  to turn off. From Fig. 4(a) we obtain  $i_LR(t)$  and  $V_D(t)$  as follows:

$$i_{LR}(t) = \frac{V_{IN}}{7n} \sin \omega_n t + i_{LR}(t_0) \cos \omega_n t$$

(1)

$V_D(t) = V_{IN}[1-\cos\omega_n t] + i_{LR}(to) Zn Sin\omega_n t + V_D(to)$  (2)

Stage B [  $t_1 \sim ta_2$  ]

$V_D(t)$  increase from zero to the positive value, and the resonant current  $i_{LR}(t)$  reach the peak value. At the end of this stage, the  $SW_1$  turn OFF.

$$i_{LR}(t) = \frac{V_{IN}}{Z_{n}} \sin \omega_{n}t + [i_{LR}(t_{1}) - Ie] \cos \omega_{n}t + Ie \quad (3)$$

$$V_D(t)=V_{IN}[1-\cos\omega_n t] + [i_{LR}(t_1)-I_e]\cos\omega_n t + V_D(t_1)$$

(4)

Stage C [  $t_2 \sim t_3$  ]

After the main switch SW<sub>1</sub> is turn off,  $i_{LR}(t)$  and  $V_C(t)$  are resonated by the three resonant elements  $L_R$ ,  $C_R$  and  $C_D$ .  $V_{DS1}$  are inceased during this stage.  $i_{LR}(t)$ ,  $V_D(t)$  and the voltage across the drain and source of switch SW<sub>1</sub>,  $V_{DS1}(t)$  are obtained as follows: the

$$i_{LR}(t) = \frac{V_{1N}}{Z_0} \operatorname{Sin}\omega_0 t + \left[i_{LR}(t_2) - \frac{\operatorname{IeG}}{C_0}\right] \cos \omega_0 t + \frac{\operatorname{IeC}_0}{C_0}$$

(5)

$$V_{D}(t) = \frac{V_{IN}C_{O}}{C_{D}} (1 - Cos\omega_{O}t) + \left[ \frac{i_{LR}(t_{2})}{C_{D}\omega_{O}} - \frac{IeC_{O}}{\omega_{O}C_{D}^{2}} \right] Sin\omega_{O}t$$

$$+ V_{D}(t_{2}) + \left[ \frac{IeC_{O}}{C_{C}^{2}} - \frac{Ie}{C_{C}} \right]t$$

(6)

$$V_{DS1}(t) = \frac{V_{INCo}}{C_R} (1 - Cos\omega ot) + \left\{ \frac{i_{LR}(t_2)}{C_R\omega o} - \frac{IeC_o}{C_DC_R\omega o} \right\} Sin\omega ot$$

$$+ \frac{IoC_o}{C_DC_R} t$$

$$STAGE A$$

$$STAGE B$$

$$STAGE E$$

$$STAGE C$$

$$STAGE F$$

(a) The topological stages of CM Forward ZVS MRC

# (b) Theoretical waveforms

Fig. 4 The topological stage and theoretical waveforms for each mode of CM Forward ZVS MRC

In this stage, switch  $SW_2$  is turn on, and the valtage across the capacitor,  $C_{\rm c}$ , is more and more increased. As a result, voltage  $V_{\rm DSI}(t)$  is clamped by the voltage across the cpacitor,  $C_{\rm c}$ , and  $i_{\rm LR}(t)$  decrease to zero.

$$i_{LR}(t) = \frac{v_{IN}}{Z_S} \sin \omega_S t + \left(i_{LR}(t_3) - \frac{IeC_S}{C_D}\right) \cos \omega_S t + \frac{IeC_S}{C_D}$$

(8)

$$V_{D}(t) = \frac{V_{IN}C_{S}}{C_{D}} (1 - \cos \omega_{S}t) + \left(\frac{i_{LR}(t_{3})}{C_{D}\omega_{S}} - \frac{IeC_{S}}{\omega_{S}C_{D}^{2}}\right) \sin \omega_{S}t$$

+

$$V_D(t_3)$$

+  $\left(\frac{IeC_S}{C_D^2} - \frac{Ie}{C_D}\right)t$  (8)

$$V_{DS1}(t) = \frac{V_{IM}C_S}{C_C} (1 - Cos\omega_S t) + \left(\frac{i_{LR}(t_3)}{C_C\omega_S} - \frac{IeC_S}{\omega_S C_D C_C}\right) Sin\omega_S t$$

$$+\frac{I_0C_8}{C_0C_6}t + V_{DS1}(t_3)$$

(10)

#### Stage E [ t4 ~ t5 ]

Switch SW2 remains on, the voltage across the capacitor,  $C_C$ , will decrease to the constant value, and the voltage,  $V_{DS1}(t)$ , is still clamped. This stage ends at  $t=t_S$ , when switch SW2 is turned off.

$$i_{LR}(t) = \frac{V_{1N}}{Z_{s}} Sin\omega_{s}t + \left[i_{LR}(t_{4}) - \frac{IeC_{s}}{C_{D}}\right] Cos\omega_{s}t + \frac{IeC_{s}}{C_{D}}$$

(11)

$$V_{D}(t) = \frac{V_{IN}C_{S}}{C_{D}} (1 - \cos \omega_{S}t) + \left[\frac{i_{LR}(t_{4})}{\omega_{S}C_{D}} - \frac{IeC_{S}}{\omega_{S}C_{D}C_{S}}\right] \sin \omega_{S}t$$

$$+ V_D(t_4) + \left(\frac{I_0C_S}{C_D^2} - \frac{I_C}{C_D}\right)t \tag{12}$$

$$V_{DS1}(t) = \frac{V_{1M}C_S}{C_C} (1 - Cos\omega_S t) + \left(\frac{i_{LR}(t_4)}{C_C\omega_S} - \frac{IeC_S}{C_DC_C\omega_S}\right) Sin\omega_S t$$

+  $V_{DS1}(t_4)$  (13)

# Stage F [ ts ~ t6 ]

Main switch  $SW_1$  and clamp switch  $SW_2$  are turn off, the voltage across the  $SW_1$   $V_{DS_1}(t)$  and  $V_D(t)$  is reduced to zero. The cycle is completed when the switch  $SW_1$  is turned on at  $t=t_6$ .

$$\begin{split} &i_{LR}(t) = & \frac{V_{IN}}{V_D} Sin\omega ot + \left[i_{LR}(t_5) - \frac{1eC_0}{C_D}\right] Cos\omega ot + \frac{1eC_0}{C_D} \ (14) \\ &V_D(t) = & \frac{V_{IN}^2 C_0}{C_D} \ (1 - Cos\omega ot) + \left\{\frac{i_{LR}(t_5)}{C_D\omega_0} - \frac{1eC_0}{C_D^2\omega_0}\right\} Sin\omega ot \end{split}$$

$$+\left(\frac{IeC_0}{C_0^2}-\frac{Ie}{C_D}\right)t+V_D(t_5) \tag{15}$$

$$V_{DS1}(t) = \frac{V_{IN}C_0}{C_R} (1 - Cos\omega_0 t) + \left(\frac{i_{LR}(t_5)}{C_R\omega_0} - \frac{IeC_0}{C_0C_R\omega_0}\right) Sin\omega_0 t$$

$$+ \frac{IeC_0}{C_0C_0} t + \frac{V_{DS1}(t_5)}{C_0C_0}$$

(16)

### IV. EXPERIMENT RESULT

A clamp mode Farward ZVS-MRC was breadborded with the following specification.

- o Output Voltage  $V_0 = 5 [V]$

- o Input Voltage  $V_{IN} = 48 [V] \pm 10 [V]$

- o Maximum switching frequency fm max = above 2 [MHz]

- o Maximum output current = 7 [A]

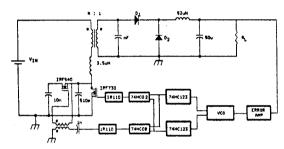

Fig.5 shows the clamp mode forward ZVS MRC with circuit diagram of the converter including gate drive, VCO (Voltage Control Oscillator) and error amplifier using in experiment.

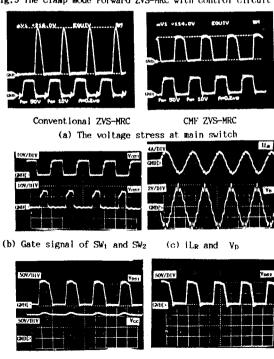

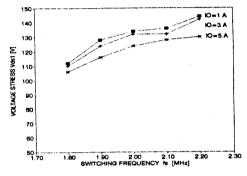

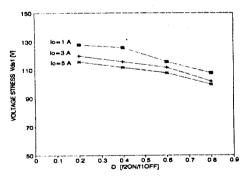

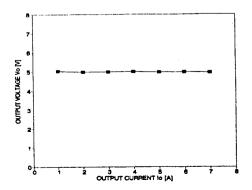

Fig.6 shows oscillograms for the clamp mode Froward ZVS-MRC. Fig.7 shows switching voltage stress of Vds1 versus switching frequency, Fig.8 shows the voltage stress of Vds1 versus the Duty (f2om/f1oFF) variation. Fig.9 shows the stability of output voltage versus load variation measured from the experimental power stage.

#### V. CONCLUSIONS

The analysis and experiments of the clamp mode forward ZVS-MRC are carried out under the conditions of 5V/7A output and 2MHz switching frequency. As a result, we obtain the followings:

- Voltage stress across the main switch is 150V at full load.

- 80% efficiency and less than 1% regulation error at full load.

- Zero-Voltage-Switching is also achived in the clamping circuit.

Fig. 5 The clamp mode Forward ZVS-MRC with control circuit

Fig. 6 The oscillograms for the CM Forward ZVS-MRC.

(d) Vost and Vcc

(e) V<sub>DS2</sub>

#### REFERENCES

- [1] Wojciech A. Tabisz and F.C.Lee," A Novel Zero-Voltage-Switching Multi-Resonant Forward Converter," HFPCC May 1988, PP 309-318.

- [2] H.J.Kim, Tae-Yong Ahn, Chang-Sun Kim, "Phase Shif Controlled Forward ZVS MRC Fixed Switching Frequency." JTC-CSCC '91, PP 121-126.

- [3] H.J.Kim, Tae-Yong Ahn, Jae-Deok Cha, "A New Method For Regulating The Output Voltage In The Forward Zero-Voltage-Switching Multi-Resonant-Converter." JTC-CSCC '91, PP 121-126.

- [4] W.A.Tabisz,F.C.Lee,"DC Analysis and Design of Zero -Voltage-Switching Multi-Resonant Converters." IFFE PESC Record. 1989, PP 243-251.

- [5] R.Takeishi, I.Yoshioka, H.Hiki and S.Kameyama, "ZVS PWM Converter Partial resonance" Intelection, Sec. 20.9, PP 1-6.

- [6] A.W.Lotfi, V. Yorperian, F.C. Lee, "Comparison Of Stress In Quasi-Resonant And Pulse-Width-Modulated Converters," IEEE PESC '88 RECORD (APRIL 1988), PP 5919-598.

Fig. 7. The voltage stress of Vde1 versus switching frequency

Fig. 8 The voltage stress V<sub>d+1</sub> versus the Duty variation.

Fig.9 The stability of output voltage versus load variation