# 마이크로머신을 위한 SOI기술 A SOI Technology for Micromachining

# 정 귀 상 동서공<mark>과대학교</mark> 전자공학과

# Gwiy-Sang Chung

# Dept. of Electronics Eng., Dongseo University of Technology

#### Abstract

A SOI technology is promising for micromachining: high temperature operation, the fabrication easiness of sophisticated and 3D microstructures, radiation hardness, integrated sensors etc. This paper describes reviews of SOI technologies, and their applications to microsensors and microactuators

### I. Introduction

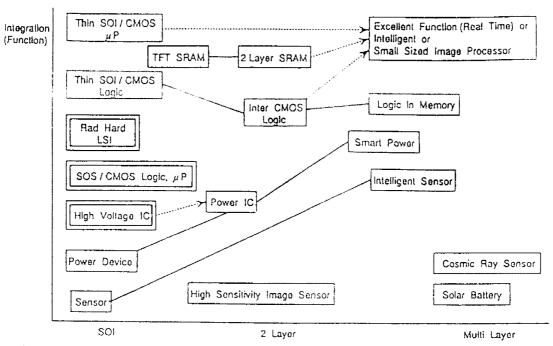

In comparison with widely used junction isolation technology, dielectric isolation technology using thin SOI (semiconductor or Si-on-insulator) structure offers particular advantages such as latch-up free in CMOS device, high-speed operation, high packing density, lower power consumption, and high temperature operation. Owing to these advantages, the SOI structure has been investigated for device applications such as 3-DIC, power, radiation-hard and new TFT's. Recently, combined with micromachining technologies, the SOI structure has also concentrated on applications such as microsensors, microactuators and microstructures. Possible applications of the SOI structure to a variety of microelectronic devices are summarized in Fig. 1.

In this paper, the reviews of the SOI technologies, and their application to microsensors and microactuators such as several types of SOI pressure sensors, hall device, pressure swith and microvalve etc are presented.

# 2. SOI Techologies

When various advantages of a SOI structure are willing to utilize the application of many devices, first of all, the formation of the excellent SOI structure is more and more important, and is indispensable to stack it monolithically. In order to form this SOI structure during recnet years, a number of different SOI formation technologies such as recrystal-lization, epitaxial, insulator buring, and direct bonding have been developed.

## ① Recrystallization method

Recrystallization is usually accomplished by heating the substrate to a fixed bais temperature. Using laser scanning or electron beam irradiation, additional energy then directed to the surface of the wafer melts the thin SOI layer of deposited amorphous or polycrystalline Si.

### 2 Epitaxial growth method

A single heteroepitaxial growth of SOS, and a double heteroepitaxial growth of insul- ator and Si films on Si substrate have been worked to form the SOI structure. SOS has been under investi- gation for the last fifteen years and has been used to fabricate several special devices. On the other hand, double heteroepitaxial SOI structures using epitaxial insulator materials such as  $MgO.Al_2O_3$ ,  $CaF_2$ ,  $(Y_2O)_n(ZrO_2)_{1-n}$ , SrO and  $Al_2O_3$  has been reported.

# 3 Insulator buring method

SIMOX, the formation of buried insulator layer by the energetic implantation of oxygen or nitrogen ion is another method of fabricating the SOI structure.

FIPOS is a technique for forming individual of Si surrounded by insulating material. The process is based on forming porous Si by anodic dissolution of a portion of the crystalline Si in an aqueous HF solution.

## 4 Adhesion method

During the past decade, wafer-bonding technology have become the focus of a great deal of research. Among various wafer-bonding techniques, anodic bonding has been widely used for making pressure sensors and other devices. However, this technology has various limitations.

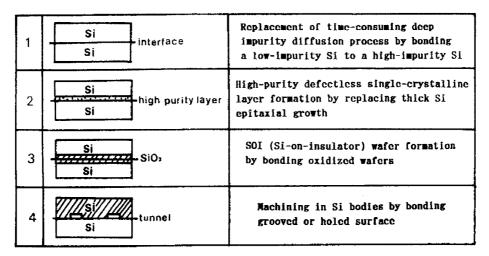

Two pieces of Si-wafer without any additional glue and with or without surface layer of themally grown  $\mathrm{SiO}_2$  can be bonded together at room temperature without any additional force applied. The bonded wafer is thinned by mechanical-chemical polishing or planarization etchants. The SDB technology offers a number of advantages, and these merits will be appears potenti-

ally attractive in many areas of applicationas shown in Fig. 2 for new functional devices and process.

Each technology has various advantages depending on the applications. To judge the relative merits of these technologies, Table 1 lists the important SOI technologies and compares their various characteristics including substrate and film formation, cost, material quality for integrated circuit applications.

# 3. Application to Miromachining

#### ① Pressure sensors

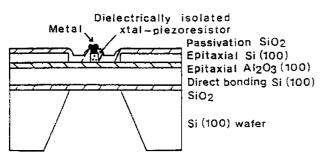

SOI pressure sensors using double SOI structures, i.e.,  $Si/Al_2O_3/Si/SiO_2/Si$  substrate which were formed by combining SDB technology with epitaxial growth was fabricated as shown in Fig.3. A first SOI layer is employed as an etch stop layer during KOH selective anisotropic etching and for controlling the thickness of the thin membrane, epitaxially grown second SOI layer on the first SOI layer is used as the dielectrically isolated piezoresistors. Typical characteristics of SOI pressure transducers fabricated on the double SOI structures are summarized in Table 2.

## 2 Hall devices

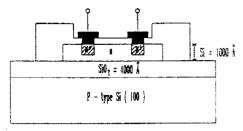

Hall devices that can be used in high temperature environment are particularly in demand for automotive, aircraft engine and FA system. The performance of most planar Si hall devices using junction isolation method deteriorates at temperature ablive roughly 200 °C due to the leakage current of a pn junction. As one of vehicle for solving of limitations mentioned, hall devices using a SOI structure seem to effective, which are possible to operate in a higher temperature region because hall devices are dielectrically isolated by the insulator of a SOI structure as shown in Fig. 4. Typical output characteristics of the fabricated SOI hall devices against magnentic field without any compensation are summarized in Table 3.

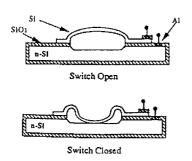

## (3) Pressure switch

Switches which close or open at predetermined pressure levels have a number of applications in consumer products, automotive systems, tire pressure monitoring tactile sensor arrays, keybords, scales, and industrial controls. In which it is often desirable to have hysteresis in the behavior of these

switches to prevent switching during small fluctuations of the parameter being sensed. Michael et al was reported on a Si micromachined threshold pressure switch using mechanical hysteresis, Fig. 5 is a schematic illustration of the pressure switch which is composed of a mechanically compliant upper Si electrode separated from the lower Si electrode by an insulating layer( $SiO_2$ ). It was tested the threshold pressure switch and found that of exhibits approximately 2 psi of hysteresis.

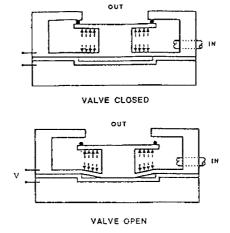

# 4 Microvalve

Using the basic concept to have the pressure of the fluid provide a balaning force on the moving part of the value, micromachined microvalue as shown in Fig. 6 was fabricated by 4. Schmidt et al. This structure is designed to enhance the limited actuation forces available in microfabricated devices with integated actuation mechanisms. The fluid pressure produces an upward directed force tending to close the valve and simultaneously a downward directed force tending to open the valve, Typical characteristics is as following. First, is the very abrupt change in flow at a threshold pressure for both opening (from an initial value of 12 psi to 5.1 psi at 60 psi across the valve) and closing (from 12 psi to 22 psi at 60 psi across the valve). Second, is hysteresis in the flow-pressure characteristics that begins to appear as the pressure across the valve is increased

#### 4. Conclusion

The combining the SOI techologies and micromachining technologies is powerful and versatile alternative process for realizing electrical devices, microsensors and microactuators with a new function: A good dielectrical isolation between the device elements and the substrate offers high temperature operation, high speed, high power and high density.

### References

- 1) G.S.Chung et al, J. Appl. Phys. 30 (1991) 143.

- 2) 6, S. Chung et al., Sensors & Actuators 29 (1991) 107.

- 3) G.S.Chung et al., Sensors & Actuators 39 (1993) 241.

- 4) Schmidt et al. Transducers '91(1991) 177.

- 5) Michael et al, Transducers'93(1993) 98.

Fig. 1 Application of a SOI structure to devices classified by the number of active layers and functions.

Table 1 Comparison of typical SOI technologies

|                       | the transfer of the second |                    |                        |                          | P                       |

|-----------------------|----------------------------|--------------------|------------------------|--------------------------|-------------------------|

| Types                 | ZMR                        | SOS                | ZOMIZ                  | FIPOS                    | SDB                     |

| Technical<br>maturity | developing                 | mature             | developing             | developing               | developing              |

| Crystal<br>quality    | good                       | good               | exellent               | exellent                 | very<br>exellent        |

| Mobility              | high                       | high               | very high              | very high                | very high               |

| Leakage<br>current    | moderate/<br>low           | very low           | moderate/<br>low       | moderate/low             | very low                |

| Circuits              | LSI                        | VLSI               | LSI                    | VIS1                     | LSI                     |

| Usable<br>SOI area    | small                      | full wafer         | full wafer             | small                    | full wafer              |

| Wafer<br>throughput   | moderate/<br>low           | moderate           | low                    | low                      | low                     |

| Wafer cost            | moderate                   | high               | high                   | moderate                 | moderate .              |

| Special advantages    | process<br>control         | crystal<br>quality | crystal<br>quality     | crystal<br>quality       | versatile<br>structures |

| Process<br>advantages | like Si                    | like Si            | like Si                | like Si                  | like Si                 |

| Special defects       | not batch                  | 1                  | not batch, selectivity | stress,<br>nonuniformity | thinning                |

Fig. 2 Application of a SDB technology

Fig. 3 Schematic cross-section of pressure sensors using double SOI structures.

Fig. 4. Schematic cross-section of the SOI Hall sensors.

Fig. 5 Schematic cross-section of microswitch.

Table 2. Typical characteristics of SOI pressure transducers fabricated on double SOI structures.

|                                | Si/Al <sub>2</sub> O <sub>3</sub> /Si/SiO <sub>2</sub> /Si |  |

|--------------------------------|------------------------------------------------------------|--|

| Pressure range                 | 0-700 mmHg                                                 |  |

| Supply voltage                 | 5 V d.c                                                    |  |

| Sensitivity                    | 0.04 mV/VmmaHg                                             |  |

| Nonlinearity                   | + 0.15 %FS                                                 |  |

| Hysteresis                     | + 0.05 %FS                                                 |  |

| Presuure sensitivity variation | $\pm$ 2.4 %s.d                                             |  |

| Temperature range              | - 20 to + 350 ℃                                            |  |

| Dependence of sensitivity      | - 0,2 %                                                    |  |

| Dependence of offset voltage   | + 0,1 %                                                    |  |

Table 3. Typical characteristics of SOI hall devices using the insulator of a SOI structure as the dielectrically isolated layer of hall devices.

| Temperature range            | + 20 to + 260 °C  |

|------------------------------|-------------------|

|                              | (I=0.05mA, B=1kG) |

| Dependence of sensitivity    | 0.55 %/℃          |

| Depentence of offset voltage | 1, <b>92</b> %/°C |

| Product sensitivity          | 480 [V/AT]        |

Fig. 6 Schematic cross-section of microvalve.