# COMMON-MODE VOLTAGE PULSE CANCELLATION METHOD BASED ON SPACE-VECTOR PWM IN CONVERTER-INVERTER SYSTEM

### Hyeoun-Dong Lee and Seung-Ki Sul

School of Electrical Engineering, Seoul National University, Seoul, Korea

San 56-1, Shillim-Dong, Kwanak-Ku, Seoul, Korea (ZIP 151-742)

Tel: +82-2-880-7243 Fax: +82-2-878-1452 E-mail: sulsk@plaza.snu.ac.kr

Abstract - This paper proposes the advanced PWM method that can reduce common-mode voltage in three-phase PWM converter-inverter system. By the proper distribution of the zero-voltage vector of inverter, it is possible to cancel out a common-mode voltage pulse in a sampling period. Since the proposed PWM method maintains the effective-voltage vector, it does not affect the control performance of converter-inverter system. Without any extra hardware, overall common-mode voltage can be decreased by one-third compared with conventional PWM scheme.

#### I. INTRODUCTION

Numerous problems accompanied by common-mode voltage due to high-speed pulse width modulation have been reported in many AC machine drive applications; leakage current flowing through the stray capacitance between motor winding and frame[1,2], radiated and conducted EMI(Electromagnetic Interference) problem [3,4], bearing current and shaft voltage[5,6], breakdown of motor insulation and so on. Thus, concerns about these problems have been increased and many studies for reducing the common-mode voltage have been progressed all over the world. Some works focused on the design of common-mode choke/transformer[1,2] or the fourth leg in conventional converter[7,8]. Since these methods require additional hardware, the drawbacks of increase in inverter weight and volume or complexity in its control are unavoidable. And the filter or transformer parameters should be redesigned according to various

applications. In recent, researches for reduction of the common-mode voltage using PWM scheme came to the front[9,10]. However, in these methods, large ripples in motor currents have to be encountered due to the absence of zero-voltage vector, and there exists a limitation of modulation index because of synthesis of zero-voltage vector using effective voltage vectors.

This paper proposes a PWM method that can reduce common-mode voltage in three-phase **PWM** converter/inverter system. By shifting the effectivevoltage vector of inverter in a sampling period, it is possible to eliminate a common-mode voltage pulse. Hence, overall common-mode voltage can be reduced to two-third compared with three-phase symmetric PWM scheme case. The proposed PWM method maintains the effective-voltage vector and just manipulates the zerovoltage vector, so that it does not aggravate the control performance of converter/inverter system. And it can be easily implemented in software without any extra hardware.

# II. RELATIONSHIP BETWEEN COMMON-MODE VOLTAGE AND SWITCHING FUNCTION

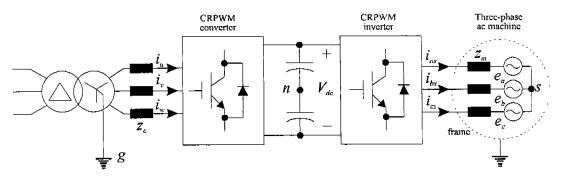

Fig. 1 shows three-phase PWM boost converter and inverter system widely used in ac machine drives. The voltage-current equations for converter-inverter system can be given by (1) for source side and (2) for load side.

Fig. 1. Three-phase PWM converter-inverter system for ac machine drive(g:grounding point, s:stator neutral).

## Proceedings ICPE '98, Seoul

$$\begin{cases} v_{ug} = -z_c i_u + e_u \\ v_{vg} = -z_c i_v + e_v & \text{for source side} \\ v_{wg} = -z_c i_w + e_w \end{cases}$$

(1)

$$\begin{cases} v_{as} = z_m i_{as} + e_a \\ v_{bs} = z_m i_{bs} + e_b \quad \text{for load side} \\ v_{cs} = z_m i_{cs} + e_c \end{cases}$$

(2)

Assuming the balanced three-phase source and load, and taking the virtual mid-point of dc bus, 'n', the voltage difference between ground, 'g' and 'n',  $v_{gn}$  can be described as (3). In the same way, the voltage difference between 'n' and stator neutral, 's' can be described as (4).

$$v_{gn} = \frac{v_{ug} + v_{vg} + v_{wg}}{3} \tag{3}$$

$$v_{sn} = \frac{v_{as} + v_{bs} + v_{cs}}{3} \tag{4}$$

Since, generally, the neutral point of the star-connected three-phase source is connected to the ground('g' in Fig. 1), and the motor frame is also connected to the same ground, the common-mode voltage in this system corresponds to the voltage difference between the ground and the stator neutral('s' in Fig. 1). From (3) and (4), the common-mode voltage,  $v_{sg}$ , can be determined as (5)

$$v_{sg} = v_{sn} - v_{gn}$$

$$= \frac{(v_{as} + v_{bs} + v_{cs}) - (v_{ug} + v_{vg} + v_{ug})}{3}$$

(5)

Using the switching functions of converter and inverter,  $s_i$ , (i=a,b,c,u,v,w),  $v_{sg}$  can be therefore determined as (6), consequently

$$v_{,g} = \frac{V_{dc}}{3} \left[ \left( s_a + s_b + s_c \right) - \left( s_u + s_v + s_w \right) \right]$$

(6)

From (6), it can be known that the both the switching states of the converter-inverter and dc-bus voltage,  $V_{dc}$  decide the common mode voltage, regardless of the motor impedance.

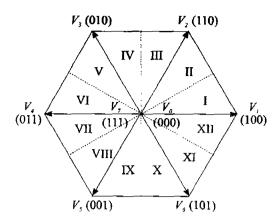

Even if there are eight states available for the output voltage vector according to eight switching functions of both the converter and the inverter as illustrated in Fig. 2, possible  $v_{sg}$  has seven states(0,  $\pm V_{dc}/3$ ,  $\pm 2V_{dc}/3$ ,  $\pm V_{dc}/3$ , which are summarized in Table 1. From Table 1,

Fig. 2. Voltage vectors according to switching states of converter and inverter in space vector plane, and sectors(I~XII).

TABLE 1. COMMON MODE VOLTAGE ACCORDING TO OUTPUT VOLTAGE VECTORS OF CONVERTER AND INVERTER

|                                            |                 | Output voltage vector of Inv. |                    |              |                     |  |  |  |

|--------------------------------------------|-----------------|-------------------------------|--------------------|--------------|---------------------|--|--|--|

|                                            |                 | $V_1, V_3, V_5$               | $V_2, V_4, V_6$    | $V_0$        | $V_{7}$             |  |  |  |

| Output<br>voltage<br>vector<br>of<br>Conv. | $V_1, V_3, V_5$ | 0                             | V <sub>dc</sub> /3 | $-V_{dc}/3$  | 2V <sub>dc</sub> /3 |  |  |  |

|                                            | $V_2, V_4, V_6$ | $-V_{dc}/3$                   | 0                  | $-2V_{dc}/3$ | $V_{dc}/3$          |  |  |  |

|                                            | $V_0$           | $V_{dc}/3$                    | $2V_{dc}/3$        | 0            | $V_{dc}$            |  |  |  |

|                                            | V <sub>7</sub>  | $-2V_{dc}/3$                  | $-V_{dc}/3$        | $-V_{dc}$    | 0                   |  |  |  |

it can be seen that  $v_{sg}$  changes by  $V_{de}/3$  every switching of converter and inverter, and has  $V_{de}$  peak when the different two zero voltage vectors are applied. Dc-bus voltage of  $v_{sg}$  can be avoided if the synchronism between starting point of switching for both converter and inverter with same switching frequency is guaranteed.

#### III. PWM STRATEGY ELIMINATING A COMMON-MODE VOLTAGE PULSE

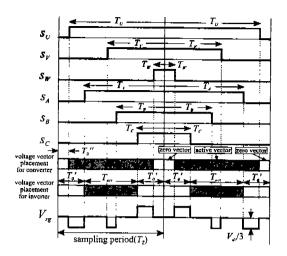

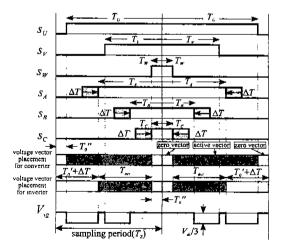

Fig. 3 shows the relationship between the switching functions of converter-inverter and the common-mode voltage when using conventional three-phase symmetric PWM method. It can be known that the disagreement between the switching points of converter and inverter brings out the common-mode voltage pulses. Six switching actions of converter and inverter occur in a sampling period,  $T_Z$ , as shown in Fig. 3. Thus, three common-mode voltage pulses are generated, of which magnitude is equal to  $V_{dc}/3$ . Since the synchronism of the converter and inverter control is confirmed, there exists no common-mode voltage pulse of  $\pm V_{dc}$ . When the magnitude of the active space vector of the inverter is

Fig. 3. Switching functions of converter and inverter, and common-mode voltage using conventional symmetric SVPWM.

very small, there can exist the common-mode voltage of  $2V_{dc}/3$

This paper proposes the PWM method that can eliminate one common-mode voltage pulse in a sampling period. Since the common-mode voltage pulse results from the disagreement between the switching points of the converter and the inverter, it is possible to eliminate one common-mode voltage pulse in a sampling period by shifting an inverter switching point and aligning this to one of the converter switching points.

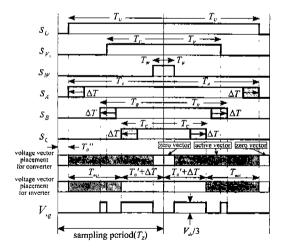

There can exist two kind of the switching alignment

- Shifting the inverter switching point of the largest pole voltage reference and aligning this to the converter switching point of the largest pole voltage reference (Method I).

- Shifting the inverter switching point of the smallest

Fig. 4. Switching functions of converter and inverter, and common-mode voltage using proposed reduction method I.

pole voltage reference and aligning this to the converter switching point of the <u>smallest</u> pole voltage reference (Method II).

In method I, the active space vector of inverter is shifted left by  $\Delta T$ . As shown in ON-sequence of Fig. 4, the starting points of the active space vectors for both converter and inverter are aligned, making the zero space vector time for inverter  $T_0 (= T_0' - \Delta T)$  be equal to the zero space vector time for converter  $T_0'''$ . Then the first one of common-mode voltage pulse train is eliminated compared to  $v_{sg}$  in Fig. 3. In method B, the active space vector for inverter is shifted right by  $\Delta T$ , and the end points of the active space vectors are aligned, making  $T_0 (= T_0' + \Delta T)$  be equal to  $T_0'''$ , as shown in Fig. 5. Then the last one of common-mode voltage pulse train is eliminated.

$\Delta T$  can be computed as (7). Since the modulation index of the converter is generally larger than that of the inverter in variable ac machine drives,  $\Delta T$  is positive. If  $\Delta T$  is negative, the proposed reduction method can be realized by shifting the active space vector of the converter rather than the active space vector of the inverter.

$$\Delta T = T_0'' - T_0' = T_0'' - (T_2 - T_{ord})/2 \tag{7}$$

In Figs. 4 and 5, note that the number of generated common-mode voltage pulses is reduced to two, although six switching actions of converter-inverter occur in  $T_Z$ . Compare this with three of the conventional symmetric SVPWM. Hence, using the proposed reduction method, the leakage current produced by high dv/dt common-mode voltage pulses can be reduced to two third of the conventional method.

Fig. 5. Switching functions of converter and inverter, and common-mode voltage using proposed reduction method II.

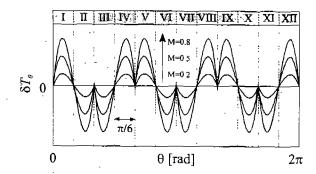

Fig. 6. Dependency of  $\delta T_0$  on modulation index and angle.

### IV. SHIFTING ACTIVE SPACE VECTOR AND RMS RIPPLE CURRENT OF THREE-PHASE LOAD

The square rms of ripple current,  $I_{npple}^2$  depends on the placement of the zero space vector in a sampling period[11,12]. Thus, in the proposed method,  $I_{npple}^2$  can be increased compared to that of the symmetrical SVPWM. Since  $I_{npple}^2$  is given by a polynomial dependent to  $T_0$ , the optimal zero space vector time that provides minimum  $I_{npple}^2$  can be computed and defined as  $T_{0\_opt}$ . The difference between the zero space vector time in conventional symmetric SVPWM,  $T_0'$  (= $(T_Z-T_{act})/2$ ) and  $T_{0\_opt}$  is defined as  $\delta T_0$ , and can be computed as (8).

$$T_{0}' - T_{0_{-}opt} = \frac{T_{z}}{V_{dc}} \cdot \frac{\left(V_{\alpha}^{*} + V_{\gamma}^{*}\right)\left(2V_{\alpha}^{*} + V_{\gamma}^{*}\right)\left(V_{\alpha}^{*} + 2V_{\gamma}^{*}\right)}{4\left(V_{\alpha}^{*2} + V_{\alpha}^{*}V_{\gamma}^{*} + V_{\gamma}^{*2}\right)} = \delta T_{0}$$

(8)

where,  $V_{\alpha}^{*}$  and  $V_{\gamma}^{*}$  are the largest and the smallest one among voltage references of the inverter, respectively.

The dependence of  $\delta T_0$  on modulation index, M, and inverter voltage angle,  $\theta$ , is depicted in Fig. 6. If  $\delta T_0 > 0$ , it can be concluded that method A is more effective than method B. If  $\delta T_0 < 0$ , method B is preferred to method A, in that the increase in  $I_{npple}^2$  due to the shift of the active space vector placement is minimized. From Fig. 6, the choice of the aligning

method can be confirmed only by sector in which the reference voltage lies, regardless of the modulation index, and is presented in Table 2.

#### V. EXPERIMENTAL RESULTS

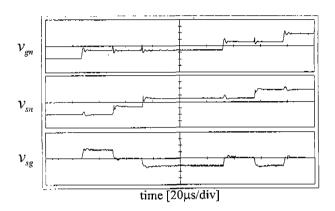

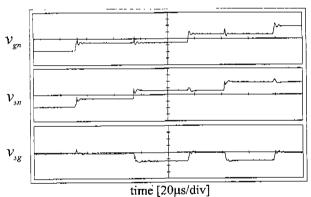

In the experiments, the PWM boost converter controls dc bus voltage,  $V_{dc}$  as 370V, and 22kW induction machine is operated with constant V/f ratio. The sampling periods for both converter and inverter are 200 $\mu$ s, and are synchronized each other.

In Fig. 7,  $v_{gn}$ ,  $v_{sn}$  and  $v_{sg}$  during  $T_z$  are presented when using the conventional symmetric SVPWM.  $v_{on}$ and  $v_{sn}$  denote the voltage difference between virtual ground, n and source ground and stator neutral, respectively. The virtual ground, n that can be realized by accessing the mid-point of the dc bus capacitor.  $v_{gn}$  and  $v_{sn}$  are  $\pm V_{dc}/2$  when zero space vectors are applied, and  $\pm V_{dc}/6$  for active space vectors. It can be easily found that there exist three common-mode voltage pulses according to converter and inverter switching states. In Fig. 8, it can be shown that the starting points of the active space vectors of the converter and inverter are aligned. Thus first common-mode voltage pulse is eliminated, and the number of generated common-mode voltage pulses is reduced to two, using the proposed reduction method.

# IV. CONCLUSIONS

In this paper, the common-mode voltage in three-phase PWM converter-inverter system is defined according to the switching functions and analyzed. Based on the conventional SVPWM, the proposed method eliminates one common-mode voltage pulse in one sampling period by shifting the inverter active space vector and aligning this to that of the converter. Possible two methods are presented and the choice between two methods is confirmed according to the inverter output angle, minimizing the increase of rms ripple current.

With the help of the proposed reduction scheme, the number of generated common-mode voltage pulses can be reduced to **two**, compared with **three** of the conventional symmetric SVPWM method, so that overall

Table 2. Choice between method A or B minimizing the increase in  $I_{cont}^2$ .

| Sector | I | П | ш | IV | ν | VI | VII | VIII | ΙX | х | ΧI | xn |

|--------|---|---|---|----|---|----|-----|------|----|---|----|----|

| Method | Α | В | В | A  | A | В  | В   | Α    | Α  | В | В  | A  |

dv/dt current can be decreased by one third. Since the proposed reduction method maintains the active space vector and redistributes the zero space vector, it does not aggravate the control performance of converter-inverter system. In addition, the proposed method can be easily implemented in software without any extra hardware.

Fig. 7. Experimental results when using conventional Symmetric SVPWM( $v_{gn}$ ,  $v_{sn}$ ,  $v_{sg}$ :100[V/div]).

Fig. 8. Experimental results when using proposed reduction method( $v_{gn}$ ,  $v_{sn}$ ,  $v_{sg}$ :100[V/div]).

#### REFERENCES

- [1] Y. Murai, T. Kubota and Y. Kawase, "Leakage Current Reduction for a High-Frequency Carrier Inverter Feeding an Induction Machine," *IEEE Trans. Ind. Appl.*, vol. 28, no. 4, pp. 858-863, Jul./Aug., 1992.

- [2] S. Ogasawara and H. Akagi, "Modeling and Damping of High-Frequency Leakage Currents in PWM Inverter-Fed AC Motor Drive Systems," *IEEE IAS Annual Meeting*, pp. 29-36, 1995.

- [3] M. A. Jabbar and M. A. Rahman, "Radio Frequency Interference of Electric Motor and Associated Controls," *IEEE Trans. Ind. Appl.*, vol. 27, no. 1, pp. 27-31, Jan./Feb., 1991

- [4] E. Zhong, S. Chen and T. A. Lipo, "Improvement in EMI Performance of Inverter-Fed Motor Drives," *IEEE APEC Conf. Rec.*, pp. 608-614, 1994.

- [5] S. Chen, T. A. Lipo and D. Fitzegrald, "Modeling of Motor Bearing Currents in PWM Inverter Drives," *IEEE IAS Annual Meeting*, pp. 388-393, 1995.

- [6] J. M. Erdman, R. J. Kerkman, D. W. Schlegel and G. L. Skibinski, "Effect of PWM Inverters on AC Motor Bearing Currents and Shaft Voltages," *IEEE Trans. Ind. Appl.*, vol. 32, no. 2, pp. 250-259, Mar./Apr., 1996.

- [7] A. L. Julian, T. A. Lipo and G. Oriti, "Elimination of Common Mode Voltage in Three Phase Sinusoidal Power Converters," *IEEE PESC Conf. Rec.*, pp. 1968-1972, 1996.

- [8] S. Ogasawara, H. Ayano and H. Akagi, "An Active Circuit for Cancellation Common-Mode Voltage Generated by a PWM Inverter," *IEEE PESC Conf. Rec.*, pp. 1547-1553, 1997.

- [9] M. Cacciato, A. Consoli, G. Scarcella and A. Testa, "Reduction of Common Mode Currents in PWM Inverter Motor Drives," *IEEE IAS Annual Meeting*, pp. 707-713, 1997.

- [10] M. Cacciato, A. Consoli, G. Scarcella and A. Testa, "Continuous PWM to Square Wave Inverter Control with Low Common Mode Emissions," *IEEE PESC Conf. Rec.*, pp. 871-877, 1998.

- [11] D. G. Holmes, "The Significance of Zero Space Vector Placement for Carrier-Based PWM Schemes," *IEEE Trans. Ind. Appl.*, vol. 32, no. 5, pp. 1122-1129, Sep./Oct., 1996.

- [12] V. Blasco, "Analysis of a Hybrid PWM based on Modified Space-Vector and Triangle-Comparison Methods," *IEEE Trans. Ind. Appl.*, vol. 33, no. 3, pp. 756-764, May/Jun., 1997.