# A New Control Model for a 3\$\phi\$ PWM Converter with Digital Current Controller Considering Delay and SVPWM Effects

Dong-Ki Min<sup>1</sup>, Sung-Chan Ahn<sup>2</sup>, Dong-Seok Hyun<sup>3</sup> 1: Samsung Advanced Institute of Technology, Seoul, Korea 2,3: Dept. of Electrical Eng., Hanyang University, Seoul, Korea

Abstract - In design of a digital current controller for a 3phase (3φ) voltage-source (VS) PWM converter, its conventional model, i.e., stationary or synchronous reference frame model, is used in obtaining its discretized version. It introduces, however, inherent errors since the following practical problems are not taken into consideration: the characteristics of the space vector-based pulse-width modulation (SVPWM) and the time delays in the process of sampling and computation. In this paper, the new hybrid reference frame model of the 36 VS PWM converter is proposed considering these problems. In addition, the direct digital current controller based on this model is designed without any prediction or extrapolation algorithm to compensate the time delay. So the control algorithm is made very simple. It represents no steady-state error in input current control and has the optimized transient responses. The validity of the proposed algorithm is proved by the computer simulation and experimental results.

#### I. INTRODUCTION

The advantages in using  $3\phi$  VS PWM converters in high performance AC motor drive system are as follows [1][2]:

- The input current can be controlled to be sinusoidal, which results in a reduction in the lower-order current harmonics.

- The phase of the input current with respect to the input voltage can be adjustable, which means that the input power factor is controllable.

- The DC link voltage can be regulated fast and stable against the variation in the load.

- The excess power in the load side can be regenerated into the input side.

To take these advantages fully, both the sufficient analysis of the given system and the accurate design of its controller are required. In this paper, two subjects that are overlooked in modeling of a 3φ VS PWM converter and designing its current controller will be discussed: (1) characteristics of a pulsewidth modulated signal based on space vector theory and time delay between sampling the signals and manipulating the control output.

In a PWM VS inverter-fed drive or converter system, the pulsewidth-modulated voltage has been approximated to only its fundamental component, which may cause some significant errors as the switching frequency decreases.

In digital control system, there always is a time delay since A/D and D/A conversions and computations take

time. In one of the recent papers, O. Kukrer [3] discussed the discrete-time current controller of a  $3\phi$  VS PWM inverter having a time delay between sampling and the application of the inverter voltage to the system and proposed the modified control law using a prediction algorithm to eliminate the undesirable effects of the time delay. However, the time delay must be modeled to the system and the controller is much complex.

In this paper, a new mathematical model of the  $3\phi$  VS PWM converter is proposed based on the analysis of a pulsewidth-modulated voltage based on space vector theory and a time delay due to the process of sampling and computing. Then a direct digital current controller are designed based on this new model having no steady-state error and an optimized dynamic response by the ITAE criterion. The validity of the proposed control algorithm is proved by the computer simulation and experimental results.

# II. MODELING OF A 3¢ VS PWM CONVERTER AND ITS CONVENTIONAL MODELS

In this section, a  $3\phi$  VS PWM converter system will be mathematically modeled in the time domain, then its conventional models based on the space vector theory are reviewed.

# A. Modeling of a 3 \phi VS PWM Converter

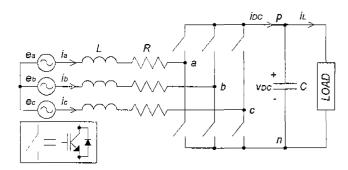

In a  $3\phi$  VS PWM converter as shown in Fig. 1, the following dynamic equations can be obtained assuming that the instantaneous sum of the input voltages is zero, there is no neutral line at source side, and each phase has the same input inductance L and effective input resistance

Fig. 1. Circuit diagram of a 3\phi VS PWM converter

# Proceedings ICPE '98, Seoul

R[1]:

$$\dot{\mathbf{i}}_{abc}(t) = -\frac{R}{L} \mathbf{i}_{abc}(t) - \frac{1}{L} \mathbf{v}_{abc}(t) + \frac{1}{L} \mathbf{e}_{abc}(t)$$

(1)

$$\mathbf{v}_{abc} = \mathbf{v}_{abcn} + v_{no} \mathbf{I}_{3} = v_{DC} \cdot \mathbf{s}_{abc} - \frac{v_{DC}}{3} \cdot \mathbf{s}_{abc}$$

$$= \frac{v_{DC}}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \mathbf{s}_{abc}$$

(2)

$$i_{DC} = \mathbf{s}_{abc}^T \mathbf{i}_{abc} \tag{3}$$

$$\dot{\mathbf{v}}_{DC} = \frac{1}{C} \left( i_{DC} - i_L \right) \tag{4}$$

where

$$\mathbf{x}_{abc}^{T} = \begin{bmatrix} x_a & x_b & x_c \end{bmatrix}, \mathbf{x} \in \{\mathbf{i}, \mathbf{v}, \mathbf{e}, \mathbf{s}\}$$

i: input current vector

v: converter voltage vector

e: source voltage vector

s: switching function vector

$I_3: 3\times 3$  identity matrix

$i_{DC}$ : converter output DC current

$v_{DC}$ : DC link voltage

$i_L$ : load current

T: transpose of the vector

The switching function  $s_x$  has a value of 1 if the upper switch or its anti-parallel diode of leg x is on conduction or has a value of 0 if the lower is on conduction, i.e.,

$$s_x = \begin{cases} 1 & \text{if} \quad v_{kn} = v_{IX} \\ 0 & \text{if} \quad v_{kn} = 0 \end{cases}$$

(5)

# B. Stationary Reference Frame Model

If the instantaneous sum of the three-phase variables, which are not necessary to be symmetric or balanced, is equal to zero, then they can be represented with the space vectors in the stationary reference frame [5] by the following equation:

$$\mathbf{x}_{\alpha\beta} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \mathbf{x}_{abc}$$

(6)

As all the three-phase variables in this system, as assumed before, meet the condition, (1) can be represented as

$$\dot{\mathbf{i}}_{\alpha\beta}(t) = \mathbf{A}_{s} \mathbf{i}_{\alpha\beta}(t) + \mathbf{B} \mathbf{v}_{\alpha\beta}(t) - \mathbf{B} \mathbf{e}_{\alpha\beta}(t)$$

(7)

where  $\mathbf{A}_s = -\frac{R}{L}\mathbf{I}_2$ ,  $\mathbf{B} = -\frac{1}{L}\mathbf{I}_2$ , and  $\mathbf{I}_2$  is a 2×2 identity matrix.

The variables represented in the stationary reference frame can be transformed into the variables in the synchronous reference frame.

$$\mathbf{x}_{dq} = \mathbf{C}^{-1}(\theta)\mathbf{x}_{\alpha\beta} \tag{8}$$

where  $\mathbf{C}(\theta) = \begin{bmatrix} \cos \theta & -\sin \theta \\ \sin \theta & \cos \theta \end{bmatrix}$  and  $\theta$  is the angle between

the direct axes of the two reference frames.

Note that if the three-phase variables in (6) are sinusoidal symmetric, then the variables in (8) are constant.

Assume that the direct axis of the synchronous reference frame is set to coincide with the source voltage vector  $\mathbf{e}_{\alpha\beta}$ , which means the quadrature component of the source voltage,  $e_q$ , is zero. Also  $\mathbf{e}_{dq}$  is constant. Using (8), the dynamic equation of (7) can be rewritten as

$$\dot{\mathbf{i}}_{da}(t) = \mathbf{A}_c \mathbf{i}_{da}(t) + \mathbf{B} \mathbf{v}_{da}(t) - \mathbf{B} \mathbf{e}_{da}(t)$$

(9)

where  $\mathbf{A}_e = \begin{bmatrix} -R/L & \omega \\ -\omega & -R/L \end{bmatrix}$  and  $\omega$  is the angular speed

of the source voltage vector.

# III. HYBRID REFERENCE FRAME MODEL

In the design of a direct digital controller [4], the continuous-time model is discretized and simplified with the assumption of a constant control input during a control period T. In the 3 $\phi$  VS PWM converter system, however, this assumption is not satisfied. The reason will be explained at the following subsection. Then the new model, referred as hybrid reference frame model, is proposed.

#### A. Characteristics of the Signals

The sinusoidal source voltage vector in the stationary reference frame in (7),  $\mathbf{e}_{\alpha\beta}$ , is not constant during the current control period T but the source voltage vector in

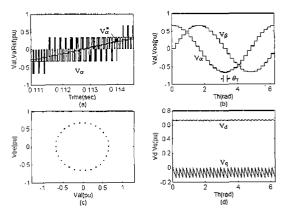

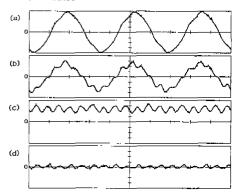

Fig. 2. Converter voltage modulated by SVPWM (a) real and reference voltage waveforms (T=200 $\mu$ s) (b) in the stationary reference frame ( $\theta_T$ =2 $\pi$ /30) (c) in the voltage space vector plane – (d) in the synchronous reference frame

the synchronous reference frame,  $e_{dq}$ , in (9) is constant.

On the other hand, the converter voltage,  $\mathbf{v}_{\alpha\beta}$ , shows pulsewidth modulated pattern and its analysis may be difficult. However, if the converter voltage is modulated by SVPWM, then its analysis can be easily done. This results from the principle of SVPWM. The converter voltage is synthesized by its two adjacent switching vectors,  $\mathbf{V}_a$  and  $\mathbf{V}_b$  to be equal to a given voltage reference vector  $\mathbf{V}_{\alpha\beta}^*$  in average of a switching period T [6]:

$$\left\langle \mathbf{v}_{\alpha\beta} \right\rangle_{T} = \frac{1}{T} \int_{T} \mathbf{v}_{\alpha\beta} (t) dt = \frac{1}{T} \left( T_{a} \mathbf{V}_{a} + T_{b} \mathbf{V}_{b} \right) = \mathbf{V}_{\alpha\beta}^{*}$$

(10)

where  $T_a$  and  $T_b$  are the on-state duration of the switching vectors  $\mathbf{V}_a$  and  $\mathbf{V}_b$  respectively.

Therefore, the resultant voltage could be equal to the reference voltage vector that is piecewise constant during T as shown in Fig. 2(a). Then, direct and quadrature components of the converter voltage normalized by the DC link voltage are piecewise constant in the stationary reference frame as shown in Fig. 2(b). Its trajectory in the voltage space vector plane is shown in Fig. 2(c). In the synchronous reference frame, direct and quadrature components of the converter voltage vector are not piecewise constant as shown in Fig. 2(d).

Therefore, in the stationary reference frame model of  $3\phi$  VS PWM converter, the real converter voltage can be approximated to be piecewise constant but, in the synchronous reference frame, it can not be piecewise constant. Note that it is contrary for the source voltage.

# B. Time Delays in Sampling and Computation

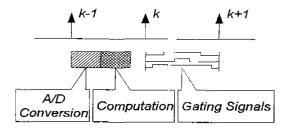

Any digital control system has a time delay in the process of sampling and computation [7]. Such inherent delay must be included in modeling the system.

All signals needed for making the reference voltage are sampled simultaneously and then the on-times of each phase are computed. In case of SVPWM, the switching frequency is constant so that the gating signals of each phase are fired periodically and synchronously. Fig. 3 shows the time sequence of sampling, computation, and gating signals. In this case, one unit of a time delay is produced.

# C. Hybrid Reference Frame Model

Fig. 3. Time sequence of sampling, computation, and gating signals.

To obtain an accurate discrete-time model from the continuous-time model of the 3φ VS PWM converter, the characteristics of the signals and a time delay in the digital control system have been discussed in the above two subsections. Now the new model considering them will be derived.

The stationary reference frame model with one unit of the time delay in applying the converter voltage can be rewritten as

$$\dot{\mathbf{i}}_{\alpha\beta}(t) = \mathbf{A}_{s} \dot{\mathbf{i}}_{\alpha\beta}(t) + \mathbf{B} \mathbf{v}_{\alpha\beta}(t - T) - \mathbf{B} \mathbf{e}_{\alpha\beta}(t) \tag{11}$$

In this model, the converter voltage is piecewise constant but the source voltage is not. So the discrete-time model can not be obtained easily from (11).

Therefore, to represent the source voltage to be piecewise constant, it must be represented in the synchronous reference frame. Then (11) can be

$$\dot{\mathbf{i}}_{dq}(t) = \mathbf{A}_e \mathbf{i}_{dq}(t) + \mathbf{B}\mathbf{C}^{-1}(\theta) \mathbf{v}_{\alpha\beta}(t-T) - \mathbf{B}\mathbf{e}_{dq}(t)$$

(12)

In (12), the input current and the source voltage are represented in the synchronous reference frame and the converter voltage is in stationary reference frame. We defined this new continuous-time model as a hybrid reference frame model because both frames are referred. Also, note that all signals are piecewise constant during T so that this model can be simply discretized without any errors.

# IV. DIGITAL CURRENT CONTROLLER DESIGN

The continuous-time hybrid reference frame model of the  $3\phi$  VS PWM converter is first discretized. Then a direct digital current controller is designed for the discrete-time system. The parameters are obtained by matching the optimal poles of the prototype third-order continuous-time system.

# A. Discretization of the Hybrid Reference Frame Model

From the complete solution of (12), the current vector at k+1 step can be obtained as

$$\mathbf{i}_{dq}(kT+T) = e^{\mathbf{A}_{c}T} \mathbf{i}_{dq}(kT)

+ \left( \int_{0}^{\tau} e^{\mathbf{A}_{c}T} \mathbf{C}^{-1}(\omega(kT+T-\tau)) \mathbf{B} d\tau \right) \mathbf{v}_{\alpha\beta}(kT-T)

- \left( \int_{0}^{\tau} e^{\mathbf{A}_{c}T} \mathbf{B} d\tau \right) \mathbf{e}_{dq}(kT)

= \mathbf{A}_{cd} \mathbf{i}_{dq}(kT) + \hat{\mathbf{B}}_{d} \mathbf{v}_{dq}(kT-T) - \mathbf{B}_{d} \mathbf{e}_{dq}(kT)$$

(13)

where

Here

$$\mathbf{A}_{ed} = e^{\mathbf{A}_{e}\tau},$$

$$\hat{\mathbf{B}}_{d} = \left(\int_{0}^{T} e^{\mathbf{A}_{e}\tau} \mathbf{C}(\omega \tau) \mathbf{B} d\tau\right) \mathbf{C}^{-1} (2\omega T),$$

$$\mathbf{B}_{d} = \int_{0}^{T} e^{\mathbf{A}_{e}\tau} \mathbf{B} d\tau.$$

In (13),  $\mathbf{C}^{-1}(\omega T + T)$  and  $\mathbf{v}_{\alpha\beta}(kT - T)$  can be out from

the integral operator because none of them is a function of time, and then the converter voltage is represented in the synchronous reference frame. Among the above matrices,  $\mathbf{A}_{ed}$  and  $\mathbf{B}_{d}$  can be easily numerically evaluated using standard mathematical tools, e.g., c2d of MATLAB, but evaluating  $\hat{\mathbf{B}}_{d}$  is not so easy.

However, it can be approximated as

$$\hat{\mathbf{B}}_{d} \approx \left( \int_{0}^{T} e^{\mathbf{A}_{c} \tau} \mathbf{B} d\tau \right) \mathbf{C} \left( \frac{\omega T}{2} \right) \mathbf{C}^{-1} \left( 2\omega T \right) = \mathbf{B}_{d} \mathbf{C}^{-1} \left( \frac{3\omega T}{2} \right)$$

(14)

#### B. Control Structure

The structure of the digital current controller is given as

$$\mathbf{v}_{dq}^{\star}(kT) = \mathbf{L}_{1}\mathbf{i}_{dq}(kT) + \mathbf{L}_{2}\mathbf{i}_{dq}(kT - T) + \mathbf{M}_{1}\mathbf{i}_{dd}^{\star}(kT) + \mathbf{N}_{1}\mathbf{e}_{dd}(kT)$$

(15)

where  $\mathbf{L}_1$ ,  $\mathbf{L}_2$ ,  $\mathbf{M}_1$ , and  $\mathbf{N}_1$  are  $2\times 2$  gain matrices to be determined.

The current controller of (15) is simple and its parameters can be easily determined. Note that the gain matrices may not be diagonal so that the coupling effects due to the time delay can be compensated.

Substitution of (15) in (13) and defining the matrix  $\hat{\mathbf{X}} = \hat{\mathbf{B}}_d \mathbf{X}$ ,  $\mathbf{X} \in \{\mathbf{I}, \mathbf{V}, \mathbf{E}\}$  result in

$$\mathbf{i}_{dq}(kT+T) = \mathbf{A}_{cd} \mathbf{i}_{dq}(kT) + \hat{\mathbf{L}}_{1} \mathbf{i}_{dq}(kT-T)$$

$$+ \hat{\mathbf{L}}_{2} \mathbf{i}_{dq}(kT-2T) + \hat{\mathbf{M}}_{1} \mathbf{i}_{dq}^{*}(kT-T)$$

$$+ \hat{\mathbf{N}}_{1} \mathbf{e}_{dq}(kT-T) - \mathbf{B}_{d} \mathbf{e}_{dq}(kT)$$

(16)

### C. No Steady-State Error Condition

If the current vector,  $\mathbf{i}_{dq}$ , is convergent to its reference vector,  $\mathbf{I}_{dq}^{\star}$ , then the following steady state equation can be obtained as

$$(\mathbf{I}_2 - \mathbf{A}_{cd} - \hat{\mathbf{L}}_1 - \hat{\mathbf{L}}_2 - \hat{\mathbf{M}}_1)\mathbf{I}_{da}^* = (\hat{\mathbf{N}}_1 - \mathbf{B}_d)\mathbf{e}_{da}$$

(17)

Two conditions for no steady-state errors in the input current control are

$$\hat{\mathbf{M}}_{1} = \mathbf{I}_{2} + \mathbf{A}_{cd} - \hat{\mathbf{L}}_{1} - \hat{\mathbf{L}}_{2} \tag{18}$$

$$\hat{\mathbf{N}}_1 = \mathbf{B}_d \tag{19}$$

Since the source voltage is not a function of time, (19) ensures that the source voltage can not affect current control.

# D. Decoupling Condition

To derive the decoupling condition, the transfer function matrix, T(z), is necessary and it can be obtained from the z-transformation of (16) as

$$\mathbf{I}_{dq}(z) = \mathbf{T}(z)\mathbf{I}_{dq}^{*}(z) = \mathbf{P}^{-1}(z)\hat{\mathbf{M}}_{1}\mathbf{I}_{dq}^{*}(z)$$

(20)

where

$$P(z) = z^2 I_2 - z A_{ed} - \hat{L}_1 - z^{-1} \hat{L}_2$$

.

The transfer function matrix is given as

$$\mathbf{T}(z) = \mathbf{P}^{-1}(z)\hat{\mathbf{M}}_{1}$$

$$= \frac{1}{\det \mathbf{P}(z)} \begin{bmatrix} p_{22}(z) & -p_{12}(z) \\ -p_{21}(z) & p_{11}(z) \end{bmatrix} \begin{bmatrix} \hat{m}_{11} & \hat{m}_{12} \\ \hat{m}_{21} & \hat{m}_{22} \end{bmatrix}$$

(21)

where  $p_{ij}$  and  $\hat{m}_{ij}$  are entries of P(z) and  $\hat{M}_1$  respectively.

The decoupling control, or non-interactive control can be achieved if the off-diagonal terms of the transfer function matrix, T(z), becomes zero as

$$\hat{m}_{12}p_{22}(z) - \hat{m}_{22}p_{12}(z) = 0 {(22a)}$$

$$-\hat{m}_{11}p_{21}(z) + \hat{m}_{21}p_{11}(z) = 0 (22b)$$

Although there are many ways to determine the gain matrices, it is convenient that the off-diagonal terms of  $\hat{\mathbf{M}}_1$  set to zero and the off-diagonal terms of  $\mathbf{P}(z)$  shrink to zero by setting the off-diagonal terms of  $\hat{\mathbf{L}}_1$  and  $\hat{\mathbf{L}}_2$ .

$$\hat{m}_{12} = \hat{m}_{21} = 0 \tag{23}$$

$$\hat{l}_{1,12} = -\hat{l}_{1,21} = -2a_{12}, \quad \hat{l}_{2,12} = -\hat{l}_{2,12} = a_{12}$$

(24)

where  $a_n$  is an entry of  $\mathbf{A}_{ed}$ .

Parameters of (24) are derived from the first-order Lagrange interpolation formula [3] and meet the no steady-state error condition of (18).

#### E. Pole Assignment

The transfer function of the direct component of the input current can be simplified if the current control is decoupled as

$$\frac{I_d(z)}{I_d^*(z)} = \frac{\hat{m}_{11} p_{22}(z) - \hat{m}_{21} p_{12}(z)}{\det \mathbf{P}(z)}$$

$$\approx \frac{\hat{m}_{11}}{p_{11}(z)} = \frac{\hat{m}_{11} z}{z^3 - a_{11} z^2 - \hat{l}_{111} z - \hat{l}_{211}}$$

(25)

As this transfer function is the third order, it has three poles in z-domain. The poles can be assigned by setting the parameters,  $\hat{l}_{1,11}$  and  $\hat{l}_{2,11}$ , but the sum of them is already determined as  $a_{11}$ , a function of the time constant of the system and current control period T.

The poles can be assigned from the continuous-time third-order prototype system optimized by integral of time multiplied absolute error (ITAE) criterion.

$$T_{ITAE}(s) = \frac{\omega_n^3}{s^3 + 1.75\omega_n^1 s^2 + 2.15\omega_n^2 s + \omega_n^3}$$

(26)

where  $\omega_n$  is undamped natural frequency.

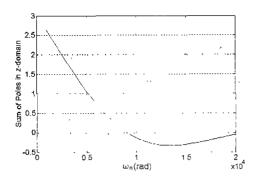

Due to the restriction on the sum of the poles in z-domain,  $\omega_n$  must be found to match the poles in s-domain of (26) to those in z-domain. Fig. 4 shows the curve of the sum of the poles according to  $\omega_n$ . From the system parameters shown in Table I,  $\omega_n$  can be set to 5.2e3 rad/sec.

Fig.4. Matching the Optimal Poles

Then the optimal poles of (26) is determined and therefore the matched poles in z-domain is determined using  $z = e^{sT}$ .

The parameters in (25) can be determined as

$$\hat{l}_{111} = \hat{l}_{122} = -(z_1 z_2 + z_2 z_3 + z_3 z_1) \tag{27}$$

$$\hat{l}_{211} = \hat{l}_{222} = z_1 z_2 z_3 \tag{28}$$

The diagonal terms in  $M_1$  can be obtained from the no steady-state error condition of (18).

In consequence, all entries of the gain matrices are determined from the no steady-state error and the decoupling conditions

#### V. SIMULATION AND EXPERIMENTAL RESULTS

To show the validity of the proposed controller for the 3\$\phi\$ VS PWM converter with a time delay, the simulation and experimental has been done. The system parameters are given in Table 1.

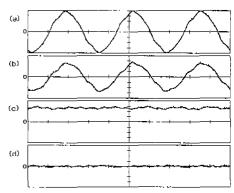

First, the simulated waveforms in the steady state for the predictive current controller designed in the synchronous reference are shown in Fig. 5. The input voltage and the input current are shown in Fig. 5(a). The input current is not sinousoidally controlled with a large amount of lowerorder harmonics. The direct and quadrature components of the input current in the synchronous reference frame are shown in Fig. 5(b). This unstability results mainly from the time delay. On the other hand, in case of the direct digital current controller, the input current is sinusoidally controlled without any steady-state errors. Fig. 6(a) shows that the input current is sinusoidally controlled with unit power factor. Fig. 6(b) shows that no steady state errors is produced in the input current in the synchronous reference frame. In the transient state, the direct digital current controller gives a good dynamic response as shown in Fig. 7. The load is changed abruptly from no load to 8.9kW.

TABLE I SYSTEM PARAMETERS

|   | 3131EW TARAWEI ERS               |            |     |

|---|----------------------------------|------------|-----|

|   | Parameters                       | Value      |     |

| • | Input Inductance                 | 1.2mH      |     |

|   | DC Link Capacitance              | 2300μF     |     |

|   | Input Voltage(Line-to-Line, rms) | 220V       |     |

|   | Load Resistance                  | $18\Omega$ |     |

|   | Current Control Period           | 200µsec    |     |

|   | DC Link Voltage Control Period   | 2msec      |     |

|   | DC Link Voltage                  | 400V       | - 3 |

Fig. 5. Simulation waveforms in steady state for the predictive current controller in the synchronous reference frame without consideration of SVPWM effects and a time delay. (10msec/div.)

(a) Input current(×3) and Input voltage (b) Direct and Quadrature components of the input current

Fig. 6. Simulation waveforms in steady state for the direct digital current controller. (10mscc/div.)

(a) Input current (×3) and Input voltage (b) Direct and Quadrature components of the input current (10msec/div.)

Fig. 7. Simulation waveforms in transient state from no load to 8.9kW for the direct digital current controller. (10mscc/div.)

(a) Input current (×3) and Input voltage (b) Direct and Quadrature components of the input current.

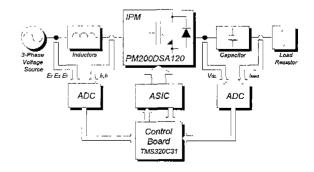

150 - Fig. 8. Schematic diagram of 3φ VS PWM converter

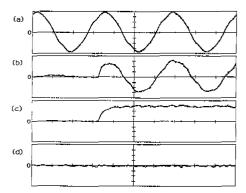

Fig. 8. shows a schematic diagram of 3φ VS PWM converter. The line-to-line voltage in the laboratory was 234V. Fig. 9 shows the waveform in the steady-state for the predictive current controller. Fig. 10 shows a the waveforms in the direct digital current controller. Fig. 11 shows the waveforms in the transient state for the direct digital current controller. All experimental waveforms are similar to simulation results.

Fig. 9. Experimental waveforms in steady state for the predictive current controller in the synchronous reference frame without consideration of SVPWM effects and a time delay. (5msec/div.)

(a) Input voltage(50V/div) (b) Input current(10A/div) (c) Direct components of the input current(10A/div) (d) Quadrature components of the input current(10A/div)

Fig. 10. Experimental waveforms in steady state for the direct digital current controller. (5msec/div.)

(a) Input voltage(50V/div) (b) Input current(10A/div) (c) Direct components of the input current(10A/div) (d) Quadrature components of the input current(10A/div)

# VI. CONCLUSION

In this paper, the current control for  $3\phi$  VS PWM converter with a time delay has been dealt. After investigating the pulsewidth-modulated signals, the new control model, hybrid reference frame model is proposed considering a time delay. From this continuous-time model, the discrete-time model can be easily obtained since the converter voltage and the input voltage are represented in the stationary and synchronous reference frames respectively. The gain matrices in the direct digital current controller are determined from the no steady-state error condition, decoupling control condition, and the matched poles in the z-domain from those in the s-domain which are satisfied to ITAE criterion. This current controller has a simple structure and its validity is proved

by the computer simulation and experimental results.

Fig. 11. Experimental waveforms in transient state from no load to 8.9kW for the direct digital current controller. (5msec/div.) (a) Input voltage(50V/div) (b) Input current(10A/div) (c) Direct components of the input current(10A/div) (d) Quadrature components of the input current(10A/div)

#### VII. REFERENCE

- [1] R. Wu, S. B. Dewan, and G. R. Slemon, "A PWM AC-to-DC Converter with Fixed Switching Frequency," *IEEE Trans. Industry Applications*, Vol. IA-26, No. 5, 1990, pp. 880 ~884.

- [2] T. G. Habetler, "A Space Vector-Based Rectifier Regulator for AC/DC/AC Converter," *IEEE Trans. Power Electronics*, Vol. 8, No. 1, 1993, pp. 30 ~36

- [3] O. Kurker, "Discrete-Time Current Control of Voltage-Fed Three-Phase PWM Inverters," *IEEE Trans. Power Electronics*, Vol. 11, No. 2, 1996, pp. 260 ~269

- [4] F. L. Lewis, Applied Optimal Control and Estimation, Prentice Hall Inc., 1992

- [5] M. P. Kazmierkowski and H. Tunia, Automatic Control of Converter-fed Drives, Elsevier, 1994

- [6] H.W.Broeck, H.-C. Skudelny, and G. V. Stanke, "Analysis and Realization of a Pulsewidth Modulator Based on Voltage Space Vectors," *IEEE Trans. Industry Applications*, Vol. IA-24, No. 1, 1988, pp. 142~150.

- [7] K. J. Astrom and B. Wittenmark, Computer-Controlled Systems 2/e, Prentice Hall Inc., 1990.