# DIGITAL CONTROL OF SINGLE PHASE BUCK-BOOST CONVERTER BY PULSE AREA MODULATION

T. J. Kim Y. B. Byun K. Y. Joe

Korea Electrotechnology Research Institute, P.O.BOX 20, Chang Won, 641-600, Korea Tel: +82-551-280-1412, FAX: +82-551-280-1406 E-mail: tjkim@keri.re.kr

#### C. U. Kim

Dept. of Electrical Engineering, Pusan Nat. Univ., Keumjeong-Ku, Pusan, 609-735, Korea Tel: +82-51-510-2368, FAX: +82-51-513-0212 E-mail: kimcu@hyowon.pusan.ac.kr

ABSTRACT - This paper is described a digital implementation of a pulse area modulation (PAM) method for a unity-power-factor buck-boost converter. A digital controller is designed and implemented by a Digital Signal Processor(DSP) to replace the analog control circuit for PAM. Experimental results are presented and compared with simulations.

#### 1. INTRODUCTION

The recent advance in Digital Signal Processor (DSP) technology has given better possibilities and advantages for using digital means in control of power converter. DSP digital controllers permit one to realize high speed high performance control, parallel operation, self-diagnose function and flexible control algorithms. Despite of the increasing number of application in 3 phase inverter system control such as Space-Vector PWM control scheme, relatively few DSP digital controllers have been built for PWM DC-DC converter<sup>(1</sup>H<sup>(2)</sup>.

In this paper, the design of DSP (TMS320C32-50) based controller for DC-DC converter is presented. Simulation and Experiment results of 1kW 20kHz single phase unity Power Factor Collection (PFC) buck-boost converter prototype by Pulse-Area-Modulation (PAM)<sup>[3]-[4]</sup> control scheme built on a DSP, but the controller is also applicable to the single phase full bridge converter.

# 2. DSP based controller for single phase PWM DC-DC converter.

The T.I. TMS320C32-50 is versatile 32-bit high

performance CMOS floating point processor cable of 50MFLOPS and 275MOPS with a 40nS single cycle instruction execution time. A board, whose size is 218.4× 157.5mm is single. The board consist of A/D D/A converter, hardware protect signal, input-output signal isolated with photo coupler, interfacing with peripheral device, Electrical Programmable Logic Device (EPLD) which has reset, decoder boot-loader address interrupt controller. The DSP controller hardware configuration is as shown Table 1.

Talble 1 DSP controller hardware configuration

|                            | DSP Pa                                          | rt                      |                   |            |  |

|----------------------------|-------------------------------------------------|-------------------------|-------------------|------------|--|

| DSP                        | TMS320C32-50<br>50MHz, 50MFLOPS<br>275MOPS      |                         |                   | IEA        |  |

| MEMORY                     | SRAM(KM68257)<br>EPROM(27CO20)                  | 32K× 8bit<br>256K× 8bit | 15nsec<br>150nsec | 4EA<br>1EA |  |

| EPLD                       | EPM7160LC84<br>EPM7032LC44                      |                         | 12nsec<br>12nsec  | 1EA<br>1EA |  |

| Analog I/O Interface Part  |                                                 |                         |                   |            |  |

| Analog<br>Input 4ch        | A/D<br>Converter(MAX120)<br>Multiplexer(ADG529) | 12bit                   | 1.6µ sec          | 1EA<br>1EA |  |

| Analog<br>Output 4ch       | D/A Converter(AD664)                            | 12bit                   | 4ch               | lEA        |  |

| Digital I/O Interface Part |                                                 |                         |                   |            |  |

| Optic Input                | HFBR-1521                                       | 5MBd                    |                   | 4EA        |  |

| OpticOutput                | HFBR-2521                                       | 5MBd                    |                   | 8EA        |  |

| Digital<br>In/Out          |                                                 |                         |                   | 6EA        |  |

| R\$485<br>R\$232           | AM85C30<br>MAX 211                              |                         |                   | 1EA<br>1EA |  |

# 3. DIGITAL CONTROL OF SINGLE PHASE BUCK-BOOST CONVERTER BY PULSE AREA MODULATION

# 3.1 Single phase unity PFC buck-boost converter

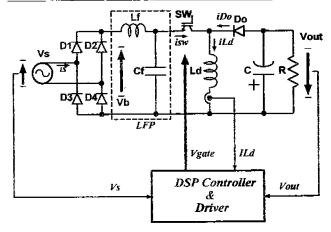

Fig. 1 A power circuits of the PFC buck-boost converter

Fig. 1 shows the power circuits of the single phase unity PFC buck-boost converter. The AC line input voltage  $v_s$  is rectified to a DC voltage by a diode bridge and low pass filter  $(L_{f}, C_{f})$ . The DC voltage is then applied to a buck-boost converter, which constitutes of inductor  $L_{tb}$  switch SW, diode  $D_o$  and Capacitor C. The output voltage  $v_o$  can be controlled less than or higher the peak value of the input voltage  $v_s$  with duty ratio.

If the inductance L is very large and the inductor current  $i_{ld}$  has no ripples, that is, a very large inductance is required to avoid modulation errors caused by ripples of the inductor current in traditional PWM control scheme buck-boost converter. In case of small inductance L which caused inductor current  $i_{ld}$  to have ripples, the buck-boost converter by replacing traditional PWM control scheme to PAM control scheme, is controlled to avoid the modulation errors.

The PAM converter regulates input instantaneous current is to its reference value in proportionate to sinusoidal input voltage  $v_s$ . The next describes PAM control scheme digital controller for a unity PFC DC-DC converter.

## 3.2 Pulse Area Modulation Control [4]

Fig. 2 show a principles of PAM control scheme. Carrier signal  $i_{cor}$  can be determined by integrating the inductor current  $i_{Ld}$  in each switching period. We obtain

Fig. 2 A principles of PAM control scheme

$$i_{cur} = \int_{t_{l}}^{t} i_{Ld} dt \tag{1}$$

Thus, carrier signal  $i_{cor}$  is a modulated sawtooth function, whose amplitude is determined in proportion to inductor current  $i_{td}$ . And we can write a pulse area reference  $i^*_{core}$  is as follows;

$$i^*_{area} = i^*_{s} \cdot T_{sw} \tag{2}$$

where  $i_s^*$  is a current reference, whose absolute value is in proportion to input voltage  $v_s$ .  $T_{sw}$  is switching period.

Switching turn-off time  $t_k$  is determined by carrier signal  $i_{cor}$  and pulse area reference  $i_{cor}$  in a each period, current  $i_{sw}$  is equal to inductor current  $i_{Ld}$  in the turn-on switching time. Thus, we obtain

$$i_{area} = \int_{t_k}^{t_{k+1}} i_{sw} dt = \int_{t_k}^{t_k} i_{Ld} dt = i^*_{area}$$

(3)

#### 3.3 Simulation

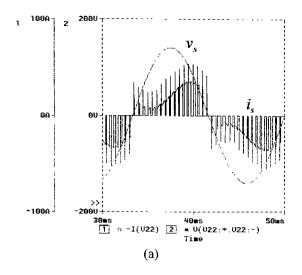

Fig. 3(a) shows input voltage  $v_s$  and input current  $i_s$  in case of traditional PWM control scheme. Fig. 3(b) shows in case of PAM control scheme.

In fig. 3(a), regardless of instantaneous magnitude of input current  $i_s$ , the pulse width in each modulation periods of current is proportional to input voltage  $v_s$ .

But, in fig 3(b), a pulse area in each modulation period of current, is proportional to input voltage  $v_s$ . A pulse width is determined by magnitude of input current. When inductor current  $i_{Ld}$  is very small about zerocrossing in case of PAM control scheme, it can appear overmodulation, which cause modulation errors.

Fig. 3 Simulation results (Input voltage and current)

- (a) Traditional PWM control scheme

- (b) PAM control scheme

# 4. DIGITAL CONTROL ALGORITHMS

Let assume that inductor current  $i_{Ld}$  is constant in sampling period. From equation (3), we obtain

$$i^*_{sw} \cdot T_{somp} = i_L \cdot T_{ii} \tag{4}$$

where  $i_{sn}^*$  is PI controlled output.  $T_{samp}$  is sampling period.  $T_{ii}$  is turn-on switching time. From equation (4), we can write the turn-on switching time  $T_{ii}$  as

$$T_{ii} = \frac{i^*_{sw} \cdot T_{samp}}{i_L} \tag{5}$$

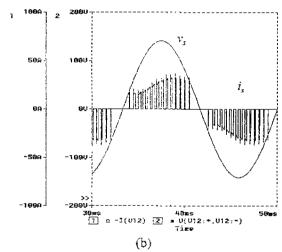

Fig. 4 PAM Control scheme( $v_o = 110V$ , 5ms/div)

- (a) Input voltage  $v_s$  and current  $i_s$  (200V/div, 5A/div)

- (b) Inductor current  $i_{Ld}$  and Inductor current  $i_s$  (20A/div)

- (c) Output voltage (50V/div)

Fig. 5 PAM Control scheme  $(v_a = 150\text{V}, 200\text{V/div}, 5\text{A/div}, 5\text{ms/div})$

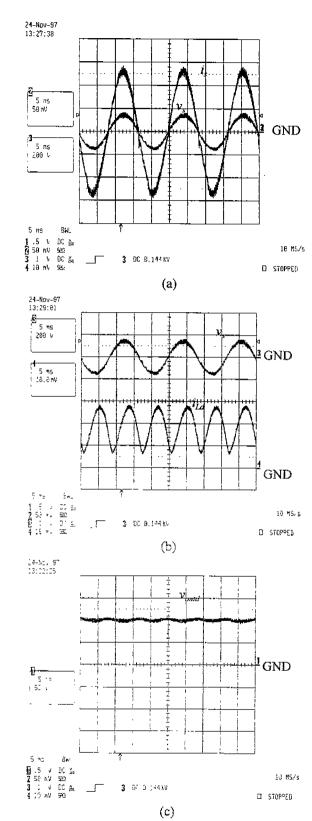

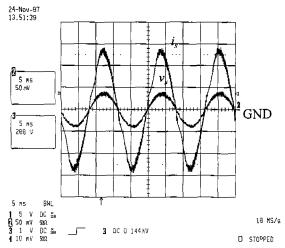

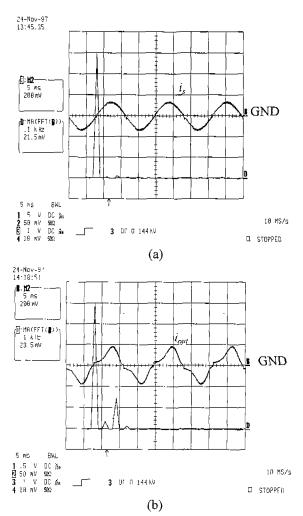

Fig. 6 Input current *i*, and its FFT (20A/div, 100Hz/div, 5ms/div)

- (a) Traditional PWM Control scheme.

- (b) PAM Control scheme.

### 5. EXPERIMENTAL RESULTS

The operating conditions and circuits are as shown Table 2. Fig. 4 shows input voltage  $v_s$ , current  $i_{l,d}$  and output voltage  $v_o$ . Fig. 5 shows in case of output voltage is 150V.

Fig. 6(a)(b) shows input current  $i_s$  and its spectrum analyzer in cases of traditional PWM and PAM control scheme respectively. In Fig. 6(a), it appears that the low order harmonics, which cause the distortions seriously, are effectively suppressed. In fig.6(b), Specially 3th harmonics factor measured by the FFT analyzer is about 27%, but is 2.5% which is reduced to one-tenths in Fig. 6(a).

#### 6. CONCLUSION

In this paper, we obtain simple digital control algorithms for single phase unity PFC buck-boost converter by PAM scheme. Experimental results, matching the simulation results have already proved control scheme. The DSP employed in the prototype is relatively inexpensive yet powerful. But with the decreasing cost of DSP and implementing more complex algorithms, digital controlled power converters appear well suited.

Table 2 Main parameter of buck-boost converter

| Inductor $L_d$                  | 7mH(60Hz)  |  |

|---------------------------------|------------|--|

| Filter Inductor $L_f$           | 300uH      |  |

| Filter Capacitor C <sub>f</sub> | 4.7uF      |  |

| Capacitor C                     | 4700uF     |  |

| Switching Freq. F               | 20kHz      |  |

| Input Voltage $V_s$             | 110V, 60Hz |  |

| Output Power P <sub>o</sub>     | 1kW        |  |

### 7. REFERENCES

- [1] A.H.Mitwalli, S.B.Leeb, G.C.Verghese, "An Adaptive digital controller for unity power factor converter," IEEE Trans Power Electron, vol.11 no.2 Mar.1996.

- [2] N.Mohan, S.S.Ang, "A digital signal processor based Controller for a switching converter" Int. J. Electronics, vol77,no.5, 1994

- [3] S.Motegi, A.Maeda, "A Sinlge-phase Buck-Boost PFC Converter with Output Voltage-Ripple-Reducing Operation", T.IEE Japan, Vol 117-D, No.7, 1997

- [4] K.Hirachi, Y.Nishida, K.G.D.Laknath, M.NakaokaA New Buck-Type Controlled AC-DC Converter with Input Current Harmonics Compensated Output Voltage Ripple Active Filtering Scheme", PEMC, P1/232-1/238,1997