# **Analog Adaptive Pulse shaping and Line Equalizer**

# For 400Mb/s data rate on 50m STP Cable

Hoon Lee, Kwisung Yoo and Gunhee Han

Department of Electrical and Electronic Engineering Yonsei University,

134, Shinchon-dong Seodaemoon-gu, Seoul, Korea

E-mail: lhoon@cad.yonsei.ac.kr

## **ABSTRACT**

High Speed data transmission over a long length of cable is limited due to the limited bandwidth of a cable which introduces ISI(Inter Symbol Interference). In order to compensate for the loss and phase dispersion in the cable, a pulse shaping in a transmitter and a line equalizer in receiver can be used. This paper presents a low-power and small-area analog adaptive pulse shaping circuit and line equalizer. The design was fabricated in a 0.25 m inxedsignal CMOS process. The proposed pulse shaping circuit and equalizer operate at 400Mb/s on 50m STP(Shielded Twisted Pair) cable. It consumes 28.5 m with a 2.5-V power supply and occupies only 0.098 mm.

# I. INTRODUCTION

In wired high speed serial data communication, the major limiting factor of performance is the limited cable bandwidth that is inversely proportional to the square of the cable length [1]. This frequency-dependent attenuation causes significant ISI and eventually results in a poor eye-opening with high BER(Bit Error Rate). The measured 9-MHz channel bandwidth is roughly a factor of forty-five less than the bandwidth required to obtain a reasonable eye opening for a 400Mbps system with square pulses, so special filtering techniques are required.

Either signal equalization at the receiver side or pulse shaping at the transmitter side is required to compensate ISI. Equalization in the receiver can be implemented with either digital or analog circuit. In digital equalization method, ADC(Analog Digital Converter), which is just after analog front end and typically 7 or 8 bit, consumes high power and occupies large silicon area [2]. In analog implementation, OPAMP-based circuit commonly used. However, OPAMP-based circuit is consumes high power especially when the high speed operation is required [3].

In the transmitter side FIR-type pulse shaping filter is commonly used for ISI compensation. Although the hardware complexity of a FIR-type pulse shaping is less than an equalizer, it is impossible to find the optimal pulse shape for unknown cable length [2]. So this paper proposes an adaptive analog pulse shaping and line equalization scheme for master-slave system configuration.

Section II provides the architecture and adaptation method. Section III and IV discuss detailed circuit implementation and simulation results of proposed circuit, respectively. Finally, conclusion is provided in section V.

# II. ADAPTIVE PULSE SHAPING AND EQUALIZER ARCHITECTURE

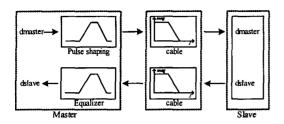

Fig. 1 shows the proposed concept of an adaptive analog pulse shaping and the line equalizer and fig. 2 shows its block diagram

Figure 1. The proposed concept

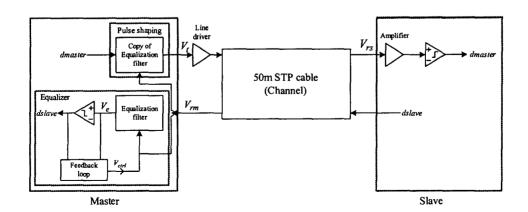

The equalizer in master stage can obtain the control signal,  $V_{ctrl}$ , according to the cable length by the feedback loop. The equalization filter compensate ISI in  $V_{rm}$  and the generate equalized signal  $V_e$ . The data (dslave) that the slave sent is recovered from  $V_e$  with comparator. The proposed pulse shaping is realized with a copy of the equalization filter. Therefore the pulse shaping filter is adjusted for the cable length in use. There is no need for slave stage to have equalizer if the characteristic of the equalizer and the pulse shaping is the very same. So the slave stage can be made very simply without equalizer, which consists of a simple amplifier and a comparator.

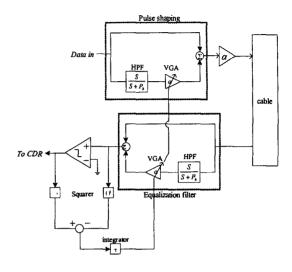

Fig. 3 shows the block diagram of the proposed adaptive analog line equalizer[3] and pulse shaping. The optimal VGA gain,  $A_{opt}$ , is obtained by comparing the signal power of the comparator's input against that of its output. Differently from existing FIR-filter based pulse shaping, the proposed circuit can make proper pulse shape according to cable length by using  $A_{opt}$  which can be

obtained from an adaptive equalizer. The output of the pulse shaping filter is transmitted through the line driver

Figure 3. Proposed Block diagram of total architecture

## III. CIRCUIT IMPLEMENTATION

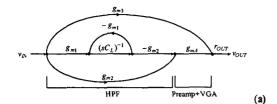

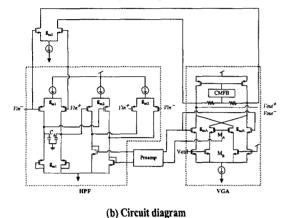

Fig. 4 shows the signal flow graph and circuit diagram of the filter used for the equalizer and pulse shaping. The filter is implemented with Gm-C circuit. The preamplifier is provided to obtain high VGA gain to operating at high frequency.

Figure 2. Proposed concept of adaptive pulse shaping and equalizer

## 2003년도 대한전자공학회 하계종합학술대회 논문집 제26권 제1호

Signal flow graph

Figure 4. Signal flow graph and circuit diagram.

The transfer function of this filter is as follow.

$$H(s) = \left(g_{m2} \cdot \frac{sC_L}{g_{m1} + sC_L} \cdot g_{mA} + g_{m3}\right) \cdot r_{out} \tag{1}$$

The first fixed pole of this filter is located at  $g_{ml}/C_L$ . This first pole should be located at higher frequency than 280Mhz which is 70% of the transmitted data rate [5]. Another fixed pole is located at the output node by VGA output node.

One adjustable zero of the equalizer is determined by the VGA gain as reported in [3].

## IV. SIMULATION RESULTS

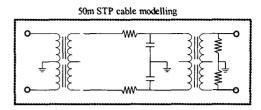

The designed analog adaptive pulse shaping and line equalizer is simulated with 400Mbps pseudo random data signal on cable having 9Mhz bandwidth (50m STP cable). A twisted-pair cable and the transformer is modeled as 1<sup>st</sup> order low-pass filter whose 3dB frequency located at around 9Mhz as shown in Figure 5.

Figure 5. Channel modeling.

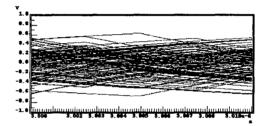

The proposed circuit including the channel model is simulated with PRBS data

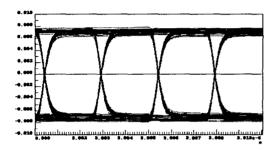

(a) The eye diagram of the output of 50m STP cable ( $V_{rn}$ )

(b) The eye diagram of the equalizer output (  $V_e$  )

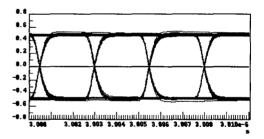

Figure 6. Simulation results of the equalizer.

Fig. 5 shows the simulated eye diagram of the signals from the slave to the master. The received signal through the 50m cable,  $V_{rm}$  is degraded with severe ISI and does not show any eye opening. After equalization,  $V_e$ , the eye is completely open with plenty margin which is sufficient to detect source signal with no distortion.

#### 2003년도 대한전자공학회 하계종합학술대회 논문집 제26권 제1호

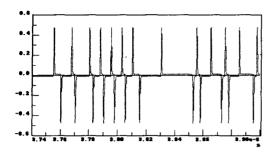

# (a) The output of the pulse shaping filter ( $V_t$ )

(b) The eye diagram of the output of 50m STP cable (  $V_{rs}$  )

Figure 7. Simulation results of the pulse shaping

Fig 6. shows the simulated waveform the data transmission from the master to the slave. The output waveform of the pulse shaping filter,  $V_t$ , is shown in Fig. 6 (a). The output at the end of a 50m STP cable,  $V_{rs}$ , in Fig. 6 (b). As the figure shows, the output of pulse shaping filter is properly pre-shaped according to  $V_{ctrl}$ , and the output signal through 50m STP cable shows the proper eye opening.

# V. CONCLUSION

This paper proposes a low power and small area analog adaptive pulse shaping and line equalizer for 400Mbps data rate on 50m STP cable. The STP cable should be used due to the high frequency radiation by the pulse shaping. It consumes significantly low power (28.5 mW) with a 2.5-V power supply and occupies very small area (0.098 mm²) using 0.25 µm CMOS process. This proposed circuit is under fabrication.

## REFERENCE

- [1] D.A. Johns and D. Essig, "Integrated circuits for data transmission over twisted-pair channels," *IEEE Journal of Solid-State Circuits*, Vol.32, No. 3, pp. 398-406, March 1997

- [2] David J. Foley and Michel P.Flynn, "A Low-power 8-PAM Serial-Transceiver in 0.5um digital CMOS", IEEE 2001 Custom Integrated Circuits Conference, 2001

- [3] Babanezhad J. N. "A 3.3V Analog Adaptive Line-Equalizer for Fast Ethernet Data Communication," in Proc. 1998 IEEE Custom Integrated Circuits Conference, pp 343-346, 1998

- [4] Kwisung Yoo, Hoon Lee, Gunhee Han. "A low power CMOS adaptive line equalizer for fast Ethernet" IEEE Asia-Pacific Conference on 2002. Page(s): 129 -132

- [5] Jafar Savoj, Behzad Razavi, High-Speed CMOS Circuits for Optical Receivers, 1st edition: Kluwer Academic, 2001