# Advanced P-Channel Poly-Si TFTs for SOG

# Seong Jin Park, Sang Hoon Kang, Yu Mi Ku, Jong Hyun Choi, and Jin Jang

Advanced Display Research Center, Kyung Hee University, Seoul 130-701, KOREA Email: jjang@khu.ac.kr

## **Abstract**

High performance p-ch poly-Si TFTs with excellent stability were developed. By using a frequency doubled DPSS CW laser, the a-Si on glass could be crystallized into one dimensional single crystalline silicon named as a sequential lateral crystallization (SLC) region. We fabricated p-ch TFTs on SLC region and the typical characteristic values of the TFTs were  $u_{fe} = 180 \text{ cm}^2/\text{Vs}$ ,  $V_{th} = -3 \text{ V}$ , S.S. = 0.5 V/dec, and  $I_{off} = 1 \text{ pA/um@V_d} = -10 \text{ V}$ . It is found that the TFTs are very stable after bias stresses such as negative and positive gate biases, hot carrier bias and high current bias. These results indicate that the poly-Si in SLC region is suitable for system on glass (SOG) application.

#### 1. Introduction

The demands for compact, light-weight and high-resolution displays are getting stronger in the mobile application fields. However it is difficult to fulfill these demands by using a conventional amorphous silicon (a-Si) technology because of the difficulties in driving circuit integration and the large size of TFTs. In this point of view, a low-temperature polycrystalline silicon (LTPS) technology has some advantages compared to the a-Si technology. Among the various crystallization techniques, excimer laser annealed (ELA) poly-Si has been spotlighted as a candidate for a promising method however this technique has still issues about mass production such as process instability, high cost and difficult maintenance. Meanwhile, system integration on glass is gaining attractions more and more for next generation information display. It is clear that TFTs for SOG should require better electrical characteristics than those for current AM devices and be more stable like SOI devices.

Recently, Hara et al. reported very impressive results on a new approach to make high-quality LTPS, called a CW laser crystallization (CLC).[1] According to their results, the CLC has many advantages such as simplicity, low-cost process and maintenance besides its electrical performances. However, the CLC poly-Si shows various microstructures from very small grains with average size of several tens of nanometers to directionally crystallized super large grains over 10 um-so called, sequential lateral crystallized (SLC) region. This phenomenon appeared regardless of the crystallization process conditions such as a laser power and a scanning speed.[2] Needless to say, SLC region shows a very good electrical performance among the microstructures.[2]

The objectives of this work are to verify the characteristics of the SLC poly-Si TFTs under various electrical bias stresses, and to give the possibilities of this novel technique as another candidate for mass production of a LTPS TFT-OLED

# 2. Results and Discussion

## 2.1 SLC poly-Si TFTs

A silicon oxide (SiO<sub>2</sub>) layer of 400 nm was deposited on a glass (Corning 1737) prior to the deposition of an amorphous silicon (a-Si) layer. The thickness of the a-Si was 150 nm. We used plasma enhanced chemical vapor deposition (PECVD) method to deposit SiO<sub>2</sub> and a-Si layers. Dehydrogenation of the a-Si was done by a furnace annealing at 480 °C for 5 hrs. After these processes, we irradiated a CW laser to the samples on the 2-D translation stage with X-Y scanning.

A  $2\omega$  CW DPSS (diode pumped solid state) laser with the wavelength of 532 nm was used to crystallize the samples. Laser beam size onto the a-Si surface was 20 um (short axis, scan direction)  $\times$  800 um (long axis, transverse direction to scan direction), and the beam shape is Gaussian with short axis, top-hat with long axis. Output power and scanning speed of the laser were 10 W and 20 cm/s, respectively.

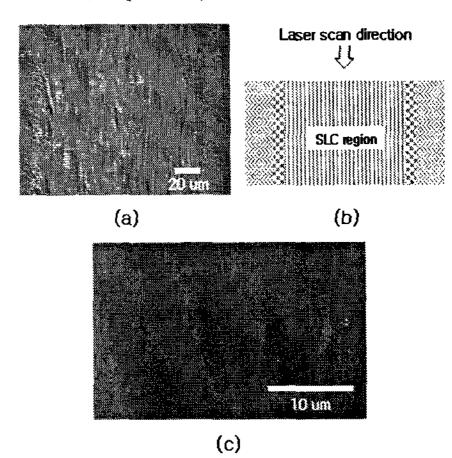

Figure 1. An optical microscope image of crystallized region after a CW laser scanning (a) and its schematic representation with sequential lateral crystallized (SLC) region (b). A SEM image shows SLC region (c).

Figure 1 shows a typical Nomarski optical microscope image of the crystallized region after a CW laser scanning (a) and its schematic representation with sequential lateral crystallized (SLC) region (b). Even though only a single scanning, the total width of crystallized region is over 500 um and especially the SLC region, reaches almost 130 um. In general, the microstructure of CLC poly-Si is appeared like Fig. 1 (b) with different size of grains.[1,

2] The grains are getting smaller from the SLC region to the outer regions. Note that the frozen stream-like region at the center (SLC region) is composed of large, especially very long (over 10 um) elongated grains along the laser scan direction as shown in a SEM image of Fig. 1 (c).

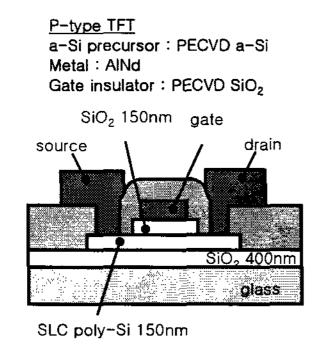

Figure 2. The cross-sectional schematic diagram of a SLC poly-Si TFT.

The p-channel poly-Si TFT with a coplanar structure was fabricated by using a SLC region as an active layer.(see Fig. 2) The fabrication process is described in the literature.[2]

# 2.2 Stability against Various Bias Stresses

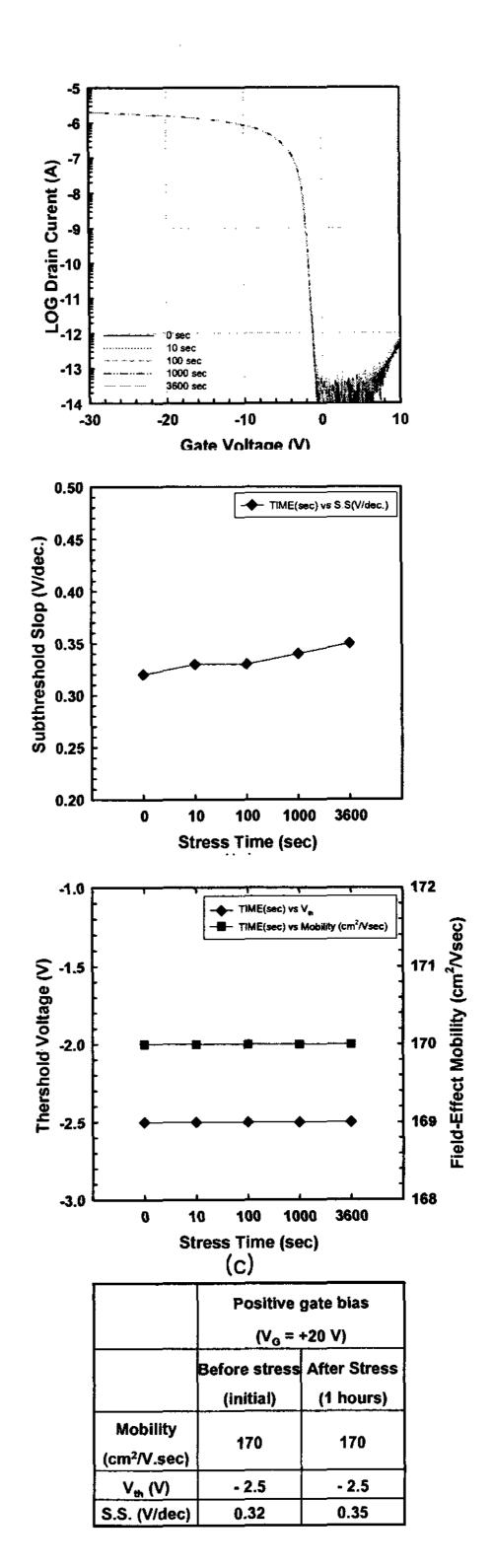

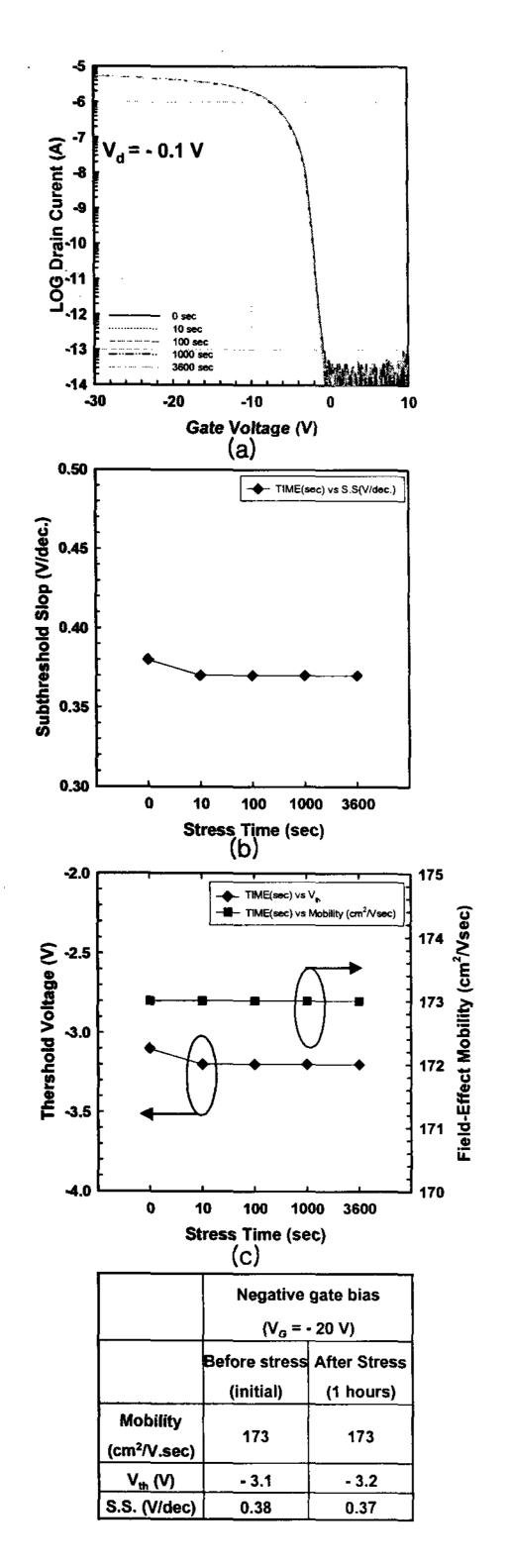

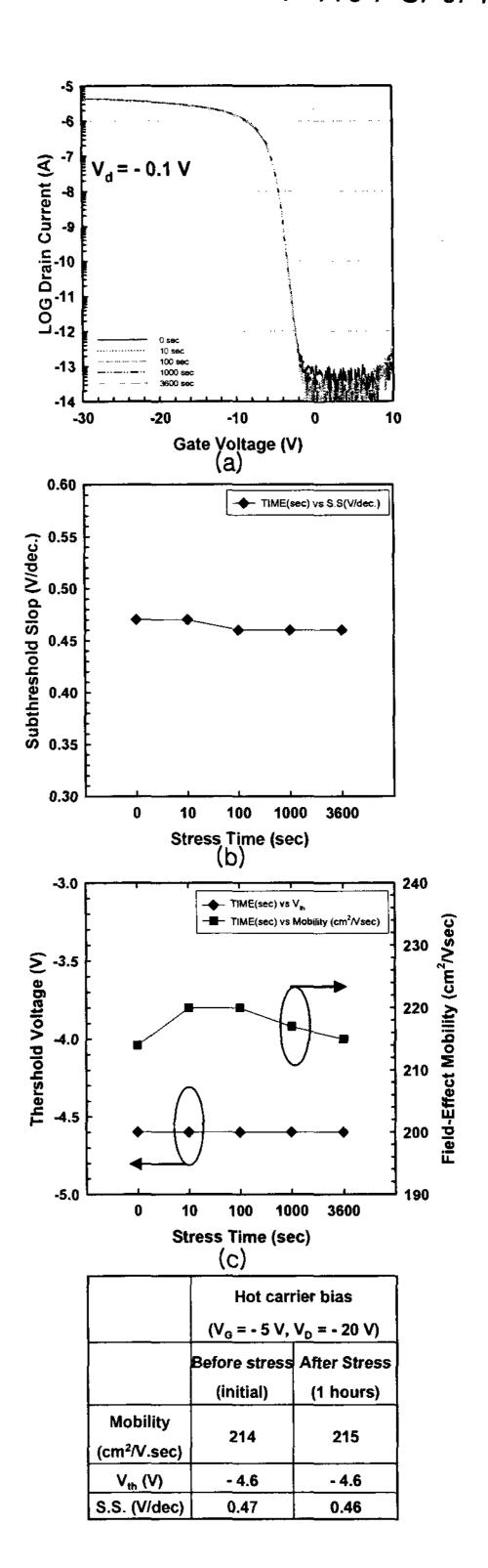

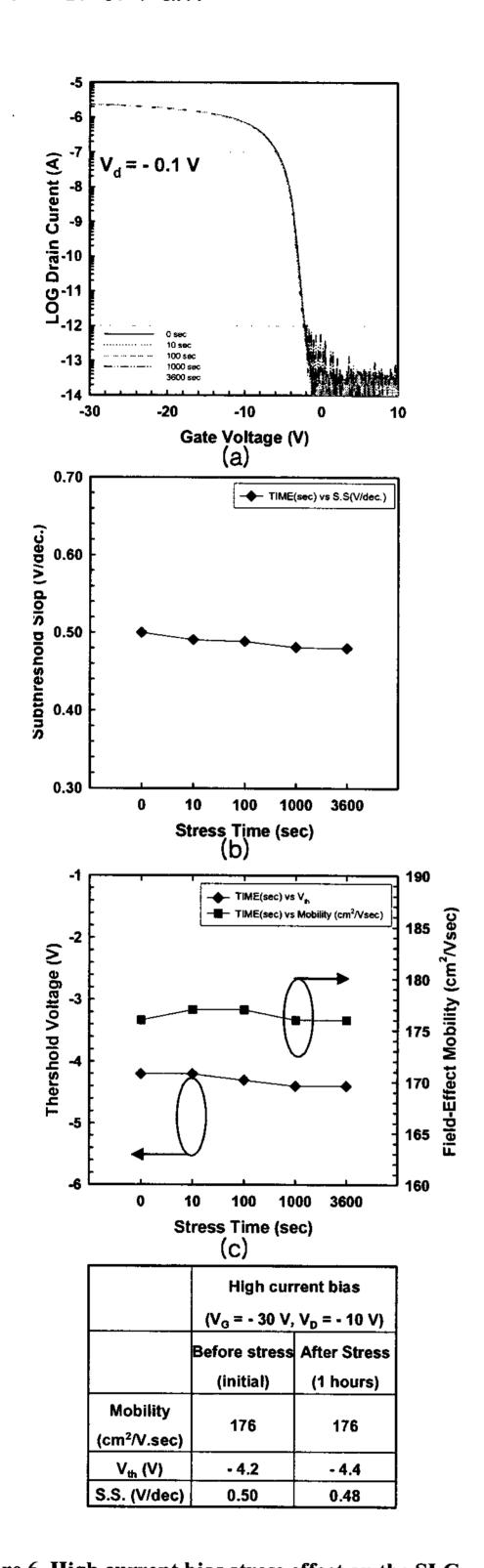

In this section, we describe the results of the electrical bias stress effect on the characteristic variation in p-type SLC poly-Si TFTs. We examined the characteristic changes of the TFTs under 4 different electrical bias stresses as a function of stress time; negative and positive gate biases, hot carrier bias, high current bias, respectively. In Figures 3 through 6, the results were described with the transfer characteristics variation (a), the subthreshold slope change (b), and the threshold voltage and the field effect mobility change (c) during bias stresses. The characteristic values such as mobility, threshold voltage and subthreshold slope, before and after bias stresses, were summarized in each figure with a table. Before we give an explanation of our results, we note that we do not carry out the attempts to enhance the electrical performances of SLC poly-Si TFTs, such as surface treatments by plasma and /or hydrogenation after TFT fabrication.

Generally, the poly-Si TFTs suffer from the gate bias stress because the weak-bonds at grain boundaries are easily broken during the stress and they generate enormous states result in obstructing carrier currents.[3] However, in Figures 3 and 4, the electrical characteristics (subthreshold slope as well as threshold voltage) of the SLC poly-Si TFTs do not change during the positive or negative stresses. This means that there are little weak-bonds, to increase deep states by being broken, in the SLC poly-Si. In addition, it can be considered that the SLC poly-Si matches well with the PECVD SiO<sub>2</sub>. This is, of course, very important factor for mass productions and this can be one of the merits of the SLC poly-Si film.

It is well known that the poly-Si TFTs under hot carrier bias stress show some degradation in mobility, threshold voltage and subthreshold slope. All the reason of this degradation has responsible for the creation of acceptor-like interface states and of mid-gap states by the severe collision of hot carrier near the drain. [4] The results of Fig. 5 show that the SLC poly-Si TFT is very stable under hot carrier bias.

Figure 3. Positive gate bias stress effect on the SLC poly-Si TFT(W/L=8/8); transfer characteristics (a), sub threshold slope variation (b), threshold voltage and field effect mobility variation (c). The characteristic parameters are summarized in the table before and after stress

Figure 4. Negative gate bias stress effect on the SLC poly-Si TFT (W/L=8/8); transfer characteristics (a), sub threshold slope variation (b), threshold voltage and field effect mobility variation (c). The characteristic parameters are summarized in the table before and after stress

Figure 5. Hot carrier bias stress effect on the SLC poly-Si TFT (W/L=8/8); transfer characteristics (a), sub threshold slope variation (b), threshold voltage and field effect mobility variation (c). The characteristic parameters are summarized in the table before and after stress.

Figure 6. High current bias stress effect on the SLC poly-Si TFT(W/L=8/8); transfer characteristics (a), sub threshold slope variation (b), threshold voltage and field effect mobility variation (c). The characteristic parameters are summarized in the table before and after stress

These excellent stabilities under gate bias and hot carrier bias stresses might be due to the crystalliniy of the SLC poly-Si layer in the channel. As shown in Fig. 1 (c), the probability of grainboundary penetration of carriers is reduced when the channel is parallel to the scan direction like this works. Indeed, the rms roughness of SLC poly-Si films is a half of that of conventional ELC poly-Si films. Considering the size of the TFT (W/L=8/8), there are few grain boundaries in the channel, if any a few grain boundaries in it. Therefore the electrical characteristics are not affected by the bias stresses. While, different from above results, the SLC poly-Si TFT under high current bias stress shows some changes during the stress. The transfer curve shows slight parallel shift toward negative gate voltage direction, which results in subthreshold voltage shift from -4.2 to -4.4 V. According to Maeda et al., this parallel shift of transfer curve is due to the breaking of Si-H bonds at the poly-Si/SiO<sub>2</sub> interface so that hole traps at these sites.[5] This explanation can be applied to our case because we used PECVD SiO<sub>2</sub> with SiH<sub>4</sub> gas and the maximum process temperature was not exceed 360 °C so that SiO<sub>2</sub> includes some hydrogen.

Although the reason why the SLC poly-Si TFTs are so stable against various bias stresses should be studied more, the experimental results of bias stress effects on the SLC poly-Si TFT indicate that the SLC poly-Si TFTs are enough to be adopted for switching and driving devices for AM-OLEDs and SOG.

## 3 Conclusion

We fabricated the p-type SLC poly-Si TFTs by using a CW laser scanning. The various bias stress effects on the electrical characteristics of the SLC poly-Si TFTs as a function of stress time were reported for the first time. The results showed that the SLC poly-Si TFTs are very stable under positive/negative gate bias stresses and hot carrier bias stress. This is due to the good crystallinity of the SLC poly-Si films. Under high current bias stress, the transfer curve slightly shifted to negative gate voltage. This may result from the H in SiO<sub>2</sub> film. Considering the excellent electrical characteristics of the SLC poly-Si TFTs as well as the stability under various bias stresses, the SLC poly-Si TFTs can be applied for SOG.

# 4. Acknowledgements

This work was supported in part by Ministry of Commerce, Industry and Energy of Korea under project 00014755

# 5. References

- [1] A. Hara, F. Tkeuchi, M. Takei, K. Yoshino, K. Suga and N. Sasaki, AM-LCD'01 Digest, 227 (2001) / F. Takeuchi, A. Hara and N. Sasaki, Proc. of IDMC'02, 73 (2002)

- [2] S. J. Park, S. H. Kang, Y. M. Ku and J. Jang, 2004 MRS Spring Meeting, A3.3/I2.3 (San Francisco, US, 2004) / S. J. Park, S. H. Kang, Y. M. Ku and J. Jang, to be published in EPJ-AP, 2004.

- [3] M. Hack, A. G. Lewis and I. W. Wu, IEEE Trans. Elec. Dev. 40, 890 (1993) / N. D. Young and J. R. Aryes, IEEE Trans. Elec. Dev. 42, 1623 (1995)

- [4] N. D. Young, IEEE Trans. Elec. Dev. 43, 450 (1996)

- [5] S. Maeda, S. Maegawa, T. Lapposi, H. Nishihara, T. Lchiki, J. Misuhashi, M. Ashida, T. Muragishi, Y. Inoue and T. Nishihara, J. Appl. Phys. 76, 8160 (1994)