# Recent Progress in Organic Thin Film Transistor on the Plastic Substrates

Kyung Soo Suh, Seung-Youl Kang, Seong Deok Ahn, Ji Young Oh, In Kyu You, Gi Hyun Kim, Kyu Ha Baek, Chul Am Kim, Chi-Sun Hwang, Sang-Hee Ko Park, Yong Suk Yang, Sung Mook Chung, Jeong-Ik Lee, Lee-Mi Do, Hye Yong Chu, and Kwang Yong Kang

## Electronics and Telecommunications Research Institute Basic Research Lab., 161, Gajeong-dong, Yuseong-gu, Daejeon, 305-350, Korea

#### **Abstract**

Pentacene based OTFT on PC and PES plastic substrates have been fabricated in a scale of 5 inches. We could get a small OTFT device enough to be applicable for AMOLED by acquiring the at least misalignment margin through a contact aligner. And also we could find out the degradation of device parameter through the integration processes and improve the properties by using a buffer layer as an etch stopper in an active patterning. Through these, the mobility of device is more than about  $0.2 \text{cm}^2/\text{Vs}$  and  $I_{\text{onf}}/I_{\text{off}}$  is higher than  $10^5$ .

### 1. Introduction

Many researchers have tried to fabricate an OTFT for high performance on the plastic substrates. [1-3] But most of all have been manufactured and performed through a kind of simple patterning processes using shadow masks. Devices through these processes might have some problems in case of considering a large scale application like as AMOLED. Among them, process using shadow mask will not guarantee the fine patterning. And also we will not be able to deal with the actual degradation of parameters of device in the integration of OTFT. Therefore these problems will not permit us to access the genuineness of OTFT as an IC application. So we have fabricated an OTFT by using the compatible process with semiconductor process like as lithography using contact aligner, wet process, dry etching, and high vacuum deposition. We have found out that what major effects have made on an OTFT in integration.

### 2. Experimental details

The OTFT arrays with 88x64 pixels have been fabricated by using PC-OVD (pressure control - organic vapor deposition) for pentacene film. The device structure is an inverted coplanar bottom contact type. Cr/Al/Cr triple layers are adapted as a gate metal and J1 is used as a gate insulator. Ti/Au double layer

is used as a source/drain electrode material. The thickness ratio of Ti/Au is optimized. And a high speed lift-off method is used for source/drain patterning. Thermal and chemical treatment is made on a gate dielectric surface before pentacene deposition. Buffer layer is deposited on a gate dielectric as an etch stopper. Pentacene film is deposited by PC-OVD method, which is applicable in large scale processing. The channel width and length of device is  $1,000/100~\mu m$ , respectively. We have developed the process for AMOLED application. Parylene and AlO are used as a passivation layer.

### 3. Results and discussion

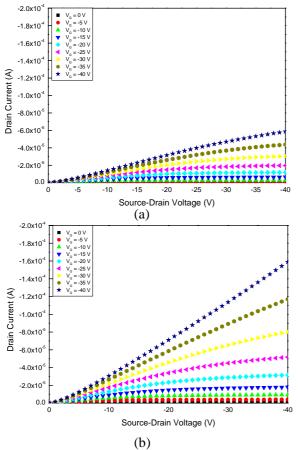

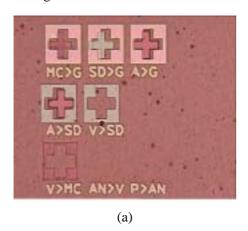

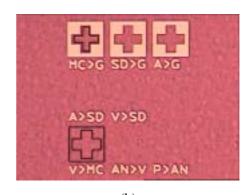

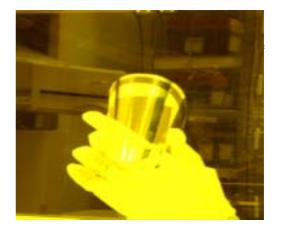

The effects of the measurement of OTFT in each process step are investigated on PES and PC substrate. The measurement parameter is mobility, I<sub>on</sub>/ I <sub>off</sub>, and  $V_{th}$  (threshold voltage). Figure 1 shows the transfer characteristics of OTFT device fabricated on PES (a) and PC(b) substrates at various gate voltages. The mobility,  $I_{op}/I_{off}$ , and  $V_{th}$  of OTFT on PES is 0.08  $cm^2/Vs$ ,  $10^3$ , and 7 V. The mobility,  $I_{on}/I_{off}$ , and  $V_{th}$  of OTFT on PC substrate is 0.24 cm<sup>2</sup>/Vs, 10<sup>4</sup>, and 11V. Figure 2 shows the misalignment of layers by photo lithography process. Alignment of layers formed on PC substrate is found to be more accurate than that on PES substrate. Figure 3 shows how the each process step affects on the properties of OTFT. In the case of mobility, the original value of OTFT after active deposition is decreased by more than 80% through a passivation. Figure 4 shows the actual photograph of OTFT device fabricated on PC substrate.

Fig. 1 The transfer characteristics of OTFT device fabricated on PES (a) and PC(b) substrates at various gate voltages.

(b) Fig. 2 The pictures of the misalignment by photo lithography process on PES (a) and PC(b) substrates.

Fig. 3 Process effect on the mobility of OTFT

#### 4. Conclusions

We have fabricated the OTFT through 5 inch scale process. The field effect mobility and on/off current ratio of the OTFT are about  $0.05 \sim 0.25$  cm<sup>2</sup>/Vs and  $10^5$  order. And how the effects of each process against the performance of OTFT have been found.

- **5. References**1. C.C.Lee,IMID'04 proceeding, p880 (2004)

2. Thomas. N. Jackson, Organic Thin Film Electronics '04

- 3. Thomas. N. Jackson, The 5<sup>th</sup> Internaitonal Conference on Electroluminescence of molecular materials and related phenomena '05, p43