## 저용량형 국부소자가 평행평판에 미치는 영향에 대한 비교연구

<sup>1</sup>주정호, <sup>1</sup>강 승택, <sup>2</sup>김형석 <sup>1</sup>인천대학교 정보통신공학과, <sup>2</sup>중앙대학교 전기전자공학부

# A case-study on low Capacitance Lumped Elements' Effects on Parallel Plates

<sup>1</sup>Jeong Ho Ju, <sup>1</sup>Sungtek Kahng, <sup>2</sup>Hyeongseok Kim

<sup>1</sup>Dept. Info. & Telecomm. Eng. at Univ. of Incheon, <sup>2</sup>School of Electrical and Electronics Engineering at Chung-Ang Univ.

**Abstract** - This paper conducts a study on the way the PCB's parallel plates' performances are affected by the loading of low cap. elements such as low cap-decoupling capacitors in conjunction with other lumped element. The fields and impedance profiles are rigorously evaluated and analyzed on various cases loaded with the above components and their effects will be given to bring better PCB EMC schemes

### 1. Introduction

In the PCB circuitry, layers are stacked and the power-bus as parallel plates will cause the cavity resonance and spurious spikes in its impedance as the EMI noise  $^{(1)-(6)}$ .

Therefore, it needs examining that placing local elements on the parallel plates affects the initial resonances [2]-[6]. As the local components, decoupling capacitor(DeCap)s are used to weaken the resonance.

This paper investigates the structure loaded with DeCaps and possibly with vias in the same structure.

#### 2. Theory

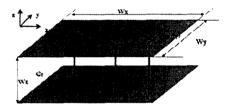

The power supply plane and its ground form parallel plates. In Fig. 1, such a structure is illustrated with  $W_x$  by  $W_y$  by  $W_z$  in size.

〈그림 1〉 Parallel plates of interest

The feeding is made at  $(X_s, Y_s)$ . The observation is done at  $(X_0, Y_0)$ . The intermediate region between the metal planes correspond s to the PCB's substrate and 4.2 and 0.02 are each chosen as its relative dielectric constant and loss tangent. The impedance of the structure is given as follows.

$$Z(X_{0}, Y_{0} | X_{f}, Y_{f})$$

$$= \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} Y_{mn} \cdot C_{mn}(X_{0}, Y_{0}) \cdot C_{mn}(X_{f}, Y_{f}) \cdot W_{z}$$

$$/[[\epsilon \mu/Q + j \{\epsilon \omega - (k_{xm}^{2} + k_{yn}^{2})/(\omega \mu)\}] \cdot (W_{x} W_{y})]$$

(1)

where

$$C_{mn}(X, Y) = \cos(k_{xm}X) \cdot \cos(k_{yn}Y)$$

$k_{xm} = mt/W_x, k_{yn} = nt/W_y, \omega = 2tf$

$Q = [\tan \delta + \{2/(\omega_0 x W_x^2)\}^{0.5}]^1$

$\omega_{mn} = \{(k_{xm}^2 + k_{yn}^2)/(z_0^2)\}^{0.5}$

$G_{mn} = C_0 \times \omega_{mn}/Q$

$m_n$  is 1 and 4 for (m=0, n=0) and (m=0, n=0) each. With (m=0, n=0) or (m=0, n=0),  $m_n$  is 2. tanb, t, t, t, and t denote loss-tangen t, permittivity, permeability, frequency and  $\sqrt{-1}$ , respectively. Eqn. (1) itself does not have terms to consider  $N_{Lu}$  loads with the

equivalent lump elements  $(Z_{Lu})$  of which can be simply expressed as a series equivalent circuit.

$$Z_{Lu} = R_{Lu} + j \left( \omega L_{Lu} \cdot 1/(\omega C_{Lu}) \right) \tag{2}$$

In order for the loading effect to be included, the following matrices can be used.

$$\begin{bmatrix} V_0 \\ [V_{Lu(i)}] \end{bmatrix} = \begin{bmatrix} Z_{00} & [Z_{0,Lu(i)}] \\ [Z_{Lu(i),0}] & [Z_{Lu(i),Lu(i)}^{int}] \end{bmatrix} \cdot \begin{bmatrix} I_0 \\ [I_{Lu(i)}] \end{bmatrix}$$

And

$$[V_{Lu(i)}] = -[Z_{Lu(i),Lu(i)}^{Ext}] \cdot [I_{Lu(i)}]$$

with

$$Z_{Lu(i),Lu(i)}^{Ext} = Z_{Lu}, Z_{Lu(i),Lu(i)}^{Ext} = 0$$

$$Z_{Lu(i),Lu(i)}^{Int} = Z(X_{Lu(i)},Y_{Lu(i)} \mid X_{Lu(i)},Y_{Lu(i)}).$$

$$Z_{0, Lu(j)} = Z(X_0, Y_0, X_{Lu(j)}, Y_{Lu(j)}), Z_{Lu(j), 0}$$

$$= Z(X_{Lu(j)}, Y_{Lu(j)} | X_0, Y_0)$$

These are manipulated as

$$Z_{00} \leftarrow Z_{00} - [Z_{0,Lu(i)}] \cdot ([Z_{Lu(i),Lu(i)}^{int}] + [Z_{Lu(i),Lu(i)}^{int}])^{-1} \cdot [Z_{Lu(i),0}]$$

which is the generalized input impedance. The generalized transimpedance can be obtained in a similar manner. On account of it s denominator's zeroes, the impedance profile has resonance. Rese arches have seen the mounted elements on either or both of the parallel planes can change the resonance characteristics.

### 3. Numerical Experiments

All the cases go with the observation point ( $X_o$ =144.4 mm,  $Y_o$ =100 mm) and the feed point at ( $X_s$ =44.4 mm,  $Y_s$ =50 mm). The structure's size amounts to ( $W_x$ =200 mm,  $W_y$ =150 mm,  $W_z$ =1.5 mm).

Firstly, we investigate the impedance of the structure when we change the number, distribution and positions of DeCaps. Four cases are dealt with, where 4, 16, 25 and 36 DeCaps are evenly distributed in the structure.

<그림 2> 4 and 16 evenly placed DeCaps

They look like square matrices of DeCaps' positions. The 4 and 16 DeCaps are placed as follows. For evaluating the impedance b etween  $(X_s, Y_s)$  and  $(X_0, Y_0)$ , all the DeCaps are given 7.3 nF as capacitance, 0.5 nH as ESL, and 85 ml as ESR which is comme

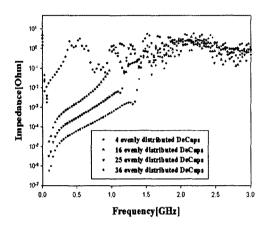

rcially available. Now we compare how the 4, 16, 25 and 36 DeC aps affect the impedance(Fig. 3).

Seeing Fig. 2, it is obvious the more DeCaps are placed in the p ower-bus, the wider becomes the resonance-suppressed regime. P articularly, from the use of 16 DeCaps, the impedance can be low ered by over 40 dB at 500 MHz with respect to the 4 DeCap-ca se.

<그림 3> Impedance of 4 and 16 evenly placed DeCaps

Next, we are dealing with the rectangular matirces of DeCap positions. Example 1 is to compare 2-by-4 and 4-by-2 rectangular distribution. Each of them has 8 DeCaps in a total. The followin g shows the illustration of these two ways of placement. When the impedance is calculated, all the DeCaps are assumed the same as those of Fig. 3. Example 1 results in not much difference bet ween the two cases, since the density of population is close to e ach other.

<그림 4> 4-by-2 and 2-by-4 rectangularly placed DeCaps

However, the 4-by-2 case is superior to the other in noise-suppr ession around 500 MHz, because DeCaps are in the vicinity of bo th the two ports. Similarly, in Example 2, 12 DeCaps are laid in two distribution cases as 4-by-3 and 6-by-2. They are illustrat ed as follows.

<그림 5> Impedance of 4-by-2 and 2-by-4 rectangularly placed DeCaps

Solving Example 2 on the rectangular matrix of placement, the D eCaps are identical with Fig.s 3 and 5.

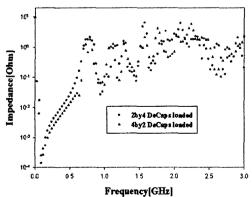

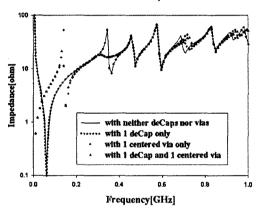

Lastly, the cases are handled with no loading, only 1 DeCap, 1 v ia, and 1 DeCap and 1 via., with  $(X_0=0, Y_0=0)$ , and 1 via at  $(X_V=100 \text{ mm}, Y_V=75 \text{ mm})$  and 1 DeCap at  $(X_D=200 \text{ mm}, Y_D=75 \text{ m})$  m) are used. The DeCap has  $C_D=47 \text{ pF}$  with  $R_D=5.2 \text{ Ohms}$  and  $L_D=3.8 \text{ nH}$  Similarly, the value of the via is given as  $L_V=1.097n$  H as can be done in [5].

As case 1 goes with neither vias nor DeCaps, it shows its origin al resonance modes. With only the DeCap loaded, case 2 sees the successful damping of (1, 0)-mode. It is a matter of course that the other resonance modes at higher frequencies undergo slight c hanges. In case 3, a via centered at the planes shifts (2, 0) and (0,2) modes and results in no intended damping. but causes an additional resonance around 120 MHz which is believed to be a critical noise. This via still brings that extra resonance with (1, 0) resonance mode damped by the DeCap in case 4. These noises could stem from added inductance. So keep in mind their correlation.

<그림 6> Impedance of DeCaps placed with a via

### 3. 결 론

Considering the EMI-causing resonance related to the cavity-typ e parallel planes, the structure's impedance has been rigorously e valuated. Based upon this prediction method, DeCaps and vias ar e used to damp the undesirably high impedance with resonance. This can lead to success in suppressing the specific resonance.

#### 감사의 글

본 연구는 기초전력연구원의 전력선행기술 신규과제지원으로 이루 어졌습니다.

#### [참고문헌]

- S. Van den Berghe et al., "Study of the ground bounce caused by power plane resonances", *IEEE Trans. EMC*, vol. 40, no. 2, pp. 111-119, May 1998.

- [2] J. Trinkle et al., "Efficient impedance calculation of loaded po wer ground planes", in Proc. 15<sup>th</sup> Zurich Symp. EMC, Zurich, Switzerland, 18, pp. 285–290 Feb. 2003.

- [3] T. Okoshi, Planar Circuits for Microwaves and Lightwaves, B erlin, Germany: Springer-Verlag, 1985.

- [4] V. Ricchiuti, "Supply decoupling on fully populated high-speed digital PCBs", IEEE Trans. EMC, vol. 43, pp. 671-676, Nov. 2001.

- [5] J. Fan et al., "DC power-bus modelling and design with an MPIE formulation and circuit extraction", IEEE Trans. EM C, vol. 43, no. 2, pp. 426-436, May 2001.

- [6] X. Ye et al., "DC power-bus design using FDTD modeling w ith dispersive media and surface mount technology", IEEE T rans. EMC, vol. 43, no. 4, pp. 579-587, Nov. 2001.