# The Research on Vertical Block Mura in TFT-LCD

*Chunping Long<sup>1</sup>, Wei Wang <sup>2</sup>, Hongjiang Wu<sup>2</sup>* <sup>1</sup>Dept. of Process Engineering, Beijing BOE Optoelectronics Technology CO., LTD., Beijing, China

TEL:86-10-67855688-6115, e-mail: wuhongjiang@boe.com.cn,gabrielwoo@163.com

Keywords : TFT LCD, Mura, Flicker, Coupling Capacitance, Display Quality

### Abstract

In this paper, a vertical block mura, which massively occurred in the LCD products, was investigated extensively by various methods, source drain (SD) line shift is found out to be one of the key reasons. This work to some extent, establishes theoretic hypothesis for further research and solutions similar issues.

## **1. Introduction**

Mura is one type of visual defects, which shows display gray level non-uniformity on the display screen.

A simple way to detect mura is to tune the display pattern to black pattern or other low gray level pattern in the darkroom. Observing the display screen from different angles, various types of mura could be seen on the display screen along with multifarious manufacturing flaws. Vertical block mura demonstrates vertical strip pattern on the display screen, which is easy to be seen at L63 gray level, as shown in Fig. 1.

Fig.1. Vertical Block Mura

Vertical block mura occurring position, size and level are unfixed. It occurs randomly and usually appears with other defects. Vertical block mura doesn't hamper the use of display device, but it deteriorates image quality. This work attempts to solve this issue in TFT-LCD mass production.

# 2. Experimental

In order to find out the root cause of vertical block mura, we had carried out a series of experiments by the microscopic measurement and the theoretical calculation, which are shown as follows:

2-1).A module sample which has vertical block mura was put onto panel inspection equipment. TFT-LCD driving signal was input with Vcom voltage tuned from 3V-4.8V. The test voltages are listed in table 1. The trend of vertical block mura was observed.

|            |         | 8          | 0       |

|------------|---------|------------|---------|

| Test Split | Vcom(V) | Test split | Vcom(V) |

| A          | 3.0     | F          | 4.0     |

| В          | 3.2     | G          | 4.2     |

| C          | 3.4     | Н          | 4.4     |

| D          | 3.6     | J          | 4.6     |

| Е          | 3.8     | K          | 4.8     |

Table 1.TFT-LCD Vcom voltage change test

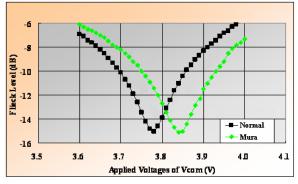

2-2).A module sample which has vertical block mura was used in flicker measurement.

Fig.2 Normal and Vertical Block Mura area flicker measurement

The normal display area and vertical block mura area was labeled on the module. as shown in Fig. 2. The module display flicker level varied with changing Vcom voltages. The flicker-Vcom curves were compared between the normal area and vertical block mura area.

2-3). A module sample which has vertical block mura was disassembled into panel, backlight unit and driver IC. The panel was decaped separating the TFT glass substrate from CF glass substrate. Then measure every TFT layer's Critical Dimension (CD) and overlay on the TFT Glass substrate.

#### 3. Result and discussion

### 3.1

Tuning Vcom voltage from 3V to 4.8V, vertical block mura level changes consequently as shown in table 2.

| Table 2.1F1-LCD V com voltage test result |      |                                 |  |  |  |

|-------------------------------------------|------|---------------------------------|--|--|--|

| Test split                                | Vcom | Vertical Block<br>Mura leveling |  |  |  |

| А                                         | 3.0  | L2                              |  |  |  |

| В                                         | 3.2  | L2                              |  |  |  |

| С                                         | 3.4  | L4                              |  |  |  |

| D                                         | 3.6  | L5                              |  |  |  |

| E                                         | 3.8  | L5                              |  |  |  |

| F                                         | 4.0  | L3                              |  |  |  |

| G                                         | 4.2  | L2                              |  |  |  |

| Н                                         | 4.4  | L1                              |  |  |  |

| J                                         | 4.6  | LO                              |  |  |  |

| K                                         | 4.8  | LO                              |  |  |  |

Table 2.TFT-LCD Vcom voltage test result

When Vcom voltage is about 3.6-3.8V, vertical block mura becomes the worst. When Vcom voltage exceeds 4.6V, vertical block mura is very difficult to be observed. It implies that vertical block mura level is related with Vcom voltage, as demonstrated in Fig.3. Table3 is Vertical Block Mura leveling description.

Fig.3. Vertical Block Mura level vs Vcom

#### Table3. Vertical Block Mura leveling description

| Vertical Block Mura leveling |    |    |    |    |    |    |

|------------------------------|----|----|----|----|----|----|

| weak strong                  |    |    |    |    |    |    |

| L0                           | L1 | L2 | L3 | L4 | L5 | L6 |

3.2

In the flicker level measurement, the Vcom voltage corresponding to the lowest flicker level has about 0.06V difference between the vertical block mura area and normal display area, as shown in Fig 4.

Fig 4. Flicker level curve with Vcom variation

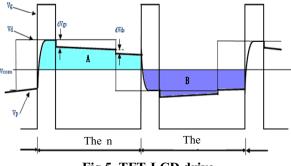

$$\Delta Vp = dVgs + dVds$$

$$dVgs = dVg \times \frac{Cgs}{Cgs + Clc + Cst + \cdots}$$

$$dVds = dVd \times \frac{Cds}{Cgs + Clc + Cst + \cdots}$$

Where Cgs is the parasitic capacitance between gate and source, Clc is the liquid crystal capacitance, Cst is the storage capacitance, Cpd is the parasitic capacitance between sub-pixel ITO and data line. dVg is gate line voltage range between Von and Voff, and dVd is data line signal voltage range<sup>[1]</sup>.

In the above experimental result, Vcom voltage difference of 0.06V between normal area and vertical block mura area represents  $\Delta Vp$  difference of 0.06V. At standard L127 gray level:

$$\Delta Gray = K\Delta Vp$$

Where K is a experiential constant being 152.  $\Delta vp$  of 0.06V results in  $\Delta Gray$  of 9.12 shown in table 4.

| result |                                   |                     |                        |            |                        |                     |

|--------|-----------------------------------|---------------------|------------------------|------------|------------------------|---------------------|

| Area   | Flicker<br>weakest<br>Vcom<br>(V) | Vcom<br>warp<br>(V) | Data<br>Voltage<br>(V) | ΔVp<br>(V) | Gray<br>warp<br>(L127) | SD<br>shift<br>warp |

| Normal | 3.78                              | 0.06                | 0-11                   | 1.72       | 9.12                   | about               |

| Mura   | 3.84                              | 0.00                | 0-11                   | 1.66       | 9.12                   | 0.5µm               |

Table 4. Vertical Block Mura flicker check

Fig.5. TFT-LCD drive

The Vcom voltage from printed circuit board (PCB) is the same for the whole panel. The difference of Vcom voltage reveals the relationship between mura and TFT load, for example expose equipment aligning system<sup>[2,3]</sup> problem in array process. Due to the coupling capacitance<sup>[4]</sup> between data line and pixel electrode, the pixel voltage changes when the data line signal changes illustrated in Fig.5.

### 3.3

In a pixel, there are several parasitic and coupled capacitors to affect feed through voltage ( $\Delta Vp$ ) such as Clc, Cgs, Cpd, and Cst<sup>[5]</sup>. According to capacity calculation formula

$$C = \varepsilon \varepsilon 0 \frac{A}{d}$$

<sup>[6]</sup>

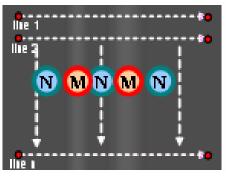

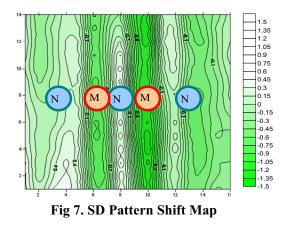

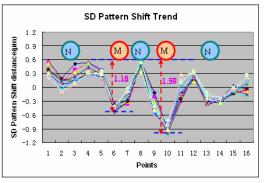

Know capacity relative with electrical medium, area and distance, Critical dimension and overlay on the array substrate is measured to characterize the above capacitances. According to the results shown in Fig. 6, 7, 8, SD pattern shift map has the same profile with vertical block mura. This demonstrates the relationship between SD pattern shifts and vertical block mura. Fig. 9 shows the SD pattern shift images taken under the optical microscope.

Fig 6. CD and Overlay Measure point

Fig 8. SD Pattern Shift Trend

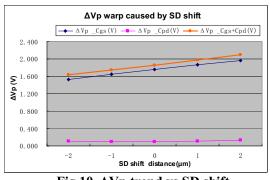

According to the Table 5, SD pattern shift affects capacitance Cgs and Cpd etc, and thus affects  $\Delta$ Vp, luminance and gray level. Fig. 10 shows linear relationship between  $\Delta$ Vp and SD shift distance. When SD pattern shift exceed certain value, it results in the different coupling capacitance in the different display area. The coupling capacitance difference results in gray level difference in different display area, and vertical block mura appears.

| SD shift<br>distance(µm)   | -2    | -1    | 0     | 1     | 2     |

|----------------------------|-------|-------|-------|-------|-------|

| Cgs(pF)                    | 0.018 | 0.020 | 0.021 | 0.023 | 0.024 |

| $\Delta Vp Cgs(V)$         | 1.530 | 1.645 | 1.757 | 1.865 | 1.969 |

| Cpd(pF)                    | 0.008 | 0.007 | 0.008 | 0.009 | 0.010 |

| $\Delta Vp Cpd(V)$         | 0.104 | 0.101 | 0.103 | 0.114 | 0.133 |

| $\Delta Vp$<br>_Cgs+Cpd(V) | 1.634 | 1.746 | 1.860 | 1.979 | 2.103 |

| L127<br>luminance          | 111.4 | 83.7  | 63.0  | 45.3  | 37.0  |

| Real Gray<br>Level         | 158   | 143   | 127   | 111   | 97    |

Table5. Variable according to SD Shift

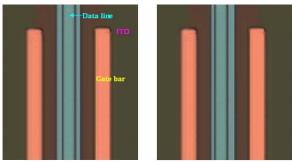

a. Normal area pattern b. Mura area pattern Fig 9. Pattern compare between normal and mura area

Fig.10.  $\Delta Vp$  trend vs SD shift

In the TFT LCD photolithography process<sup>[7]</sup>, alignment offset caused by the photo mask and exposure equipments may affect the uniformity of the arc light<sup>[8]</sup>. Comparison of data pattern shift between normal area and mura area caused by the non-uniformity of exposure light<sup>[9,10]</sup> is shown in figure 9. Figure 9a is microscope picture on the normal area and figure 9b is microscope picture on the mura area. With reference to figure 9a, data line of figure 9b shifts left. The distance between data line and the left gate bar/ITO becomes smaller, while the distance between data line and the right

gate bar/ITO becomes larger. This is the main reason of Vertical Block mura.

### 4. Conclusions

From the above experiments and discussion we conclude that SD pattern shift is one of the key reasons leading to vertical block mura. This work to some extent establishes theoretic hypothesis for further research and provides solutions to similar issues in the future.

# 5. Acknowledgements

This work was supported by science and technology committee of Beijing city project No D0306006000091

## 6. References

- 1.Toshihisa Tsukada, TFT/LCD [M], Hitachi Ltd. Tokyo, Japan, 1996, P12-26.

- 2. D.A.Markle, Solid State Tech. [J], 20:50(June 1979)

- 3. M.C.King, New Generation of Optical 1:1 Projection Aligners, In Developments in Semiconductor Microlithography IV [J], Proc. SPIE 174:70,1979.

- 4. Sung Mo kang, Yusuf leblebici COMS Digital Integrated Circuits: Analysis and Design (Third Edition) [M], Beijing, Publishing House of Electronics Industry, 2005, P182-187.

- 5. Sung Mo kang, Yusuf leblebici COMS Digital Integrated Circuits: Analysis and Design (Third Edition) [M], Beijing, Publishing House of Electronics Industry, 2005, P97-105.

- Thomas L.Floyd, Principles of Electric Circuits Conventional Current Version Seventh Edition [M], Beijing, Publishing House of Electronics Industry, 2005, P383-388.

- 7. Stephen A. Campbell, The science and Engineering of microelectronic Fabrication (Second Edition) [M], Beijing, Publishing House of Electronics Industry, 2003, P166-172.

- 8. R.T.Kerth, K.Jain, and M.R.Latta, Exciter Laser Projection Lithography on a Full-Field scanning Projection System [J], IEEE Elec. Dev. Lett. EDL-7, 1986, P299.

- 9. P.Burggraaf, Wafer steppers and Lens Options [J], Semi-condor Int. 56, March 1986

- Harry J.Levinson, Principles of Lithography [M], the International Society for Optical Engineering. SPIE. 2001 P97-104.