# Thin Film Transistor fabricated with CIS semiconductor nanoparticle

Bong-Jin Kim<sup>1</sup>, Hyung-Jun Kim<sup>1</sup>, Sung-Mok Jung<sup>1</sup>, Tae-Sik Yoon<sup>2</sup>, Yong-Sang Kim<sup>2</sup> Youngmin Choi<sup>3</sup>, Beyong-Hwan Ryu<sup>3</sup>, Hyun Ho Lee<sup>1\*</sup> <sup>1</sup>Department of Chemical Engineering, Myongji University

<sup>2</sup>Department of Nano Science & Engineering, Myongji University, Gyeonggi 449-728, Republic of Korea

<sup>3</sup>Advanced Material Division, KRICT, Yuseong, Daejeon 305-600, Republic of Korea

Phone: 82-31-330-6392 , E-mail: hyunho@mju.ac.kr

#### Abstract

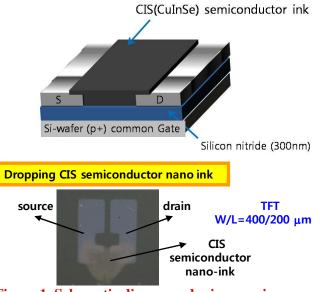

Thin Film Transistor(TFT) having CIS (CuInSe) semiconductor layer was fabricated and characterized. Heavily doped Si was used as a common gate electrode and PECVD Silicon nitride  $(SiN_x)$  was used as a gate dielectric material for the TFT. Source and drain electrodes were deposited on the SiN<sub>x</sub> layer and CIS layer was formed by a direct patterning method between source and drain electrodes. Nanoparticle of CIS material was used as the ink of the direct patterning method

### **1. Introduction**

Recently, tremendous developmental demands for printed electronics are widely experienced. For example, RFIDs are being developed in a platform of the printed electronics. Typically, the platform is frequently on the basis of organic material to constitute electronic devices [1]. However, the electrical performance of the organic material-based device is still far behind of that of inorganic materialbased device. Instead of organic material, very recently, silver ink is intensively introduced for device fabrication of printing electronics [2]. In this study, CIS nanoparticle was used as a printing ink of semiconductor layer for fabrication of thin film transistor. The CIS semiconductor ink was applied by a simple dropping or a direct patterning method, such as piezo inkiet. Output and transfer characteristics of CIS TFT were characterized.

## 2. Experimental

For CIS(CuInSe) semiconductor thin film transistor (TFTs) fabrication, a heavily boron (p+) doped silicon substrate was served as the gate in an inverted-gate structure. For dielectric layer, SiN<sub>x</sub> films, grown by PECVD(RF-frequency HF 13.56MHz, LH 400KHz) at 400  $^{\circ}$ C was used. The deposition pressure was 0.3mTorr and resultant film's refractive index was 2.02. After deposition of the dielectric layer, 100 nm thick aluminum layers were evaporated with source and drain patterned shadow mask on top of the  $SiN_x$ substrate. Two aluminum electrodes (source-drain) with a channel width-to-length ratio of 2 (channel length equals 200  $\mu$ m) were formed on the SiN<sub>x</sub> layer. After the CIS semiconductor was formed by a direct patterning method between source and drain electrodes, the films were annealing at 400 °C for 1 h in an N<sub>2</sub> atmosphere. Finally, a schematic crosssectional view and microscopic photograph of the fabricated transistors are depicted in Fig. 1. I-V curves were obtained for the fabricated field-effect TFTs with an Agilent 4145B semiconductor parameter analyzer in ambient condition.

Figure 1. Schematic diagram ad microscopic photograph of fabricated TFTs silicon substrate.

### 3. Results and discussion

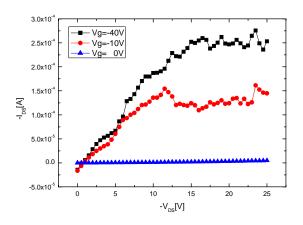

The field-effect characteristics of the TFTs fabricated on silicon substrates were investigated. Figure 2 shows the plot of  $I_D$  versus  $V_D$  modulated by applying a gate voltage ranging from 0 to -20 V for a representative TFT fabricated on a silicon substrate. It shows a typical characteristic of a p-channel transistor with a saturation region. The ON/OFF current ratio  $(I_{ON}/I_{OFF})$  was about 10<sup>2</sup>. Although the large ON current level is achieved, a high OFF-current level in the sub-micro ampere range results in a small  $(I_{ON}/I_{OFF})$  ratio compared with conventional siliconbased TFTs. It is reported that the operating gate voltage can be reduced by substituting thin  $Al_2O_3$  for thick SiO<sub>2</sub> bottom gate dielectric that is used in most solution-processed inorganic transistors [3]–[4]. Therefore, the SiN<sub>x</sub> layer in our experiment can be substituted for more optimized device performance. In this study, by introduction of a new material of CIS nanoparticle for active layer of TFT, a high performance device can be made with directpatterning method technology. It can be a breakthrough technology to make a real mass production of printed electronics, such as flexible display

**Figure 2.** Output characteristics of a CIS (CuInSe) nanoparticle TFT.

#### 4. Summary

TFT having CIS (CuInSe) semiconductor layer fabricated by dropping CIS nanoparticle ink was characterized. The TFT showed a high current level of output characteristic and low ON/OFF current ratio of  $10^{2}$ . Provided the low  $I_{ON}/I_{OFF}$  is improved, CIS nanoparticle TFTs have the potential to be used as the building blocks for a high performance TFT device.

#### **5. References**

- [1] C. D. Dimitrakopoulos, et al., *Adv. Mater.* **14**, 99-117 (2002).

- [2] J. Daniel, A. Arias, et al., SID 07 Digest, 249 (2007).

- [3] T. Shimoda, Y. Matsuki, M. Furusawa, T. Aoki, I. Yudasaka, H. Tanaka, H. Iwasawa, D. Wang, M. Miyasaka, and Y. Takeuchi, "Solution processed silicon films and transistors," *Nature*, vol. 440, no. 7085, pp. 783–786, Apr. 2006

- [4] D. V. Talapin and C. B. Murray, "PbSe nanocrystal solids for n- and p-channel thin film field-effect transistors," *Science*, vol. 310, no. 5745, pp. 86–89, Oct. 2005