# Top-down 방식으로 제작한 실리콘 나노와이어 ISFET의 전기적 특성 비교

A Comparative Study on the Electrical Characterization of Top-down Fabricated Silicon Nanowire ISFET \*김성만¹, #조영학¹,², 이준형¹,², 노지형³, 이대성³

\*S. M Kim<sup>1</sup>, \*Y. H. Cho(yhcho@seoultech.ac.kr)<sup>1,2</sup>, J. H. Lee<sup>1,2</sup>, J. H. Rho<sup>3</sup>, D. S. Lee<sup>3</sup> <sup>1</sup>서울테크노파크 MSP 기술지원센터, <sup>2</sup>서울과학기술대학교 기계시스템디자인공학과, <sup>3</sup>전자부품연구원 차세대융합센서연구센터

Key words: Nanowire ISFET, Top-down method, MEMS fabrication, Electrical property

### 1. 서론

실리콘 기반의 트랜지스터는 집적도와 속도를 향상시키기 위해서 지속적으로 그 크기가 축소 되어 지고 있다 [1-3]. 특히, 실리콘 나노와이어 트랜지스터 (Si-NWFET) 는 높은 전류 전달능력, 낮은 드레인 누설전류, 스케일링, short channel effect immunity 우수성[4]으로 인해 차세대 소자로 주목받고 있으며 또한 다중게이트 구조의 FET 는 planar 소자에 비해 equivalent oxide thickness (EOT)의 스케일링 부담을 덜 갖게 된다는 장점이 있다.

실리콘 나노와이어를 제작하는 여러 방법 중에서도 top-down 방법으로 제작한 나노와이어 어레이는 나노와이어 개개의 규격과 성능을 신뢰할수 있으며, 재현성 있는 나노와이어의 제작이 가능하고 기존의 실리콘 공정을 활용할수 있다는 뛰어난 장점이 있다.

본 연구에서는 기존 MEMS 공정을 이용하여 실리콘 나노와이어 어레이를 제작하고 전기적 특 성을 비교하여 전계효과 트랜지스터 (FET)로 적용 하기 위한 가능성을 모색하였다.

#### 2. 실험장치 구성 및 방법

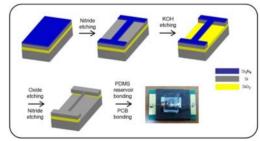

KOH 이방성 엣칭과 기본적인 MEMS 공정을 이용하여 실리콘 나노와이어 어레이를 제작하였다. 상부 실리콘충/하부 실리콘 산화막 충 두께가 각각 2um/2um인 SOI (Silicon On Insulator) 웨이퍼를 사용하였으며, SOI 웨이퍼의 표면에 LPCVD 법으로 약 1,000Å 두께의 질화 실리콘(Si<sub>3</sub>N<sub>4</sub>) 박막을 중착하여 패터닝 공정후에 KOH 엣칭공정을

위한 마스크로 사용하였다. KOH 용액의 농도는 30%, 온도는 50℃로 하였으며, 이 때의 엣칭 속도는 약 0.2um/min 로 확인되었다. 나노와이어 선폭을 약 200nm까지 엣칭한 후, 건식 RIE공정으로 실리콘 질화막을 제거하였으며 BOE 용액으로 하부의실리콘 산화막 희생충을 제거함으로써 현수형 실리콘 나노와이어를 제작하였다.

제작된 나노와이어 표면에 ion implantation 공법으로 B이온을 삽입, 전기저항을 컨트롤 하였다. 이후 용액중에서 측정가능하도록 PDMS로 reservoir를 제작하여 나노와이어 시편에 부착하였고, 나노와이어 양 끝단의 전극패드 부분을 PCB에 본 당처리하였다. 전체 공정의 개요와 완성된 시편을 Fig. 1에 나타내었다.

Fig. 1 Schematic diagram of overall fabrication process of NW-FET.

#### 3. 실험결과 및 고찰

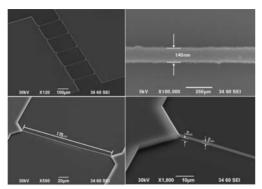

제작된 나노와이어 시편의 전자현미경 사진을 Fig. 2에 나타내었다. 선폭 140nm, 길이 175um, 높이 2um의 실리콘 나노와이어가 하부 기판과 2um의 간격을 두고 현수되어있는 것을 확인할 수 있다.

Fig. 2 FE-SEM images of fabricated Si nanowire arrays. (width=140nm, length=175um, height=2um)

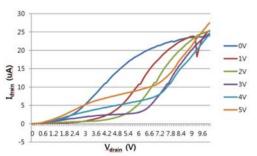

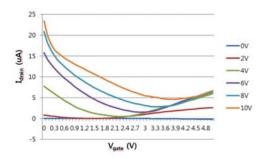

제작한 NW-FET 시편의 전기적 특성을 측정하여 그 결과를 Fig. 3과 Fig. 4에 나타내었다. 결과로부터 gate 전압이 증가함에 따라 문턱전압이 증가하며, 전류가 나노와이어를 따라 균일하게 흐르는 것을 확인할 수 있다. 다만 누설전류가 수 uA 영역대의 다소 높은 값을 갖는 것으로 확인되었는데, FET 작동시의 누설전류는 약 5nA보다 작아야 하므로 실험의 경향성 확보와 보다 안정적인 데이터수집을 위해 차후 연구에는 전극패드 부분에 Au 등의 금속으로 배선처리하여 실험할 예정에 있다.

Fig. 3 I<sub>d</sub>-V<sub>d</sub> characteristic for the fabricated NW-FET.

Fig. 4 I<sub>d</sub>-V<sub>gate</sub> characteristic for the fabricated NW-FET.

#### 4. 결론

KOH 이방성 엣칭과 기본적인 MEMS 공정을 이용하여 실리콘 나노와이어 ISFET를 제작하였다. 용액 중에서 작동할 수 있도록 시편을 제작하여 전기적으로 테스트한 결과, 기본적인 FET특성을 보이는 것으로 확인되었다.

## 후기

본 연구는 지식경제부에서 시행한 2011년 글로벌 전문기술개발사업의 지원으로 수행되었음.

#### 참고문헌

- G. E. Moore, "Progress in digital intergrated electronics", International Electron Devices Meetings Technical Digest, 11, 1975.

- W. Haensch, E. J. Nowak, R. H. Dennard, P. M. Solomon, A. Bryant, O. H. Dokumaci, A. Kumar, X. Wang, J. B. Johnson, M. V. Fischetti, "Silicon CMOS devices beyond scaling" IBM Journal of Research and Development archive, 50, 2006.

- Thompson, S. E. Chau, R. S. Ghani, T. Mistry, K. Tyagi, S. Bohr, M. T. "In search of Forever, continued transistor scaling one new materials at a time" IEEE Transactions on Semiconductor Manufacturing, 18, 26-36, 2005.

- 4. K. H. Yeo, S. D. Suk, M. Li, Y. Y. Yeoh, K. H. Cho, K. H. Hong, S. K. Yun, M. S. Lee, N. M. Cho, K. H. Lee, D. H. Hwang, B. K. Park, D. W. Kim, D. Park, and B. I. Ryu "Gate-All-Around Twin Silicon Nanowire MOSFET with 15nm length gate and 4nm radius nanowires" International Electron Devices Meetings Technical Digest, 1-4, 2006.