# UHD 영상의 실시간 처리를 위한 고성능 HEVC SAO 부호화기 하드웨어 설계

조현표・박승용・류광기

한밭대학교 정보통신전문대학원 정보통신공학과 Hardware Design of High-Performance SAO in HEVC Encoder for Ultra HD Video Processing in Real Time

Hyun-pyo Cho·Seung-yong Park·Kwang-ki Ryoo

Graduate School of Information and Communication, Hanbat National University

E-mail: chohyunpyo@naver.com

## 요 약

본 논문에서는 UHD급 영상의 실시간 처리를 위한 고성능 HEVC(High Efficiency Video Coding) SAO(Sample Adaptive Offset) 부호화기의 효율적인 하드웨어 구조를 제안한다. SAO는 HEVC에서 새롭게 채택된 루프 내 필터 기술 중 하나이다. 본 논문에서 제안하는 SAO 부호화기 하드웨어 구조는 메모리 접근 최소화 및 화소들의 처리를 간소화하기 위해 three-layered buffer를 사용한다. 또한 연산시간 및 연산량을 줄이기 위해서 4개의 화소들을 병렬적으로 에지 오프셋과 밴드 오프셋으로 분류하며, 화소들의 분류와 SAO 파라메터 적용을 2단계 파이프라인 구조로 구현하고, 하드웨어 면적을 줄이기 위해서 덧셈과 뺄셈, 쉬프트 연산, 그리고 재귀 비교기만을 사용한다. 본 논문에서 제안하는 SAO 부호화기 하드웨어 구조는 Verilog HDL로 설계하였으며, TSMC 0.18um CMOS 표준 셀 라이브러리를 사용하여 합성한 결과 약 180k개의 게이트로 구현되었다. 또한, 110MHz의 동작주파수에서 4K UHD급 해상도인 4096×2160@30fps의 실시간 처리가 가능하다.

## **ABSTRACT**

This paper proposes high-performance SAO(Sample Adaptive Offset) in HEVC(High Efficiency Video Coding) encoder for Ultra HD video processing in real time. SAO is a newly adopted technique belonging to the in-loop filter in HEVC. The proposed SAO encoder hardware architecture uses three-layered buffers to minimize memory access time and to simplify pixel processing and also uses only adder, subtractor, shift register and feed-back comparator to reduce area. Furthermore, the proposed architecture consists of pipelined pixel classification and applying SAO parameters, and also classifies four consecutive pixels into EO and BO concurrently. These result in the reduction of processing time and computation. The proposed SAO encoder architecture is designed by Verilog HDL, and implemented by 180k logic gates in TSMC  $0.18\,\mu$ m process. At 110MHz, the proposed SAO encoder can support 4K Ultra HD video encoding at 30fps in real time.

#### 키워드

HEVC Encoder, Sample Adaptive Offset, SAO, SAO architecture, Hardware Design, HM11

## I. 서 론

최근 방송 및 통신 기술이 빠르게 발전함에 따라 고해상도 영상을 지원하는 HDTV와 멀티미디어 기기의 대중화가 이루어졌다. 이에 따라 고해

상도 영상 서비스에 대한 사용자들의 관심과 수요가 증가하였고, 나아가 더 높은 해상도의 영상서비스에 대한 연구와 개발로 이어졌다. 차세대영상 기기들의 개발 방향은 1920x1080 해상도인FHD급을 넘어서 4배 이상의 해상도를 갖는 4K, 8K 해상도인 UHD급의 초고해상도 영상으로 발전

## 하고 있다[1].

본 논문에서는 UHD급 영상의 실시간 처리를 위한 고성능 HEVC SAO 부호화기 하드웨어 구조를 제안한다. SAO는 차세대 압축 기술 표준인 HEVC의 루프 내 필터 기술 중 하나로 원본 영상과 복원 영상간의 통계적 특성에 따른 오프셋 값을 구하고, 이러한 오프셋 값을 복원 영상에 적용함으로써 원본 영상과 복원 영상간의 오차를 감소시키는 필터이다. 본 논문에서 제안하는 SAO 부호화기 구조는 SAO의 연산량과 연산시간을 감소시키 위해 한번에 4개의 화소를 병렬적으로 처리하며, 2단계 파이프라인 구조를 이용한다. 또한하드웨어 면적을 최소화하기 위해 덧셈과 뺄셈, 쉬프트 연산, 그리고 재귀 비교기만을 사용한다.

## Ⅱ. 본 론

HEVC 표준의 루프 내 필터 기술 중 하나인 SAO는 영역 기반 필터이며, DBF(Deblocking Filter)가 처리 된 후 수행된다. SAO는 한 영역의화소 간 통계적 분석에 따라 화소마다 다른 오프셋 값을 사용한다. SAO는 영역 기반 필터를 수행하기 때문에 각 영역마다 SAO 파라메터들은 적응적으로 변화한다. SAO는 두 가지 화소 분류 타입인 에지 오프셋과 밴드 오프셋을 이용하여 화소를 분류하고, 분류된 화소 정보를 이용하여 최적의 오프셋 값 및 SAO 파라메터를 생성한다[2].

# A. 에지 오프셋

에지 오프셋은 구현의 복잡성과 부호화 효율 간의 합리적인 균형을 이루기 위해 1차원적인 방 향성을 나타내는 4가지 주요 패턴을 사용하여 화 소를 분류한다. 이는 영역 내 에지 특성을 고려하 여 복원 영상의 왜곡을 효과적으로 보정하기 위 한 것으로 그림 1에서 나타내는 것과 같은 4가지 에지 패턴들을 사용한다.

그림 1. 에지 오프셋의 4가지 주요 패턴

그림 1의 각 패턴에서 표시된 C는 분류될 현재 화소를 나타내고, A와 B는 에지 방향성에 따른 주변 화소를 나타낸다.

에지 오프셋은 화소를 분류하기 위해 각 4개의 주요 패턴에서 현재 화소와 주변 화소들을 표 1 과 같은 조건식에 따라 하위 카테고리로 분류한 다.

표 1. 하위 카테고리 결정 조건식

| Category | Condition                                            |

|----------|------------------------------------------------------|

| 1        | C <a &&="" c<b<="" td=""></a>                        |

| 2        | (C <a &&="" (c="=A" c="=B)" c<b)<="" td=""  =""></a> |

| 3        | (C>A && C==B)     (C==A && C>B)                      |

| 4        | C>A && C>B                                           |

| 0        | None of the above                                    |

표 1에서 나타내는 각 카테고리의 조건식은 영역 내 화소들의 에지 상태를 고려한 것이다. 카테고리 1과 2는 현재 화소가 주변 화소보다 작을 경우이고, 카테고리 3과 4는 현재 화소가 주변 화소보다 클 경우이다. 에지오프셋은 카테고리 1과 2에 오프셋 값을 담하고, 카테고리 3과 4에 오프셋 값을 감하여 복원 화소를 보상한다.

#### B. 밴드 오프셋

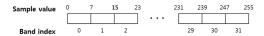

밴드 오프셋은 화소를 표현하는 색상의 밝기 범위를 일정한 크기의 32개 구간으로 나누어 분 류하고자 하는 화소를 화소의 밝기 값에 따라 해 당하는 구간으로 분류한다. 이는 영역 내 화소들 이 유사한 밝기 값을 가질 때를 고려하여 복원 영상의 왜곡을 효과적으로 보정하기 위한 것이다. 예를 들어, 화소가 8비트 심도의 밝기 범위를 가 질 때 화소의 밝기 값은 0부터 255까지이고, 이러 한 밝기 범위는 8의 크기를 갖는 32개의 일정한 구간으로 나뉜다. 이때 분류하고자 하는 화소 값 이 28이라면 4번째 구간으로 분류하게 된다. 그림 2는 밴드 오프셋의 32개 화소 분류 구간들을 나 타낸다.

그림 2. 밴드 오프셋의 32개 화소 분류 구간

밴드 오프셋은 그림 2와 같이 화소들을 32개의 밴드로 분류한 후, 각 밴드마다 오프셋 값을 결정 한다. 또한 32개의 밴드 중에서 최소의 율-왜곡 비율을 갖는 연속된 4개 밴드를 선택하고, 선택된 밴드 그룹에 속하는 복원 화소에 오프셋 값을 더 하여 복원 화소의 왜곡을 감소시킨다.

## Ⅲ. 제안하는 SAO 부호화기 하드웨어 구조

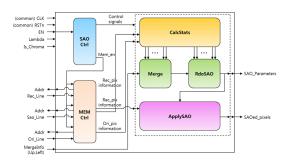

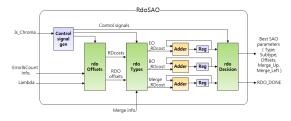

본 논문에서 제안하는 고성능 SAO 부호화기 하드웨어 구조는 그림 3과 같다.

그림 3. 제안하는 SAO 부호화기 하드웨어 구조

하드웨어 구조는 제어 신호를 생성하는 SAO Ctrl 모듈과 화소들을 분류하는 CalcStats 모듈, 최적의 오프셋과 파라메터를 결정하는 RdoSAO 모듈, Merge 여부를 체크하여 Merge 파라메터를 생성하는 Merge 모듈, 최적의 SAO 파라메터를 복원 화소에 적용하여 보상해주는 ApplySAO 모듈, 그리고 메모리로부터 처리될 화소 정보를 읽고 저장하는 MemCtrl 모듈로 구성된다.

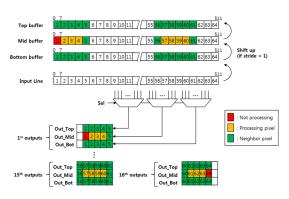

SAO 부호화기 하드웨어 구조는 메모리 접근 사이클을 최소화하고, 입력 화소들을 효율적으로 처리 및 전송하기 위해 three-layered buffer 구 조를 사용하여 MemCtrl 모듈을 구현하였다. 그림 4는 three-layered buffer 구조를 나타낸다.

그림 4. 제안하는 three-layered buffer 구조

Three-layered buffer 구조는 LCU(Largest Coding Unit)정보를 저장하고 있는 메모리로부터 한 사이클 당 한 줄의 화소 정보를 입력받아 최대 3줄을 저장하고, 처리 순서에 따라 처리될 화소 4개와 주변 화소 정보들을 다음 모듈로 전송한다. LCU 경계면에 있는 화소들은 주변 화소 정보가 없기 때문에 SAO를 처리하지 않으며, MemCtrl 모듈은 1번과 16번째에 경계면의 화소들을 제외한 화소 정보들을 전송한다.

CalcStats 모듈은 입력된 화소들을 에지 오프셋과 밴드 오프셋으로 분류하는 작업을 병렬적으로 수행하며, 구조는 그림 5와 같다.

그림 5. 제안하는 CalcStats 모듈 구조

CalcStats 모듈은 그림 5와 같이 입력 화소 정보들을 병렬적으로 4개 패턴의 에지 오프셋과 1개의 밴드 오프셋으로 분류한다. 분류된 정보들은 디멀티플렉서에 의해 해당하는 레지스터에 누적되어 진다. CalcStats 모듈은 하드웨어 면적을 감소시키기 위해 비교기 사용을 최소화하여 하드웨어 구조에 적합하도록 구현한 카테고리 분류기를 사용한다.

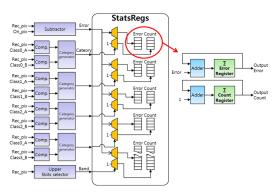

RdoSAO 모듈은 율-왜곡 비용을 계산하여 최적의 오프셋 및 파라메터를 결정하며, 구조는 그림 6과 같다.

그림 6. 제안하는 RdoSAO 모듈 구조

RdoSAO 모듈은 최소의 율-왜곡 비용을 갖는 각각의 오프셋 값들을 구하고, 에지 오프셋과 밴드 오프셋, 머지 모드 중에서 최소의 율-왜곡 비용을 갖는 타입을 결정한다. 마지막으로 밝기 성분과 색차 성분의 율-왜곡 비용을 합하여 최소의율-왜곡 비용을 갖는 SAO 파라메터를 결정한다. RdoSAO 모듈은 고속 왜곡 예측 기법을 기반으로율-왜곡 비용을 계산하고, 하드웨어 면적과 연산량을 고려하여 나눗셈기를 사용하지 않고, 덧셈기, 뺄셈기와 쉬프트만을 사용하여 구현하였다. 또한율-왜곡 비용이 양수일 경우 영상의 열화를뜻하거나 최적의 파라메터로 선택되지 않으므로양수 값을 갖는 율-왜곡 비용은 0으로 대체하고, 음수 값을 갖는 율-왜곡 비용은 양수 형태로 표현하여 연산의 복잡성을 감소시켰다.

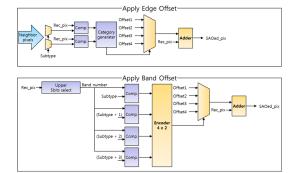

ApplySAO 모듈은 최적의 SAO 파라메터 정보 를 이용하여 복원 화소를 보상해주는 작업을 수 행하며, 구조는 그림 7과 같다.

그림 7. 제안하는 ApplySAO 모듈 구조

ApplySAO 모듈은 CalcStats 모듈과 비슷한 구조를 가지며, 4개의 복원 화소를 병렬적으로 처리한다. 최적의 SAO 파라메터에 따라서 에지 오프셋과 밴드 오프셋을 선택적으로 수행하고, 복원화소에 최적의 오프셋 값을 더함으로써 복원 영상의 왜곡을 감소시킨다.

본 논문에서 제안하는 SAO 부호화기 하드웨어 구조는 SAO 연산시간을 감소시키기 위해 그림 8 과 같이 2단계 파이프라인 구조로 구현하였다.

| Time                                     |                                           |                                              |                                             |                                                |                                             |  |

|------------------------------------------|-------------------------------------------|----------------------------------------------|---------------------------------------------|------------------------------------------------|---------------------------------------------|--|

| LCU <sub>n</sub><br>Pixel Classification | LCU <sub>n</sub><br>Parameter<br>Decision | LCU <sub>n+1</sub><br>Pixel Classification   | LCU <sub>n+1</sub><br>Parameter<br>Decision | LCU <sub>n+2</sub><br>Pixel Classification     | LCU <sub>n+2</sub><br>Parameter<br>Decision |  |

| ·                                        |                                           | LCU <sub>n</sub><br>Parameter<br>Application |                                             | LCU <sub>n+1</sub><br>Parameter<br>Application |                                             |  |

그림 8. 제안하는 SAO 2단계 파이프라인 구조

제안하는 구조는 LCU에 대하여 화소의 분류 작업을 수행하고, 분류 작업이 수행된 후 율-왜곡 최적화 작업을 통해 각각의 오프셋 및 최적의 타 입을 결정한다. 밝기 성분과 색차 성분에 대하여 율-왜곡 최적화 작업이 완료되면 밝기 성분과 색 차 성분의 율-왜곡 비용을 합산하여 최적의 SAO 파라메터를 결정한다. 결정된 최적의 SAO 파라메 터 정보는 ApplySAO 모듈로 전송되어 복원 화소 를 보상함과 동시에 다음 LCU에 대하여 화소의 분류 작업과 율-왜곡 최적화 작업을 수행한다.

## Ⅳ. 하드웨어 구조 결과 및 검증

본 논문에서 제안하는 고성능 SAO 부호화기하드웨어 구조는 Verilog HDL로 설계하였다. 하드웨어 합성은 IDEC에서 지원하는 Synopsys사의 DesignCompiler를 사용하였으며, TSMC 0.18um CMOS 표준 셀 라이브러리로 합성하였다. 표 2는 제안하는 SAO 부호화기 하드웨어 구조의 합성결과를 나타낸다.

표 2. 제안하는 하드웨어 구조 합성 결과

| Category       | Result              |  |  |

|----------------|---------------------|--|--|

| Process        | TSMC 0.18um CMOS    |  |  |

| Frequency      | 110MHz for 4K@30fps |  |  |

| Cycles per LCU | 1600                |  |  |

| Area(Kgates)   | 180                 |  |  |

4096x2160@30fps 영상을 실시간으로 처리하기 위해선 초당 약 65,280개의 LCU를 처리해야한다. 제안하는 SAO 부호화기 하드웨어 구조는 하나의 LCU를 처리하는데 1600 사이클을 소요하므로, 약 110MHz의 동작주파수에서 4K@30fps 영상을 실시간으로 처리할 수 있다.

## Ⅴ. 결 론

본 논문에서 제안하는 고성능 SAO 부호화기하드웨어 구조는 SAO의 연산시간을 감소시키기위해 한번에 4개의 화소를 병렬적으로 처리하며, 2단계 파이프라인 구조로 구현하였다. 또한 연산량과 하드웨어 면적을 감소시키기 위해 SAO 연산기들을 하드웨어에 적합한 구조로 구현하였고, 연산기 사용을 최소화하였다.

제안하는 하드웨어 구조는 합성 결과 약 180k 개의 게이트로 구현되었고, 약 110MHz의 동작주 파수에서 4K@30fps UHD급 영상을 실시간으로 처리할 수 있다.

## 감사의 글

본 연구는 교육부와 한국연구재단의 지역혁신 인력양성사업(NRF-2012H1B8A2025862)과 미래창 조과학부 및 정보통신산업진흥원의 해외인재스카 우팅사업(NIPA-HB616-13-1001)의 지원으로 수행 되었습니다.

## 참고문헌

- [1] G. J. Sullivan, J. R. Ohm, W. J. Han, and T. Wiegand, "Overview of the High Efficiency Video Coding(HEVC) Standard," IEEE Transaction on Circuits and Systems for Video Technology, vol. 22, no. 12, pp. 1649–1668, Dec. 2012.

- [2] C. M. Fu, E. Alshina, A. Alshin, Y. W. Huang, C. Y. Chen, C. Y. Tsai, C. W. Hsu, S. M. Lei, J. H. Park, and W. J. Han, "Sample Adaptive Offset in the HEVC Standard," IEEE Trans. Circuits Syst. Video Technol., vol. 22, no. 12, Dec. 2012.