# 저면적 12비트 연속 근사형 레지스터 아날로그-디지털 변환기

성명우\*·최근호\*·김신곤\*·Habib Rastegar\*·Abu Abdoulaye Tall\*·Murod Kurbanov\*· 최승우\*·Chandrasekar Pushpalatha·류지열\*·노석호\*\*·길근필\*\*\* \*부경대학교·\*\*안동대학교·\*\*\*부산과학기술대학교

### The Low Area 12-bit SAR ADC

Myeong-U Sung\*·Geun-Ho Choi\*·Shin-Gon Kim\*·Habib Rastegar\*·Abu Abdoulaye Tall\*· Murod Kurbanov\*·Seung-Woo Choi\*··Chandrasekar Pushpalatha·Jee-Youl Ryu\*·Seok-Ho Noh\*\*·Keun-Pil Kil\*\*\*

\*Pukyong National University·\*\*Andong National University·\*\*\*Busan Institute of Science and Technology

E-mail: ryujy@pknu.ac.kr

#### 요 약

In this paper we present a low area 12-bit SAR ADC (Successive Approximation Register Analog-to-Digital Converter). The proposed circuit is fabricated using Magnachip/SK Hynix 1-Poly 6-Metal 0.18-μm CMOS process, and it is powered by a 1.8-V supply. Total chip area is reduced by replacing the MIM capacitors with MOS capacitors instead of the capacitors consisting of overall part in chip area. The proposed circuit showed improved power dissipation of 1.9mW, and chip area of 0.45mm² as compared to conventional research results at the power supply of 1.8V. The designed circuit also showed high SNDR (Signal-to-Noise Distortion Ratio) of 70.51dB, and excellent effective number of bits of 11.4bits.

# 키워드 12-bit, SAR, ADC, 저면적

### I. 서 론

집적회로 기술의 꾸준한 발전으로 아날로그 영역에서 구현되어 왔던 많은 기능들이 디지털 영역에서 쉽게 구현되었다. 비약적인 기술의 발전으로 많은 종류의 신호처리는 디지털 영역으로 이동하였지만, 자연 신호의 처리에 있어서 아날로그신호처리에 대한 필요성은 여전히 큰 비중을 차지한다. 이러한 이유로 많은 시스템들은 아날로그신호처리를 위한 아날로그-디지털 변환기(Analog-to-Digital Converter, ADC)와 디지털 신호처리 장치를 필요로 하고 있다 [1-3].

본 논문에서는 면적을 줄이기 위해 여러 가지 구조의 ADC 중에서 저면적 12비트 연속 근사형 레지스터 (Successive Approximation Register, SAR) ADC를 제안한다. 전체 칩 면적 중 많은 부분을 차지하는 커패시터 부분을 MOS 커패시터 로 대체함으로써 전체 칩 면적을 줄였다.

### II. 본 론

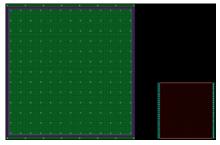

구성한 MOS 커패시터를 비교한 것이다. MOS 커패시터는 N형 트랜지스터를 이용하여 구성하 였다. 그림 1(b)의 MOS 커패시터가 그림 1(a)의 MIM 커패시터보다 약 80%의 면적 감소 효과를 보였다.

(a) MIM 커패시터 (b) MOS 커패시터 그림 1. 커패시터 비교

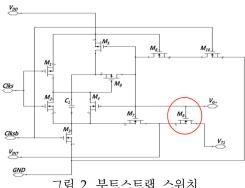

그림 2는 커패시터 어레이 입력단의 부트스트

랩 스위치를 나타낸 것이다. 부트스트랩 스위치는 정착속도 및 입력 대역폭을 증가시키는 기능을 하며, 입력 받은 아날로그 신호를 샘플링 및 홀드 하여 커패시터 어레이단으로 보내는 기능을 한다.

그림 2. 부트스트랩 스위치

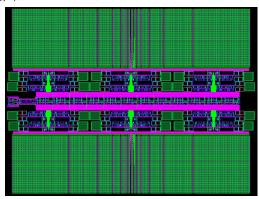

그림 3은 SAR ADC를 구성하는 전체 블록들 을 레이아웃한 결과이다. 레이아웃은 매그나칩 /SK하이닉스 1-Poly 6-Metal 0.18-μm CMOS 공 Cadence Tool을 이용하여 수행하였고, 레이아웃 결과 전체 면적은 0.45mm²로 기존의 연구 결과에 비해 가장 작은 칩 면적 특성을 보 였다.

그림 3. SAR ADC 레이아웃

## III. 시뮬레이션 및 결과

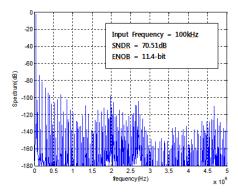

그림 4는 입력신호의 주파수가 100kHz일 때, ADC의 고속 푸리에 변환 (Fast Fourier Transform, FFT) 결과를 나타낸 것이다. FFT 결과 70.51dB의 높은 신호 대 잡음 왜곡비 (Signal-to-Noise Distortion Ratio, 보였고, 11.4비트의 우수한 유효비트수 (Effective Numbur of Bit, ENOB) 특성을 보였다.

그림 4. 고속 푸리에 변환 결과

#### IV. 결 론

본 논문에서는 저면적 12비트 연속 근사형 레 지스터 아날로그-디지털 변환기를 제안하였다. 전 체 칩 크기를 최소화하기 위해 MOS 커패시터를 적용하였고, 전력소모를 최소화하기 위한 최적화 를 고려하여 설계하였다. 제안된 SAR ADC는 기 존 연구 결과에 비해 0.45mm<sup>2</sup>의 작은 칩 면적, 1.9mW 수준의 낮은 소비전력, 70.51dB의 높은 SNDR 및 11.4비트의 우수한 ENOB 특성을 보였 다.

### 감사의 글

This research was supported by Basic Science Research Program through the National Research Foundation of Korea(NRF) funded by the Ministry of Education (2015R1D1A3A01015753).

## 참고문헌

- [1] B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill, 2013.

- [2] A. M. Abo and P. R. Gray, "A 1.5-V, 14.3-MS/s **CMOS** pipeline analog-to-digital converter", IEEE Journal of Solid-State Circuits 34, pp. 599-606, 1999.

- [3] K. J. Min et al. "Design of timing register structure for area optimization of high resolution and low power SAR ADC", Journal of the Institute of Electronics Engineers of Korea 47-SD, pp. 47-55, 2010.

- [4] J. S. Kim et al. "A design of SAR ADC for low power and area applications", Journal of the Institute of Electronics Engineers of Korea 46-SD, pp. 433-434, 2009.