# 전기적 상호작용을 고려한 3차원 순차적 인버터의 SPICE 시뮬레이션

안태준, 유윤섭\*

한경대학교 전기전자제어공학과

# SPICE Simulation of 3D Sequential Inverter Considering Electrical Coupling

Tae-Jun Ahn, Yun Seop Yu\*

Department of Electrical, Electronic and Control Engineering, Hankyong National University

E-mail: jigo1235@hknu.ac.kr

## 요 약

이 논문은 3D 순차적 CMOS 인버터 회로의 전기적 상호작용을 고려한 시뮬레이션을 제시하고자한다. 상층 NMOS는 BSIM-IMG, 하층 PMOS에는 LETI-UTSOI 모델을 사용하여 전기적 상호작용이 잘반영되는지 TCAD 데이터와 SPICE 데이터를 비교하였다. 트랜지스터 간의 높이가 작을 때 하층 게이트의 전압의 변화에 따라 상층 전류-전압 특성에 전기적 상호작용이 잘 반영되는 것을 확인하였다.

#### **ABSTRACT**

This paper introduces the SPICE simulation results of 3D sequential inverter considering electrical coupling. TCAD data and the SPICE data are compared to verify that the electrical coupling is well considered by using BSIM-IMG for the upper NMOS and LETI-UTSOI model for the lower PMOS. When inter layer dielectric is small, it is confirmed that electrical coupling is well reflected in the top transistor  $I_{ds}$ - $V_{gs}$  characteristics according to the change of the bottom transistor gate voltage.

#### 키워드

3차원 순차적 인버터, 3DIC, SPICE 모델, 3D sequential inverter, monolithic integration

## I. 서 론

반도체의 성능을 높이기 위해 무어의 법칙에 따라 트랜지스터의 크기를 계속 줄여 집적효율을 높여 왔다. 하지만 트랜지스터의 크기를 줄여 집 적효율을 높이는 것은 물리적인 한계가 있고, 이 를 탈피하기 위해 3차원 구조에 많은 관심을 가 지고 연구를 진행해 왔다[1]-[2]. 3차원 구조는 through silicon via(TSV) 방식을 사용하는 parallel 구조와 순차적으로 집적하여 쌓아올리는 sequential 구조가 있다. parallel 구조는 via를 통 해 웨이퍼들을 연결하며 주로 메모리 반도체에서 사용되고 있으며 트랜지스터 간의 높이(ILD)는 um 단위이다. 반면에 sequential 구조는 via 없이 하 나의 웨이퍼에 공정하여 적층하는 것으로 좋은 공정을 위해 기술 발전이 필요하지만 트랜지스터 간의 높이는 nm 단위로 집적 효율이 더 좋다.

현재 3D 순차적 CMOS 인버터는 회로 시뮬레 이션을 위한 모델이 없다. 단지 트랜지스터 간의 높이가 비교적 큰 구조에 대하여 각각의 트랜지스터 모델을 가지고 회로를 시뮬레이션 한다. 하지만 트랜지스터 간의 높이가 작아지면 두 트랜지스터 간에 전기적 상호작용이 발생하고 이를 고려한 회로 시뮬레이션이 필요하다. 따라서 본연구에서는 전기적 상호작용을 고려한 3D 순차적 CMOS 인버터 회로 시뮬레이션 모델을 제시하고자 한다.

# Ⅱ. 본 론

#### 2.1 3차원 순차적 CMOS 인버터

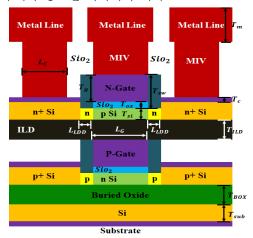

그림 1은 시뮬레이션에 이용한 3차원 순차적 CMOS 인버터의 기본 구조를 나타내고 있다. 하층 PMOS와 상층 NMOS로 이루어져 있으며 게이트 두께  $T_G$  =49 nm, 게이트 길이  $L_G$  =30 nm, 게이트 산화막 두께  $T_{OX}$  =1 nm, 실리콘 두께  $T_{Si}$  =10 nm, 사이드 월 두께  $T_{SW}$  =50 nm, LDD 길이  $L_{LDD}$

=10 nm, 컨택 두께  $T_{C}$  =50 nm, ILD 두께  $T_{ILD}$  =10 nm, 소스와 드레인(n+와 p+)은  $10^{21}$  cm<sup>-3</sup>, LDD(n과 p)는  $10^{19}$  cm<sup>-3</sup>, 채널(p-와 n-)은  $10^{15}$  cm<sup>-3</sup> 으로 도핑 하였다. 아래의 구조에서 게이트 길이와 ILD 의 두께가 중요한 파라미터 이다.

그림 1. 3차원 순차적 집적회로의 구조

#### 2.2 시뮬레이션 및 전기적 결과

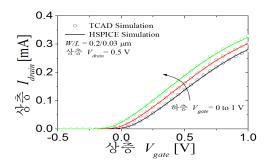

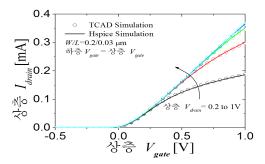

시뮬레이션은 Silvaco사의 디바이스 시뮬레이터 인 Atlas[4]를 이용하여 TCAD 데이터를 얻고, Synopsys사의 SPICE 시뮬레이터인 Hspice[5]를 이 용하여 SPICE 데이터를 얻어 비교하여 SPICE 모 델 파라미터 셋을 찾는 것이다. 시뮬레이션에 사 용된 SPICE 모델은 상층 NMOS에 BSIM-IMG, 하 층 PMOS에 LETI-UTSOI 이다.

그림 2는 상층 드레인 전압을 고정시키고 하층 게이트의 전압을 변화시켜가며 상층의 전류-전압 특성을 비교한 것이다.

그림 2. 상층  $V_{drain}$ =0.5 V 일 때 하층  $V_{gate}$ 에 따른 상층  $I_{ds}$ - $V_{gs}$  특성.

그림 3은 하층 게이트와 상층 게이트에 같은 전압이 가해질 때 상층 드레인 전압 변화에 따른 상층 전류-전압 특성을 비교한 것이다.

그림 3. 하층  $V_{gate}$  = 상층  $V_{gate}$  일 때 상층  $I_{ds}$ - $V_{gs}$  특성.

## Ⅲ. 결 론

본 연구에서는 트랜지스터 간의 높이가 작을 때 전기적 상호작용을 고려한 3D CMOS 인버터 회로 시뮬레이션 결과를 제시하였다. 상층 NMOS 에 BSIM-IMG, 하층 PMOS에 LETI-UTSOI 모델을 사용하여 하층 게이트에 전압이 가해졌을 때 전 기적 상호작용에 의한 상층 전류-전압 특성의 변 화가 반영된 것을 TCAD 데이터와 SPICE 데이터 를 비교하여 확인하였다. 하층 게이트 전압에 변 화에 따른 전기적 상호작용이 잘 나타나고 있으 므로 뵨 논문에서 제시하 BSIM-IMG와 LETI-UTSOI 모델을 사용하면 3D CMOS 인버터의 전기적 상호작용을 잘 반영할 것으로 보인다.

앞으로, 제시한 두 모델을 사용하여 DC 특성 및 커패시턴스, 과도응답 특성 등에 대하여 같은 시뮬레이션을 진행하여 전기적 상호작용이 잘 반 영되는지 확인하고자 한다.

# 참고문헌

- [1] P. Batude, *et al*, "Advances, challenges and opportunities in 3D CMOS sequential integration", in *Electron Devices Meeting* (*IEDM*), pp. 7.3.1–7.3.4, 2011.

- [2] A. M. Ionescu, H. Riel, "3DCoB: A new design approach for Monolithic 3D Integrated circuits", *Design Automation Conference (ASP-DAC)*, 19th Asia and South Pacific, pp. 79-84, 2014.

- [3] SILVACO, int. "ATLAS Users Manual", Santa Clara, CA, 2014.

- [4] Synopsys, Inc. "HSPICE® User Guide: Basic Simulation and Analysis", Mountain View, CA, 2016.