# 항공전자 장비 신뢰도 향상 방안 연구

서준호<sup>\*</sup> · 김영길<sup>\*\*</sup>

\*(주)한화시스템 · \*\*아주대학교

A Study on Reliability Improvement of Avionics Equipment

Joon-Ho Seo\* · Young-Kil Kim\*\*

\*Hanwha Systems · \*\*Ajou University

E-mail: joonho75.seo@hanwha.com

### 요 약

임베디드 시스템의 일종인 항공전자 장비는 높은 안전성과 신뢰도를 요구한다. 항공전자 장비 고장은 항공기 운용에 중대한 영향을 미칠 뿐만 아니라 최악의 경우에는 조종사와 승객의 인명 손실을 초래할 수도 있다. 본 논문에서는 항공전자 장비의 신뢰도를 높이기 위해 장비에 발생 가능한 고장을 사전에 감지할 수 있는 Built-In-Test(이하: BIT) 설계 기법과 장비의 Mean Time Between Failure (이하: MTBF)를 향상시킬 수 있는 설계 방법을 연구하고 실제 항공전자 장비에 적용하여 신뢰도를 향상시킨 사례를 소개한다.

#### **ABSTRACT**

Avionics, a type of embedded system, requires high safety and reliability. Failure of avionics equipment can have a significant impact on aircraft operations and, in the worst case, could result in loss of life for pilots and passengers. In this paper, we propose a Built-In-Test (hereafter referred to as BIT) design technique that can detect possible faults in avionics equipments in order to increase the reliability of avionics system and a design that can improve the Mean Time Between Failure (hereafter: MTBF) and applied it to real aviation electronic equipment to improve reliability.

항공전자, 신뢰도, 내장시험, 고장율

Avionics, Reliability, Built-In-Test, Failure Rate

## 1. 서 론

오늘날 많은 전자장비들이 항공기에 탑재된다. 2011년 조사에 따르면 전체 항공기 가격에서 항공전자 장비들의 비중은 이미 40%를 넘는 것으로 파악되고 있다.[1] 자동차의 경우에도 엔진 컨트롤 유닛, 네비게이션, HUD(Head Up Display)와 같은 전자장비 적용이 증대되고 있는데, 이들 전자장비들 중 상당수는 이미 항공기에서 적용되던 것들이다. 인공지능과 자동화가 대세인 오늘날의기술 추세에 따라 항공기와 자동차에 전자장비탑재 비중은 계속 늘어날 것이다. 항공기에 장착되는 대표적인 전자장비로는 임무컴퓨터, 다기능시현기, HUD, 비행제어컴퓨터, 레이더, 광학 센서, 모션/대기 정보 센서 등이 있으며, 이들 장비들은 서로 연동되어 항공전자시스템을 구성하게

된다.[2] 항공전자시스템은 항공기 자세제어, 항 법, 주변 상황 인식 및 임무통합관리 기능 등을 수행하는데 항공전자시스템을 구성하는 장비에 고장이 발생되면 항공기 운용에 중대한 영향을 미칠 뿐만 아니라 최악의 경우에는 조종사와 승 객의 인명 손실을 초래할 수 있다. 최신 항공기에 많이 적용되는 Fly-By-Wire 비행제어시스템을 예 로 들면 조종간을 통한 조종사의 명령은 전기 신 호로 변환되어 비행제어컴퓨터에 전달되고, 비행 제어컴퓨터가 항공기 조종면을 작동시키는 유압 작동기 명령을 직접적으로 생성한다. 즉 조종사 명령은 종래 기계식 링크 조종 장치와 달리 물리 적으로 조종면과 연결되어 있지 않기 때문에 비 행제어컴퓨터 고장 발생 시 조종사는 항공기 제 어권을 완전히 상실하게 되고, 결국 항공기는 자 세를 잃고 추락하게 된다.[3] 이에 본 논문에서는 항공전자 장비 고장에 의한 인명 손실을 최소화하고 항공전자 장비의 안전성과 신뢰성 향상을 위해 외부 점검 장비 도움 없이 전자장비 자체적으로 발생 가능한 고장을 감지할 수 있는 BIT 설계 기법을 연구한다. 또한 항공전자 시스템의 신뢰도를 높이기 위해 항공전자 장비의 고장률을 낮추는 설계 방법을 연구한다.

### Ⅱ. 본 론

항공전자 장비에서는 발생 가능한 고장을 사전 에 감지하고, 빠른 고장 탐지를 위해 3가지 종류 의 BIT을 구현한다. 항공전자 장비에 적용되는 BIT은 PBIT, CBIT, IBIT으로 구분된다. PBIT은 Power On BIT으로 장비에 전원이 인가 된 후, 정상 모드 동작(Normal Mode Operation) 전에 수행되어 장비에 이상이 없음을 확인한다. 일반 PC의 경우에도 Power On 시 Memory Check 등 을 수행하여 하드웨어 이상 여부를 확인하고 OS 부팅을 수행하는데 이 또한 PBIT의 일종이라고 할 수 있다. PBIT은 장비가 정상 모드 동작을 수 행하기 전에 시작되므로 CPU Test와 같이 정상 모드 동작 중 시험하기 힘든 하드웨어 체크를 용 이하게 수행할 수 있는 장점이 있다. 하지만 신속 히 정상 모드 동작을 수행할 필요가 있는 항공전 자 장비의 경우 PBIT 시간을 길게 할당할 수 없 으므로 시험 항목이나 시간에 제약이 있는 경우 가 많다.

CBIT은 Continuous BIT의 약자이다. CBIT은 Power On 이후 장비가 정상 모드 동작을 수행하는 기간 동안 주기적으로 실행되는 BIT 으로 장비가 Power Off 될 때 까지 수행된다. CBIT은 장비 동작 중 장비의 이상 유무를 주기적으로 점검하므로 정비에 고장 발생 시, 이를 즉시 발견할수 있는 장점이 있다. 하지만 CBIT 수행에 의해장비의 정상 모드 동작이 영향을 받으면 안 되므로, CBIT 동안 수행할 수 있는 시험 항목에 제한이 있다.

IBIT은 Initiated BIT의 약자이다. IBIT은 조종 사 또는 지상요원의 명령(Initiation)에 의해 수행된다. IBIT 모드에서 장비는 정상 모드 동작을 중지하고 Test 모드로 진입하게 된다. 그러므로IBIT은 시험 항목에 제한이 없으며 PBIT과 CBIT에 비해 상대적으로 긴 시간으로 시험을 수행할수 있게 된다. 통상 IBIT이 가장 높은 시험 커버리지를 가지게 된다. IBIT 에서 수행되는 Memory Test 의 경우 현재 CPU가 액세스 하지않는 Memory 영역을 검사하여 잠재적인 고장까지 발견할수 있는 장점이 있다. 조종사는 항공기이륙 전에 IBIT을 수행하여 항공전자 장비의 이상 유무를 확인하고 비행을 하게 된다.[4]

표 1은 항공전자 장비에 적용되는 BIT 시험 항목 및 실제 BIT 이 실행되는 시기를 나타내고 있다.

표 1. BIT 시험 항목

| 항목            | PBIT | CBIT | IBIT |

|---------------|------|------|------|

|               | 시 수행 | 시 수행 | 시 수행 |

| ADC Test      | X    | 0    | О    |

| UART Test     | X    | X    | О    |

| Memory Test   | О    | 0    | О    |

| Ethernet Test | X    | X    | О    |

| Power Test    | О    | 0    | О    |

| CPU Test      | О    | X    | О    |

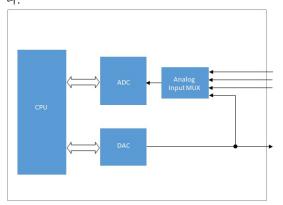

ADC Test는 Analog 입력 값을 Digital로 변환해 주는 Analog Digital Converter(이하: ADC) 칩의 이상 유무를 확인하는 시험이다. ADC 칩의 경우 산업용 또는 상용 컴퓨터에도 많이 적용되나 ADC 칩에 대해 BIT을 수행하는 경우는 많지 않다. 가장 손쉬운 ADC 칩의 시험 방법은 칩레지스터를 읽어 레지스터의 엑세스 가능 여부를확인하는 방법이다. ADC 칩이 작동 불가할 경우레지스터 엑세스가 되지 않는 경우가 많으며, 이경우 시험에서 ADC 고장을 판단 할 수 있다. 하지만 본 방법은 ADC 칩 기능의 일부에만 고장이발생 되었을 때 고장이 확인되지 않을 가능성도높기 때문에 항공전자 컴퓨터 시스템에서는 그림 1의 회로를 구성하여 ADC 칩을 시험하게 되었다.

그림 1. ADC-DAC Wraparound 회로

그림 1의 회로에서 Digital Analog Converter (이하: DAC) 출력 신호는 Analog Input MUX를 통해 ADC 로 입력된다. CPU에 의해 DAC 출력 값이 제어 되므로 ADC를 통해 입력될 값도 예측 가능하다. ADC 시험 수행 시 CPU는 예측되는 아날로그 입력 값이 정해진 허용 오차 범위 내에서 디지털로 변환되어 입력되는지 확인하여 ADC의 고장 유무를 판단하게 된다. 본 방법은 레지스터를 읽어 ADC를 시험하는 방식에 비해 복잡한하드웨어 설계를 요구하지만 실제 ADC를 작동시켜 BIT을 수행하게 되므로 ADC 칩의 고장 유무를 정확히 감지 할 수 있는 장점이 있다.

Power Test의 경우 항공전자 장비를 구성하는

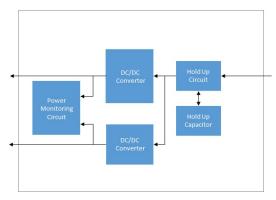

각 보드에 공급되는 3.3Vdc, 5Vdc, 12Vdc Power 의 전압 값을 모니터링 하게 된다. 모니터링 되는 전압 값이 허용오차 범위를 벗어나게 되면 BIT이고장을 선언한다. 항공전자 장비는 항공기 발전기에서 전원을 공급 받는다. 항공기 운용 중에는 Lightning 등의 원인에 의해 전원이 아주 짧은 시간 동안 단전 되거나 입력 전원이 불안정 할수 있는데, 이 경우 DC/DC 컨버터를 통해 각 보드에 공급되는 Power의 전압이 비 정상적으로 변경되어 정상적인 하드웨어 동작에 영향을 미칠수 있을 뿐만 아니라 항공전자 장비에 고장이 없는데도 Power Test 고장이 선언될 수 있다. 이에설계 개선을 위해 전원보드에 Hold Up 회로를 탑재하였다.

그림 2. 항공전자 장비 전원 보드 설계 사례

그림 2는 Hold Up 회로를 내장한 항공전자 장비 전원 보드 사례를 나타내고 있다. 대용량의 Hold Up Capacitor를 내장하여 순간적인 단전 및 전원 이상에 대해 커패시터가 대응하도록 설계 하였다. 다양한 외부 요인으로 항공전자 장비에 공급되는 전원에 50ms 정도 Interruption이 발생되어도 장비 내부를 구성하는 보드의 전원공급에 이상이 생기지 않도록 설계하여 BIT이 잘못된하드웨어 고장을 선언하지 않도록 하였으며 항공전자 장비의 운용 신뢰성을 향상 시켰다.

위에서 BIT 설계를 통해 항공기에서 발생 가능한 여러 고장을 항공기 이륙 전에 감지하여 항공전자 장비의 안전성과 운용 신뢰도를 높일 수 있음을 확인하였다. BIT 설계와 더불어 항공전자 장비에 고장 발생 확률을 감소시키는 설계를 적용한다면 항공전자 장비의 신뢰도를 더욱 향상 시킬 수 있다.

항공전자 장비는 많은 부품들로 구성되어 있다. 이들 부품의 고장은 항공전자 장비의 고장을 야기하는 중요한 요인이 되는데 설계 초기 단계부터 부품과 시스템 고장율(Failure Rate)을 고려하여 장비를 설계 한다면 신뢰성 높은 항공전자장비를 개발할 수 있다. 항공전자 장비의 신뢰도를 나타내는 수치 중 하나로 MTBF를 사용한다. MTBF는 평균 무고장 시간을 나타내는 수치로, 값이 높을수록 시스템의 고장 발생 빈도가 낮다

는 것을 의미한다. 항공전자 장비에 대한 MTBF 는 장비를 구성하는 모든 부품의 Failure Rate을 합하고, 이 값의 역수를 취해서 구할 수 있다.

MTBF 값을 향상시키기 위해서는 장비의 Failure Rate을 낮추어야 한다. 장비의 Failure Rate을 낮추기 위해 몇 가지 방법을 적용하여 항공전자 장비를 개발하게 되었다.

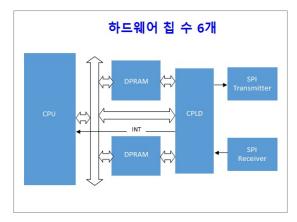

그림 3. CPU 보드 설계 변경 전

그림 3은 CPU, DPRAM, CPLD, SPI Transmitter와 Receiver로 구성된 CPU 보드 구성 다이어그램을 나타내고 있다. 총 6개의 부품이 사용된 사례로 CPU 보드의 Failure Rate은 다음과 같이 구할 수 있다.

CPU 보드 Failure Rate = CPU Failure Rate + (DPRAM Failure Rate \* 2) + CPLD Failure Rate + SPI Transmitter Failure Rate + SPI Receiver Failure Rate

CPU 보드의 Failure Rate을 낮추기 위해 기존 설계 안을 변경하여 FPGA를 적용하였다.

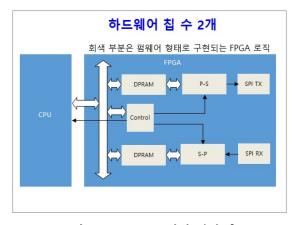

그림 4. CPU 보드 설계 변경 후

그림 4는 DPRAM과 SPI 관련 디바이스 등을 모두 FPGA 로직으로 구현하여 하드웨어 부품 수 를 줄인 형상으로 그림 3과 동일한 기능을 수행하는 CPU 보드이다. 본 CPU 보드의 Failure Rate은 다음과 같이 계산될 수 있다.

설계 변경 CPU 보드 Failure Rate = CPU Failure Rate + FPGA Failure Rate

그림 3, 4 보드에 대한 Failure Rate 계산에서 보드에 탑재되는 부품 수가 적을수록 전체 보드의 Failure Rate은 낮아질 확률이 높다고 판단할수 있다. 실제 하드웨어 설계 및 Relex라는 Failure Rate 계산 툴을 사용하여 확인한 결과 DPRAM, CPLD, FPGA 등 주요 IC 부품의 Failure Rate 값은 큰 차이가 없었으며, 부품 수가 적은 그림 4의 경우 보드의 Failure Rate 계산 값이 훨씬 좋아짐을 확인하였다.

전자 보드에 적용되는 Mechanical Switch 를 Buffer Chip으로 변경하여 Failure Rate을 개선할 수 있다.

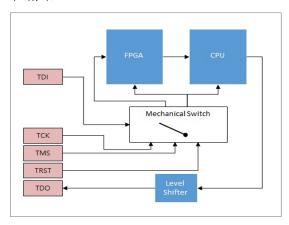

그림 5. CPU 보드 JTAG 설계 변경 전

그림 5는 DIP Switch를 적용하여 FPGA 또는 CPU JTAG을 선택하는 회로를 나타내고 있다. 본 회로에서 사용된 DIP Switch는 기계적 부품을 포 함하여 타 전자부품에 비해 높은 Failure Rate을 가진다.

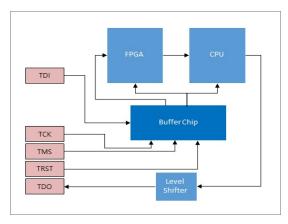

그림 6. CPU 보드 JTAG 설계 변경 후

그림 6은 Buffer Chip을 사용하여 DIP Switch 기능을 대신할 수 있도록 설계 변경을 한 회로를 나타내고 있다. Buffer Chip의 Failure Rate은 DIP Switch 대비 10배 정도의 좋은 수치를 보였 으며 설계 변경을 통해 CPU 보드 전체의 Failure Rate를 낮출 수 있었다.

### Ⅲ. 결 론

본 논문에서는 항공전자 장비에 적용되는 BIT 과 MTBF 향상을 위해 실제 항공전자 장비에 적 용된 설계 사례를 소개하였다.

BIT으로 수행되는 ADC Test와 Power Test의 경우 기존 설계방식을 개선하여 Wraparound 회로를 구성하고 Hold Up 회로를 추가하였다. 그결과 ADC Test의 경우 BIT 시험 커버리지를 증가시킬 수 있었으며, Power Test의 경우 잘못된고장 알람(False Failure Alarm)을 줄이고 장비의운용 안전성을 증가시킬 수 있게 되었다.

MTBF 향상을 위해 장비 레벨에서의 Failure Rate을 낮추는 설계를 적용하였다. 기존 유사 장비 설계를 개선하고 칩 수를 줄이기 위해 FPGA를 사용하였으며, 그 결과 IC 칩 수를 줄이고 Failure Rate을 낮출 수 있었다. DIP Switch와 같은 움직이는 Mechanical 구조로 설계된 부품은 타 IC 부품에 비해 Failure Rate이 높으며 이들 부품을 변경하는 설계를 적용할 경우 장비 전체의 Failure Rate을 낮출 수 있었다. 실제 항공전자장비 개발 사례에서 FPGA 적용 및 Mechanical Switch 변경 등을 통해 30% 정도의 MTBF 향상을 이루었다.

### 참고문헌

- [1] BIR Research Group, 비아이알, 항공 우주 산업 동향과 기술개발 전략, 203p, 2011

- [2] 한국과학기술정보연구원, 한국과학기술정보연구원 기술기회연구실, 미래 항공기의 핵심기술, 항공전자(Avionics) 경쟁환경 및 연구개발동향 분석, 14~20p, 2013

- [3] 박무혁, 한국항공우주연구원, 항공기 전기식 비행제어장치(FBW) 개발 기술동향, 24~27p, 2005

- [4] 김성우, 한국항공우주학회, 한국형 기동헬기 자체진단 시험 설계 및 입증, 623p, 2011