論文94-31A-12-17

# BiCMOS 선형 OTA

# (A BiCMOS Linear Operational Transconductance Amplifier)

朴志晚\*,蘇在煥\*,柳男圭\*,鄭元燮\*

(Ji-Mann Park, Jae-Hwan So, Nam-Kyu Ryu and Won-Sup Chung)

#### 要約

BiCMOS 선형 OTA를 설계했다. 설계된 OTA는 CMOS 트랜스컨덕터, 바이폴라 트랜스리니어 전류 이득셀, 그리고 세개의 CMOS 전류 미러로 구성된다.

설계된 회로의 선형성은 바이폴라 OTA에 필적한다. 그러나, 그것의 직류 특성은 바이폴라 OTA보다 우수하다. 47.3 등의 트랜스컨덕턴스를 갖는 측정 회로를 시뮬레이션한 결과,  $-1.0 \sim 1.0$  V 사이의 입력 전압 범위에서  $\pm 1\%$ 의 작은 선형 오차와 3.6nA보다 작은 출력 오프셋 전류가 얻어진다는 것을 알았다.

#### Abstract

Abstract—A linear BiCMOS operational transconductance amplifier (OTA) is described. It consists of a CMOS linear transconductor and a bipolar translinear current gain cell followed by three CMOS current mirrors. The proposed circuit has comparable linearity and temperature stability but superior dc characteristics to its bipolar counterpart. A test circuit with a transconductance of  $47.3\mu s$  has been simulated. Simulation results show that a linearity error of less than  $\pm 1$  percent over an input voltage range from -1.0 to 1.0 V and a output dc offset current as small as -3.6 nA can be obtained.

#### Introduction

Operational transconductance amplifiers (OTA's) are essential elements in the design of electrically tunable amplifiers, filters, oscillators, and current-mode signal

processing systems. There are two important limitations with the commercial OTA's, like the LM3080 and CA3080: one is their severe harmonic distortion for larger input signals caused by the nonlinear characteristic of the emitter-coupled differential input pair, the other is their temperature dependency caused by the temperature-sensitive transistor parameters. The simplest way of solving these problems is the use of the improved

\* 正會員,清州大學校 (Dept. of Semiconductor Eng., Chongju Univ.)

接受日字: 1993年 3月 25日

OTA's with on-chip diode linearization, like the LM13600 and CA3280. In order to achieve the improved performance with these devices, however, exactly matched resistors or elaborate trimming of a potentiometer is required. Recently, the other solution which does not suffer from such requirements has been reported. However, both circuits, being implemented with bipolar technology, exhibit a low input resistance and a large input bias current. In addition, it is difficult to adjust device parameters for maintaining a output dc offset current to within a desired low level. These factors result in limiting the usefulness of the circuits in dc applications.

In this paper, a BiCMOS linear OTA based on the bipolar linear OTA scheme <sup>15</sup> is presented. It features superior dc performance. The basic principle of the circuit is described in Section  $\[ \mathbb{I} \]$ . Its deviation from linearity under nonideal conditions is discussed in Section  $\[ \mathbb{I} \]$ . Simulation results are presented in Section  $\[ \mathbb{V} \]$ .

## 1. Circuit Description and Operation

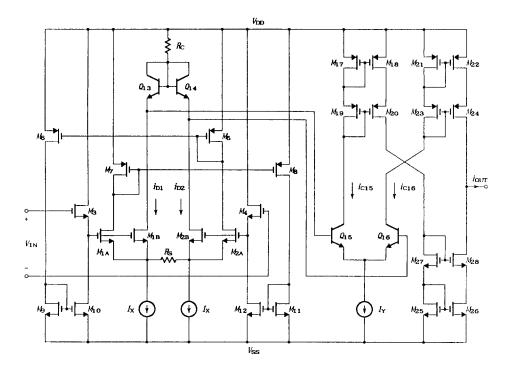

Fig. 1 shows the complete circuit diagram of the BiCMOS linear OTA. It consists of a linear transconductor formed by transistors  $M_1$  -  $M_{12}$ , a translinear current gain cell  $Q_{13}$  - $Q_{16}$ , and three cascode current mirrors  $M_{17}$  - $M_{28}$ . The transconductor converts the differential input voltage viv to its corresponding differential output currents  $i_{D1}$  and  $i_{D2}$ . Its operation can be explained as follows: For simplicity, we assume that all transistors are identical. Since the gate-source potentials of  $M_{1B}$  and  $M_{2B}$  are equal to those of  $M_{1A}$  and  $M_{2A}$ , respectively, we can write  $i_{D1B} = i_{D1A} = i_{D1}$ and  $i_{D2b} = i_{D2A} = i_{D2}$ . The drain current  $i_{D2A}$  is reproduced at the source of  $M_3$  through two current mirrors, formed by  $M_5$ ,  $M_6$ , and  $M_9$ ,  $M_{10}$ , respectively, to bias  $M_3$ . In the same manner,  $M_4$  is biased by the drain current  $i_{DA}$  which is reproduced at the source of  $M_4$ through two current mirrors: One is formed by  $M_7$  and  $M_8$  and the other by  $M_{11}$  and  $M_{12}$ .

Fig. 1. The circuit diagram of the BiCMOS linear OTA.

Summing the voltages around the loop consisting of the input voltage source, the four transistors  $M_1$ -  $M_2$ , and the source degeneration resistor  $R_{S}$ , we obtain

$$v_{IN} = \left(\sqrt{\frac{i_{D2}}{K}} + V_r\right) + \left(\sqrt{\frac{i_{D1}}{K}} + V_r\right) + R_s(i_{D1} - i_{D2}) - \left(\sqrt{\frac{i_{D2}}{K}} + V_r\right) - \left(\sqrt{\frac{i_{D1}}{K}} + V_r\right)$$

(1)

where

$V_i$  = threshold voltage

$$K = \frac{1}{2} \mu_n C_{ox} \left( \frac{W}{L} \right)$$

$\mu_n$  = electron mobility

$C_{ox}$  = channel capacitance per unit aarea

W =channel width

L =channel length

which gives

$$i_{D1} - i_{D2} = \frac{v_{IN}}{R_s} \tag{2}$$

Since the sum of  $i_{D1}$  and  $i_{D2}$  is  $I_X$ ,  $i_{D1}$  and  $i_{D2}$  will be given by

$$i_{D1} = \frac{I_x}{2} + \frac{v_{IN}}{2R_c} \tag{3a}$$

$$i_{D2} = \frac{I_x}{2} - \frac{v_{in}}{2R_s} \tag{3b}$$

The differential output currents  $i_{D1}$  and  $i_{D2}$  of the transconductor drive the diodeconnected bipolar transistor pair  $Q_{13}$  and  $Q_{14}$  of the translinear current gain cell. The current gain cell makes the current partitioning of the transistor pair  $Q_{13}$  and  $Q_{14}$  to be the mirror image of the current partitioning of the transistor pair  $Q_{15}$  and  $Q_{16}$ . Assuming that the four transistors are matched and their common-emmiter current gains are sufficiently large, one can write the following relation:

$$\frac{i_{D1}}{i_{D2}} = \frac{i_{C16}}{i_{C15}} \tag{4}$$

The output currents  $i_{C15}$  and  $i_{C16}$  of the current gain cell are differenced by three

current mirrors formed by  $M_{.7}$  –  $M_{20}$ .  $M_{21}$  –  $M_{24}$ , and  $M_{25}$  –  $M_{28}$ . respectively. Since the sum of  $i_{C15}$  and  $i_{C16}$  is  $I_Y$  and the difference is  $i_{OUT}$ , which denotes the single-ended output current of the OTA, currents  $i_{C15}$  and  $i_{C16}$  can be written as follows:

$$i_{C15} = \frac{I_{\gamma}}{2} - \frac{i_{OUT}}{2} \tag{5a}$$

$$i_{C16} = \frac{I_Y}{2} - \frac{i_{OUT}}{2}$$

(5b)

Combining (3a), (3b) and (5a), (5b) into (4), one can obtain

$$\frac{I_X}{2} + \frac{v_{IN}}{2R_s} = \frac{\frac{I_Y}{2} + \frac{i_{OUT}}{2}}{\frac{I_Y}{2} - \frac{i_{OUT}}{2}}$$

$$\frac{I_X}{2} - \frac{v_{IN}}{2R_s} = \frac{\frac{I_Y}{2} - \frac{i_{OUT}}{2}}{2}$$

(6)

which gives the transfer function of the OTA expressed as follows:

$$i_{OUT} = \frac{I_Y}{I_X} \frac{1}{R_c} v_{IN} \tag{7}$$

The transconductance  $G_m$  is given by  $(I_Y / I_X)(1/R_S)$ . It should be noted that in deriving (7) no numerical approximations have been made, and there are no temperature-dependent terms. Also, note that the transconductance of the OTA is determined by the ratio of the dc bias currents  $I_Y$  and  $I_A$

#### ■ Second-Order Effects

The discussion up to now has been based on the ideal transistor models. However, in reality, nonidealities such as finite  $\beta$  effect for bipolar transistors and body effect and channel-length modulation effect for MOS transistors are present. These nonidealities represent the sources of linearity errors and temperature coefficients of the OTA. These second-order effects are considered in this section

#### 1. Finite $\beta$ Effect

The subcircuit which contributes to this

effect is the current gain cell. In the presence of finite  $\beta$ , the transfer function of the OTA is modified so that

$$i_{OUT} \cong \frac{I_Y}{I_X} \frac{1}{R_s} \left( 1 - \frac{2}{\beta_N} \frac{I_Y}{I_X} \right) v_{IN}$$

(8)

where  $\beta_N$  is the common-emitter current gain of the npn transistors. The second term in the parenthesis represents the nonlinearity error in the transconductance against bias current ratio characteristics of the OTA.

#### 2. Channel-Length Modulation Effect

The influence of channel-length modulation on the transfer characteristic is mainly caused by the changes in  $v_{DS}$  of  $M_1$  and  $M_3$  when the voltage signal source is applied at the positive input terminal and the negative terminal is connected to ground. Analyzing the OTA with the transistor large-signal model which incorporates this effect, we can obtain the transfer function modified as follows:

$$i_{OUT} = \frac{I_{y}}{I_{x}} \frac{1}{R_{s}} \left[ 1 - \frac{\lambda_{N}}{2} \sqrt{\frac{I_{x}}{2K}} \left( \sqrt{1 + \frac{v_{NN}}{R_{s}I_{x}}} + \sqrt{1 - \frac{v_{NN}}{R_{s}I_{x}}} \right) \right] v_{NN}$$

(9)

where  $\lambda_N$  is a channel-length modulation parameter of the NMOS transistors. The second term in brackets represents the nonlinearity error in the transconductance against input voltage characteristic.

#### 3. Body Effect

In Fig. 1, only the input transistors  $M_1$  -  $M_4$  may contribute to this effect. However, since each of body terminals has made to be connected to their respective source terminals, one can find no body effect occurs.

## IV. Simulation Results and Discussion

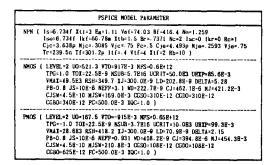

The circuit shown in Fig. 1 was simulated using SPICE. The SPICE model parameters for bipolar and MOS transistors are given in table 1. W/L = 120/12 was used for all MOS devices. The resistors used were  $R_{\rm S}$  = 40 rm 40 k

${\cal Q}$  and  $R_C=200{\rm k}{\cal Q}$ . The bais current  $I_X$  was set to 25 A for convenience. All measurements were performed at supply voltages of  $V_{DD}=10$  V and  $V_{SS}=-10$  V. The dc transfer characteristic of the simulated circuit for a fixed  $I_Y$  of 50 A is plotted in Fig. 2 as the dotted line. The linearity error relative to the straight line of slope  $G_m=47.3~\mu{\rm S}$  is also plotted. The nonlinearity is seen to be less than  $\pm 1$  percent over the input voltage range from -1.0 to 1.0 V.

Table 1. The SPICE model parameters for bipolar and MOS transistors.

Fig. 2. Transfer characteristics of the OTA.

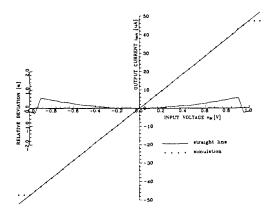

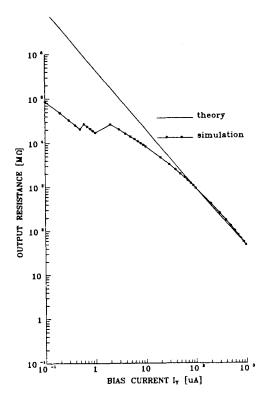

The relation between the transconductance and the bias current ratio was measured by fixing  $v_{IN}$  = 0.5 V and varying  $I_{Y}$  from 10 nA to 1 mA. The results are plotted in Fig. 3 and show that the transconductance is linearly dependent upon the bias current  $I_{Y}$  over the range of 0.01  $\sim$  100 $\mu$ A (four

decades) with a sensitivity of 1 S/A. The relation between the output resistance and the bias current  $I_Y$  is also measured. The results are plotted in Fig. 4.

Fig. 3. The transconductance against bias current ratio characteristic of the OTA.

Fig. 4. The output resistance against bias current ratio characteristic of the OTA.

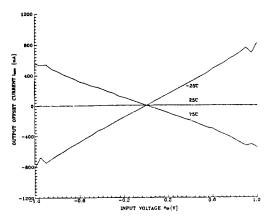

Fig. 5. Temperature characteristics of the OTA.

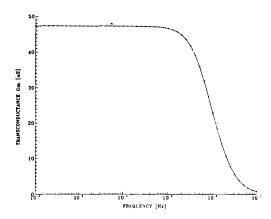

Fig. 6. Frequency characteristics of the OTA.

The dependency of output current on temperature was also simulated with a fixed  $I_{Y}$  of 50 A. The results are plotted in Fig. 5 in which output offset currents at -25°C and 75°C are estimated with reference to the output current at 25°C. The offset current is maintained to within ±16 nA/° over the entire input voltage range. The output dc offset current measured with  $I_{\rm Y} = 50$  A and grounded input terminals was -3.6 nA. This offset is about ten times lower than that of the bipolar OTA simulating under the same bias condition. Furthermore, if W/L = 107/12 is chosen for the  $M_{28}$  transistor, the output dc offset current can be reduced to -1.1 pA. The input dc current was found to be 0 A. The measured power consumption was 4.13 mW. Finally, the frequency characteristics of the OTA was investigated. The results are shown in Fig. 6. The measured 3-dB cutoff frequency was about 500 kHz.

#### V Conclusions

A BiCMOS OTA has been described. Its linearity and temperature stability are comparable to those of the bipolar counterpart. A significant advantage over the bipolar one is that the improved dc performance can be achieved by the appropriate choice of device dimensions. Therefore, the proposed BiCMOS OTA is expected to find wide applications in data conversion and precision measurement systems.

# Acknowlegment

This paper was supported by research fund of Inter-University Semiconductor Research Center in 1993.

#### REFERENCES

- [1] I. A. Khan and M. T. Ahmed, "Wide-range electronically tunable multi-functional OTA-C filter for instrumentation applications," *IEEE Trans. Instrum. Meas.*, vol. IM-36, pp. 13-17, March 1987.

- [2] W.-S. Chung and K. Watanabe, "A temperature difference-to-frequency converter using resistance temperature detectors," *IEEE Trans. Instrum. Meas.*, vol. IM-39, pp. 676-677, Aug. 1990.

- [3] W.-S. Chung, H.-W. Cha, and K.-H. Kim, "Temperature-stable VCO based on operational transconductance amplifiers," *Electron. Lett.*. vol. 26, pp. 1990-1901. Oct. 1990.

- [4] Linear Databook, National Semiconductor Corp., Santa Clara, CA, 1982.

- [5] W.-S. Chung, K.-H. Kim and H.-W. Cha, "A linear operational transconductance amplifier for instrumentation applications," *IEEE Trans. Instrum. Meas.*, vol. IM-41, pp. 441-443, June 1992.

著者紹介

Ji-Mann Park was born in 1967. He received the B.S. and M.S. degrees from Chongju University in 1989 and 1992. respectively. He is currently working towards the Ph.D. degree at the

same university. His research interests are Bipolar and CMOS IC design and sensor signal processing.

Jae-Hwan So was born in 1969. He received the B.S. degree from Chongju University in 1993. He is currently working towards the M.S. degree at the same university. His research

interests are integrated circuit design and application.

# 著 者 紹 介

Nam-Kyu Ryu was born in 1968. He received the B.S. degree from Chongju University in 1993. He is currently working towards the M.S. degree at the same university. His research

interests are integrated circuit design and application.

Won-Sup Chung was born in 1955. He received the B.S. and M.S. degrees from Hanyang University in 1977 and 1979, respectively. He received the Ph.D. degree from Shizuoka University,

Hamamatsu, Japan, in 1987. In 1986, he joined the Department of Semiconductor Engineering, Chongju University, where he is now an Associate Professor. His research interests include active-RC and switched-capacitor circuits for sensor signal processing.