# 저압 화학 기상 증착법으로 제작한 다결정 실리콘의 표면 형태 및 결정 성장

이 은 구·박 진 성·이 재 갑\*

조선대학교 재료공학과 501-759 광주시 동구 서석동 375 \*국민대학교 금속재료공학과

# Surface Morphology and Grain Growth of LPCVD Polycrystalline Silicon

Eun Gu Lee, Jin Seong Park, and Jae Gab Lee\*

Dept. Materials Science and Engineering, Chosun University

\*Dept. Metallurgical Engineering, Kookmin University

초 록 저압 화학 기상증착법으로 제작한 비정질 실리콘의 표면 형태 및 결정 성장 과정을 증착 조건과 열처리 조건의 변화에 따라 조사하였다. 비정질에서 결정으로 변화하는 전이온도인 570~590 ℃에서 증착한 시편은 (311)조직의 거친 표면으로 성장하였다. 같은 증착 온도에서 두께가 두꺼울수 록 다건정에서 비정질로 변화하였다. 증착하는 과정에서의 결정화는 기판에서부터 시작되지만, 진공 상태를 그대로 유지하고 비정질 실리콘을 전이온도에서 열처리하면 표면 실리콘 원자가 이동하여 결 정화하였다.

0

Abstract The surface morphology and grain growth of amophous silicon (a-Si) films deposited by low pressure chemical vapor deposition (LPCVD) have been investigated as a function of deposition and in situ annealing condition. The film deposited at the amorphous to polycrystalline transition temperature has an extra-rough, rugged surface with (311) texture. At the same deposition temperature, the grain structure tends to shift from the polycrystalline to the amorphous phase with increasing the film thickness. It is found that nucleation of a-Si during in situ annealing at the transition temperature without breaking the vacuum starts to occur from surface Si atom migration in contrast to a heterogeneous nucleation during film deposition.

#### 1. Introduction

Polycrystalline silicon (poly-Si) films formed by low pressure chemical vapor deposition(LPCVD) of silane (SiH<sub>4</sub>) are widely used in integrated circuits for various applications as MOS gates, interconects, resistors, and emitter contacts. Other applications include photovoltaic conversion, thermal and mechanical sensors, and thin film transistors (TFTs) for large area liquid crystal displays (LCDs). The electrical performance of the poly-Si is strongly determined by its microstructure, which depends on deposition parameters[1, 2].

Electrical properties of poly-Si formed under amorphous and polycrystalline phase have been investigated by a number of authors[3, 4]. It was suggested that deposition temperature should be as low as possible to obtain high conductivity and carrier mobility.

It is well known that the surface roughness of polysilicon degrades the electrical characteristics of dielectric film on the poly-Si[5, 6]. However, in order to get the sufficient storage capacitance required for 64M bit dynamic random access memory and beyond, some fabrication technologies having uneven surface of hemispherically grained(HSG) poly-Si film

have been suggested for increasing effective surface area [7, 8]. Solid phase growth (SPG) of amorphous silicon (a-Si) on a SiO<sub>2</sub> layer has been investigated with the a-Si film prepared by LPCVD, [9, 10] ultra-high vacuum (UHV) evaporation, [11, 12] and self-implantation [13-15] followed by the annealing for crystallization of the a-Si in vacuum or an inert ambient.

In this paper, we will present the experimental results of the grain growth of the LPCVD poly-Si followed by in situ annealing at the amorphous to crystalline transition temperature range without breaking the vacuum. In this experiment, it was found that the nucleation preocess during annelaing is different from that of deposition; grain growth starts to occur from surface silicon atom migration during in situ annealing, while grain growth starts from a nucleation on the substrate during deposition.

#### II. Experimental

The experiments were carried out in an induction heated hot wall horizontal reactor under 0.25 Torr. Undiluted SiH<sub>4</sub> gas as a silicon source was supplied from both sides of tube and was evacuated using a rotary pump. The starting wafers were CZ(100) p-type silicon, covered with 1000 Å thick SiO<sub>2</sub>. The thickness of poly-Si film, measured using ellipsometer, was approximately 1000 Å unless otherwise indicated. The surface morphology and microstructure were investigated using plane and cross sectional scanning electron microscope (SEM) and tranmission electron microscope (TEM).

The preferred orientation (texture) of the films was performed using x-ray diffractometer (XRD) with a glancing incident angle to reduce the penetration depth of x-rays and hence the diffraction from the substrated silicon. The texture of the films was measured by comparing the intensity of diffraction peaks with those obtained on random-

ly oriented polycrystalline film. In order to quantify the texture of the films, the relative unit(r.u<sub>hkl</sub>) for each diffraction plane {hkl} is normalized to {111} plane as follows.

$$\mathbf{u}.\mathbf{r}_{hkl} = \mathbf{I}_{hkl}/\mathbf{I}_{|||} \tag{1}$$

where,  $I_{hkl}$  and  $I_{lll}$  are intensities of {hkl} and {lll} planes, respectively.

The effective surface area of the film was determined from the capacitance values measured at 10kHz and 0 voltage with a HP 4275A LCR meter. The capacitor dielectric film consisted of 10 Å oxide/60 Å nitride film. The dielectric breakdown voltage was measured by taking I-V(current-voltage) curve with a HP 4145B semiconductor parameter analyser. The breakdown voltage was determined by the voltage at which current density reached 10  $\mu$  A/cm.

## III. Results and Discussion

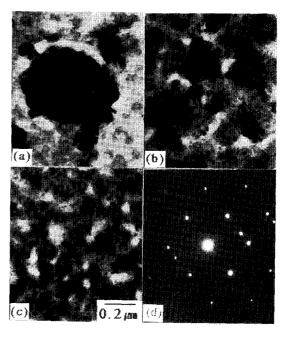

Figure 1 shows bright-field TEM photographs of the films deposited at various temperatures. Large grains and microcrystallites

Fig. 1. Bright-field TEM photographs of films deposited at (a) 570°C, (b) 580°C, and (c) 590°C, (d) the selected area diffraction (SADP) pattern of a).

were observed in the films deposited at 570°C. The films have large grains with {111} twin boundaries as shown in selected area diffraction pattern (SADP). It is found that with increasing the deposition temperature, the grain diameter decreases and the grain density increases due to the increase in number of nucle ation sites and crystallization rate. This results suggests that nucleation rate increases faster than grain growth rate as depositioin temperature increase.

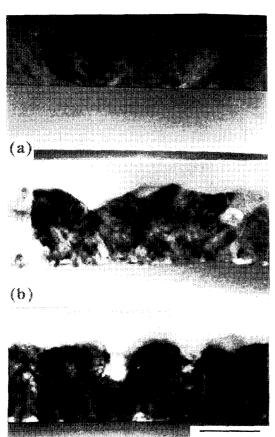

From the cross sectional TEM(X-TEM) photographs shown in Fig. 2, it was observed that

Fig. 2. X-TEM photographs of films deposited at (a) 570°C, (b) 580°C, and (c) 590°C.

(c)

100nm

small grains start to grow from the oxide substrate and a large grain protrudes from the a-Si surface at  $570^{\circ}\text{C}(a)$ . With increasing deposi-

tion temperature, many grain boundaries im pede lateral grain growth, resulting in a HSG growth at 580°C(b) and further increasing the temperature, resulting in cylindrical and/or co lumnar grain growht above 590°C(c) as observed by Lee *et al.* [4].

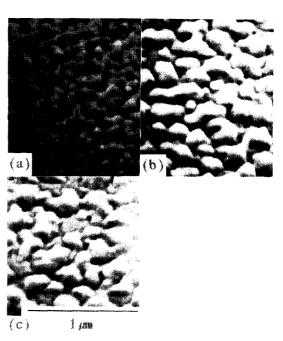

In order to examine an initial stage of the grain growth phenomena, the film thickness was varied. Figure 3 shows SEM photographs

Fig. 3. SEM photographs of films deposited at 580°C with (a) 500 Å (b) 1000 Å, and (c) 2000 Å thickness.

of 500, 1000, and 2000 Å thick films deposited at 580°C. Cylindrical grains were observed at 500 Å thick film, however, they disappered and both an amorphous film and hemispherical grains appeared in the 2000 Å thick film. With increasing film thickness, the surface morphology changes from cylindrical to hemispherical shape and the amorphous phase increases. From Figs. 2 and 3, it can be said that cylindrical grain is the nucleation step which appears in an early stage of films growth.

Crystal structures of the films were analyzed using XRD. Three x-ray diffraction peaks showing {111}, {110}, and{311} reflec-

tions were detected for the samples deposited at and above 570°C. Figure 4 shows the ratios of {110} and {311} intensity to {111} intensity as a function of deposition temperature. For a randomly oriented polysilicon film, the values of  $I_{\rm H0}/I_{\rm H1}$  and  $I_{\rm BH}/I_{\rm H1}$  are 0.6 and 0.35, respectively. The film deposited below 560°C is amorphous due to no detection of XRD peaks. It was observed that the {311} component dominated for the films deposited in the temperature range from 580°C to 600°C and the {110} component was a major peak for the films deposited above 620°C. The dramatic increase in {110} texture above 620°C implies that the preference for {110} texture is a growth phenomena rather than nucleation behavior. Comparing XRD data with film morphology, the undoped film deposited at the transition temperature has a rugged surface with small {311} texture.

Fig. 4. Relative unit of {110} and {311} intensity to {111} intensity as a function of deposition temperature.

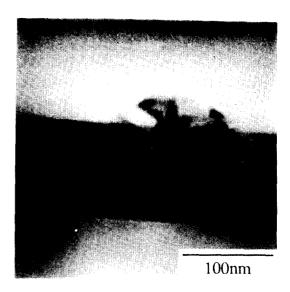

Although the surface morphology of as-deposited film is almost unchanged with subsequent annealing after exposuring in air, it is possible to change the morphology by *in situ* an-

Fig. 5. X-TEM photographs of films deposited at 560°C and *in situ* annealed at 570°C for 10min without breaking the vacuum.

nealing without breaking the vacuum. Figure 5 shows that X-TEM photographs of the film deposited at 560°C and annealed at 570°C for 10 min without breaking the vacuum. In contrast to grain growth from the substrate in Fig. 2, a large grain is observed on the surface in the amorphous phase and the surface sinks in around the grain and some microcrystallites are also observed on the substrate. The density of the hemispherical grains on the surface increases with increasing the annealing temperature and time. This result is in agreement with the result of A. Sakai et al.[6] obtained by the subsequent annelaing under UHV of  $1 \times 10^5$ Torr. Thery observed that mushroom-shaped grains are formed on the a-Si surface and protrude from the original a-Si plane. This result suggests that grain growth process during in situ annealing is different from a conventional solid phase growth; the grain growth starts to occur from surface Si atom migration during

in situ annealing, while grain growth starts from nuclei on substrate during deposition and a conventional solid phase growth. In case of the film deposited at 560°C and subsequent annealed at 570°C after exposing in air, nucleation occurs at the a-Si/SiO<sub>2</sub> interface and dendritic grain structure with flat surface is observed. It is believed that native oxide on the films exposed in air inhibits surface Si atom migration during the conventional solid phase growth.

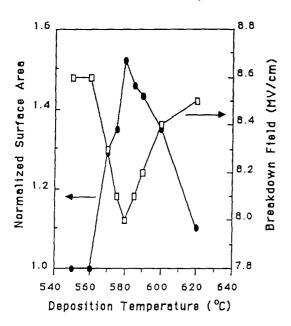

In order to calculate the increase in surface area of the polysilicon film and examine the degradation of dielectric film on the polysilicon film, effective surface area and breakdown field were measured from capacitance value and I-V characteristics of the capacitor dielec-

Fig. 6. Normalized surface area and breakdown field of capacitor dielectric film on polysilicon as a function of deposition temperature.

tric film, respectively. Figure 6 shows normalized surface area and breakdown field of capacitor dielectric film on polysilicon as a function of deposition temperature. It is found that the surface area of the film deposited at transition temperature is more than 1.5 times larger than even surface. The fact that breakdown

field of dielectric film slightly decreases with increasing the surface area is probably due to the increase in local electric field at the uneven surface. From the consideration of the enlargement of surface area and breakdown strength, uneven surface film deposited at transition temperature is suitable for further scaled DRAM device.

## IV. Conclusion

In summary, microstructure and grain growth of poly-Si films have been investigated as a function of deposition temperature, film thickness and subsequent annealing. Film deposited at amorphous to polycrystalline transition temperature has a rugged suface. At a fixed deposition temperature, the grain structure tends to shift from polycrystalline to amorphous phase with increasing the film thickness. Nucleation during deposition starts to occur from substrate, while nucletion during in-situ annealing at transition temperature without breaking the vacuum starts to occur from surface Si atom migration.

#### References

- T.I. Kammins, J. Electrochem. Soc., 127 (1980) 686

- G. Harbeke, L. Krausbauer, E.F. Steigmeier, A.E. Widmer, H.F. Kappert, and G. Neugebauer, J. Electrochem. Soc., 131 (1984) 675

- 3. M. Hendriks and C. Mavero, J. Electrochem. Soc., **138** (1991) 1466

- E.G. Lee and H.B. Im, J. Electrochem. Soc. 138 (1991) 3465

- T. Ono, T. Mori, T. Ajioka, and T. Takayashiki, IEEE IEDM Tech. Dig. (1985) 380

- S. Mori, Y. Kaneko, N. Arai Y. Ohshima,

H. Araki, K. Narita, E. Saka gami, and K.

Yoshikawa, IEEE IRPS Tech. Dig. (1990)

- M. Yoshimaru, J. Miyano, N. Inoue, A. Sakamoto, S. You, H. Tamura, and M. Ino,

- IEEE IEDM Tech. Dig. (1990) 659

- H. Watanabe, T. Tatsumi, T. Niino, A. Sakai, S. Adachi, N. Aoto, k. Koyama, T. Kikkawa, Ext. Abs. the 23rd Conf. SSDM (1991) 478

- E. Adachi, T. Aoyama, N. Konishi, T. Suzuki, Y. Okajima, and K. Miyata, Jpn. J. Appl. Phys., 27 (1988) L1809

- H. Watanabe, N. Aoto, S. Adachi, T. Ishijima, E. Ikawa, and K. Terada, Appl. Phys. Lett. 58 (1991) 251.

- H. Yamamoto, H. Ishiwara, and S. Furukawa, Jpn. J. Appl. Phys., 24 (1985)

411

- 12. Y. Kunii and Matsushita, and M.

- Kashiwagi, Jpn. J. Appl. phys., **21** (1982) 1.352

- Y. Ohyama, Y. Matsushita, and M. Kashiwagi, Jpn. J. Appl. Phys., 21 (1982)

L152

- R.B. Iverson and R. Reif, J. Appl. Phys.,

62 (1987) 1675

- A. Nakamura, F. Emoto, E. Fujii, Y. Uemoto, A. Yamamoto, K. Senda, and G. Kano, Jpn. J. Appl. Phys., 27(1988) L2408

- A. Sakai, H. Ono, K. Ishida, T. Niino, and T. Tatsumi, Jpn. J. Appl. Phys., 30 (1991) L941