# W Polymetal Gate Technology for Giga Bit DRAM

## Jong Wan Jung, Sang Beom Han, and Kyungho Lee

Abstract— W polymetal gate technology for giga bit DRAM are presented. Key module processes for polymetal gate are studied in detail.  $W/WN_x/poly$ -silicon adopted for a word line of 256Mbit DRAM has good gate oxide integrity and junction leakage characteristics through full integration, which is comparable to those of conventional  $WSi_x/Poly$ -silicon gate process. These results undoubtedly show that  $W/WN_x/poly$ -silicon is the strongest candidate as a word line for Giga bit DRAM.

Index Terms— semiconductor, DRAM, process integration, metal gate process, reliability.

## I. Introduction

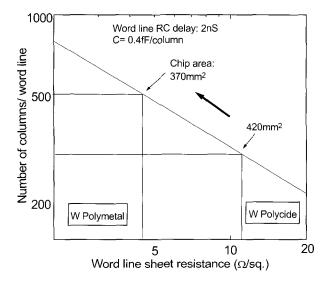

To reduce the chip area of 1Gbit DRAMs and beyond, reducing the area of peripheral circuits is essencial as well as reducing the size of each memory cell. Increased number of columns per word line allows the reduced number of peripheral circuit. Therefore, the RC delay due to the resistance of word line is a key factor to succeed in getting a smaller chip. Conventional W  $(WSi_x)$  or Ti polycide $(TiSi_x)$  have been adopted for 64M, 128M, and 256Mbit DRAM. For productive giga bit DRAM, the sheet resistance must be reduced to below 5  $\Omega$ /sq (Fig. 1) [1]. However, conventional polycide such as WSi<sub>x</sub> or TiSi<sub>x</sub> can not fully satisfy this requirement. When we simply increase the thickness of the stack structure with WSix or TiSix to reduce the sheet resistance, several issues occur, such as etch profile, BPSG void, and increased parasitic capacitance. Furthermore, sheet resistance of WSi<sub>x</sub> and TiSi<sub>x</sub> rapidly increases as the width of word line being decreased [2]. These several issues make the conventional polycide improper as a gate electrode for Giga bit DRAM

application.

**Fig. 1.** Dependence of affordable number of columns per word line under criteria of the word line RC delay is 2 ns and capacitance per word line is 0.4 fF [1].

On the contrary, W polymetal gate shows low sheet resistance even at very narrow line width(<0.1µm). Unlike W or Ti polycide, in case of W polymetal gate, a barrier metal layer is needed in order to prevent the forming of silicide layer which shows high contact resistance. Two representative candidates for W polymetal gate are W/WN<sub>x</sub>/poly-silicon and W/TiN<sub>x</sub>/poly-silicon, and some research works have shown electrical characteristics for them [3-5]. In the case of W/TiN<sub>x</sub>/poly-silicon, it has been known to be difficult to selectively reoxidize silicon without oxidizing Ti [6]. Therefore W/WN<sub>x</sub>/poly-silicon seems likely most promising technology for polymetal gate of Giga bit DRAM.

Our group has been developing 256Mbit and giga bit DRAM technologies with W/WN<sub>x</sub>/poly-silicon as a gate electrode, and recently the full integration has been presented for the first time [7]. In this paper, we will show the full integration technologies with W polymetal

Manuscript received February 10, 2001; revised March 12, 2001.

J. Jung and S. Han are with Hyundai Electronics Industries Co.. Ltd., 1 Hangjung-dong, Chungju, 361-725, Korea.(e-mail:jwanjung @hei.co.kr)

K. Lee is with Hongik University, Chochiwon, 339-701, Korea.

gate, which includes etching, cleaning, and selective oxidation process.

#### II. W POLYMETAL GATE TECHNOLOGIES

Full integration scheme for the polymetal gate process is shown in Fig. 2. Polymetal gate technologies can be mainly classified into four modules, which include the gate stack structure, gate etch, cleaning, and post reoxidation [8].

Gate oxidation (60 Å)

Gate stack deposition

- Poly-Si (700 Å)

- Barrier WNx (50 Å)

- W (700 Å)

- Capping SiNx (200 Å)

- Capping TEOS

Gate etch (W/poly-Si etch)

Post cleaning after gate etch

Pre cleaning prior to selective oxidation

Selective oxidation

Spacer SiNx deposition

**Fig. 2.** Process flows for W polymetal gate with the pre poly plug cell scheme technology.

#### A. Gate Stack

The gate stack consists of a gate electrode(W/WNx/poly-silicon) and the capping layers which are used for isolation and a hard mask for the gate etching. The gate electrode used in this paper consists of 700 Å/50 Å, W/WN<sub>x</sub> on top of 700 Å- n<sup>+</sup>-dope poly-silicon. A 50 Å thick WN<sub>x</sub> is used for a barrier film to prevent forming the W silicide between W and poly-silicon[9]. On the gate electrode, 200 Å thick SiN<sub>x</sub> film as a first capping layer was deposited for the blocking oxidation of W gate through the following processes. Then, about 3000 Å

thick SiO<sub>2</sub> film as a second capping layer was deposited on SiN<sub>x</sub> film. A suitable capping film should be chosen depending on the cell integration scheme. To make the self aligned contact process, SiN<sub>x</sub> film must be used for the capping and spacer layer. In our work, SiO<sub>2</sub> film was adopted for the pre poly plug(PPP) cell scheme[10]. In the PPP cell scheme, as a landing pad, poly-silicon is etched-out. The etch selectivity is high for SiO<sub>2</sub> compared to SiNx during poly-silicon etching. This is why SiO<sub>2</sub> layer is used in the PPP cell scheme. The stack structure is shown in Table 1.

**Table 1.** Gate stack structure applied for W/WN<sub>x</sub>/poly-silicon gate.

| Electrode     | Poly-Si/WNx/W                                                                                                                                                       |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Capping layer | <ul> <li>Capping layer1: SiNx 200 Å (for protecting W from oxidizing)</li> <li>Capping layer2: SiO<sub>2</sub> 3000 Å (In the case of SAC, SiNx is used)</li> </ul> |  |  |

| Spacer layer  | <ul> <li>Spaer1: SiNx (for protecting side W from oxidizing)</li> <li>Spacer2: SiO<sub>2</sub> (In the case of SAC, SiNx is used)</li> </ul>                        |  |  |

## B. Gate Etching

Etching of W polymetal (W/poly-silicon) is somewhat different from that of the conventional W polycide gate (WSix/poly-silicon). The basic difference comes from the etch chemistry. In the case of the conventional W polycide gate, Cl<sub>2</sub> based chemistry is used for etching both WSix and poly-silicon. On the contrary, for the W/poly-silicon gate, two kinds of chemistry should be used, which are SF<sub>6</sub>, CF<sub>4</sub> or NF<sub>3</sub> for W etching and Cl<sub>2</sub> for poly-silicon etching. This difference of the etching chemistry also makes the different etching procedure as shown in Table 2. It should be noted that the gate etch with the low damage is required not to degrade the retention time characteristics of DRAM [11].

#### C. Cleaning

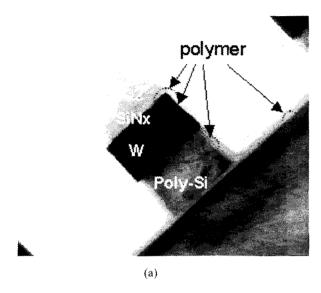

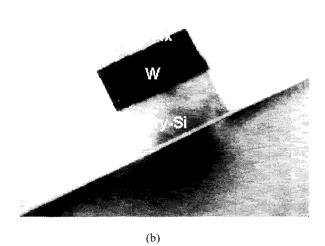

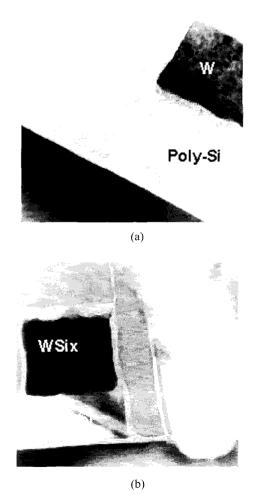

During the gate etching process, a lot of oxide polymer is usually formed, and these should be removed through cleaning (Fig. 3). Cleaning for W needs a special care because the W exposed on both sides of the gate edge can be easily damaged during the cleaning

|                   | WSix/poly-Si                                                                                     | W/poly-Si                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Gas Chemistry     | • WSix etch: Cl <sub>2</sub> base<br>• poly-Si: Cl <sub>2</sub> base                             | <ul> <li>W etch: SF<sub>6</sub>, CF<sub>4</sub>, NF<sub>3</sub></li> <li>poly -Si etch: Cl<sub>2</sub> base</li> </ul> |

| Etch process flow | <ul><li> WSix (EPD)</li><li> poly-Si (EPD)</li><li> Over Etch for poly-Si WSix/poly-Si</li></ul> | <ul> <li>W/WNx (EPD)</li> <li>Over etch of W/WNx</li> <li>poly-Si (EPD)</li> <li>Over etch for poly-Si</li> </ul>      |

Table 2. Comparison of etching process of conventional W polycide and W/WN<sub>x</sub>/poly-silicon gate.

(EPD: etch point detection).

Fig. 3. Cross sectional TEM view of gate electrode through gate etching (a) before cleaning (b) after cleaning. A lot of oxide polymer are shown before cleaning.

process. Cleaning solution which contains H<sub>2</sub>O<sub>2</sub> must be avoided because it easily damages W. In general, HF

or BOE is used. For pre-furnace cleaning, we adopted a mixture of H<sub>2</sub>SO<sub>4</sub> and deionized water to remove the impurities without damaging oxide and W.

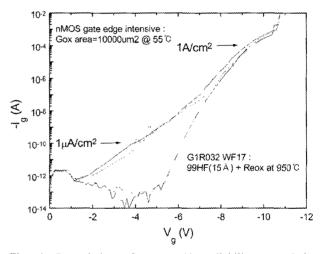

Fig. 4. Degradation of gate oxide reliability caused by insufficient post oxidation, which means the thickness of post oxidation should be thick enough to recover the thin oxide at gate edge.

## D. Post Oxidation (Selective Oxidation)

Post oxidation is needed to cure the damaged oxide during the gate etching and to increase the thickness of oxide at the gate edge. Also the gate oxide integrity can be degraded by the insufficient post oxidation. Fig. 4 shows the degraded the gate oxide integrity (GOI) characteristics caused by the insufficient post oxidation, which means the thickness of the post oxidation should be thick enough to recover the thinned oxide at the gate edge. Since W is easily oxidized at temperature above 350°C in the oxygen ambient, if W is oxidized, it swelled out, which results in the failure of circuits. Therefore post oxidation in the W/poly-silicon gate process should

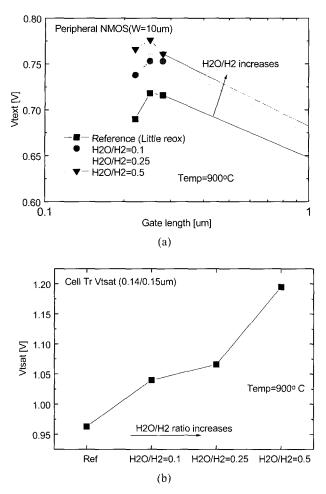

Fig. 5. Change of short channel effect of NMOSFET with  $H_2O/H_2$  ratio. (a) a peripheral NMOSFET and (b) a cell NMOSFET. Short channel effect decreases as  $H_2O/H_2$  ratio increases.

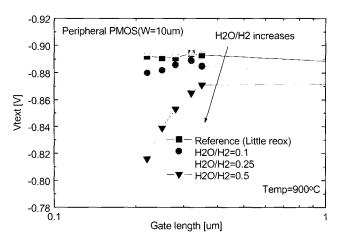

**Fig. 6.** Change of short channel effect of peripheral PMOSFET with  $H_2O/H_2$  ratio. The threshold voltage of PMOSFET slowly decreases at low  $H_2O/H_2$  ratio, but it abruptly decreases at 0.5 of  $H_2O/H_2$  ratio.

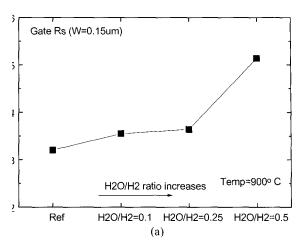

Fig. 7. Change of the sheet resistance of W polymetal gate with  $H_2O/H_2$  ratio. (a) The average and (b) uniformity value slowly increases at low  $H_2O/H_2$  ratio, but they abruptly increase at 0.5 of  $H_2O/H_2$  ratio.

selectively oxidize silicon without oxidizing W. Silicon can be selectively oxidized at the specific H<sub>2</sub>O/H<sub>2</sub> ambient [6]. In this work, the selective oxidation was performed using RTA in the optimized H<sub>2</sub>O/H<sub>2</sub> mixture ambient. From the device point of view, it should be noted that the post oxidation can severely change the device characteristics. Fig. 5 and 6 show the change of the device characteristics with the H<sub>2</sub>O/H<sub>2</sub> mixture ratio. It can be shown that the threshold voltage of the cell and pheripheral NMOSFET gradually increases as the H<sub>2</sub>O/H<sub>2</sub> ratio increases. On the contrary, the threshold voltage of PMOSFET gradually decreases at the low H<sub>2</sub>O/H<sub>2</sub> mixture ratio, however, it abruptly changes at 0.5 of the H<sub>2</sub>O/H<sub>2</sub> mixture ratio. This change of the short channel effect can be thought to be due to the oxidation enhanced diffusion(OED) of boron during the post oxidation. Buried channel PMOSFET is likely to be

more susceptible to the OED. The average and uniformity characteristics of the sheet resitance also shows the same tendancy (Fig. 7). It can be seen that the uniformity and average value of the sheet resistance also abruptly increases at 0.5 of the H<sub>2</sub>O/H<sub>2</sub> mixture ratio. These results present that the sufficient and high selective oxidation while maintaining good device characteristics is very important in the post oxidation for the polymetal gate process. Fig. 8 shows the TEM photograph of the W polymetal gate and the W polycide gate after the post oxidation (RTP and furnace are applied for the post oxidation of the polymetal gate and polycide gate, respectively.). After the post oxidation, a blocking SiN<sub>x</sub> film with the thickness of 100~200 Å was deposited for preventing the W gate exposed on edge sides from oxidizing.

**Fig. 8.** TEM photograph of W polymetal gate and conventional W polycide gate after post oxidation. W polymetal gate is oxidized by RTP at 900°C and W polycide gate is oxidized by furnace at 850°C.

### III. FULL INTEGRATION & CHARACTERISTICS

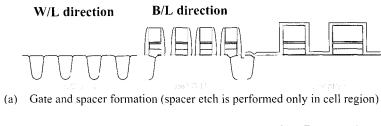

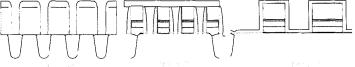

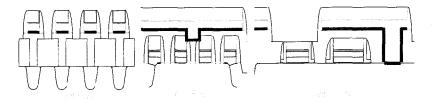

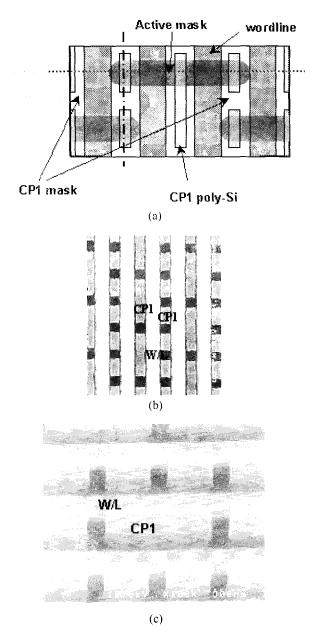

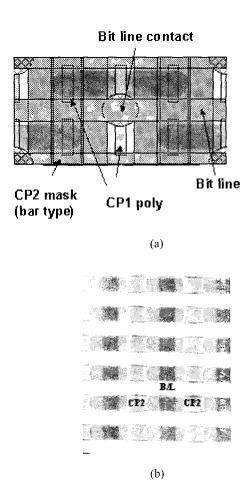

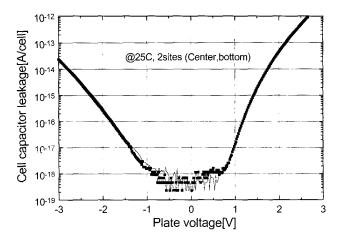

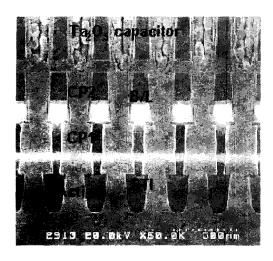

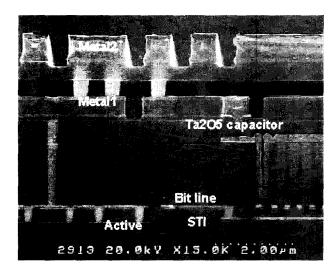

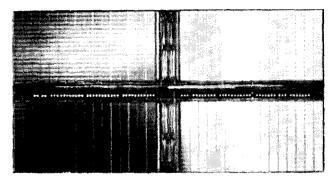

248nm KrF with high NA was applied for critical layers. The thickness of shallow trench isolation was 3000 Å and thin gate oxide (60 Å) was used to prevent the short channel effect of transistors. Tungsten (W) was adopted for both gate line and bit line, and the pre poly plug(PPP) scheme was applied for cell pads and storage contacts [10]. In order to achieve the high capacitance, MIS(metal insulator Si)-Ta<sub>2</sub>O<sub>5</sub> with the rugged type inner surface(inner cylinder) was used. Key technologies of 8F<sup>2</sup>, 0.15 µm 256Mbit DRAM were summarized in Table 3. Since the PPP technology forms poly plug ahead of the ILD formation, high selectivity oxide etch to nitride and ILD void problem in the self aligned contact (SAC) process can be basically avoided. Fig. 9 shows the schematic process flow of the PPP process. After the gate and SiNx/SiO<sub>2</sub> spacer formation, poly-silicon for landing pads was deposited and planarized using chemical mechanical polishing (CMP). CP1(Cell plug1, landing pad) was formed by the poly-silicon etching on the field area. Fig. 10 shows the mask pattern of CP1 and the SEM image after fabrication. After the bit lines stacked with barrier /W/oxide were patterned on an ILD layer, the oxide spacer was formed. Then, ILD layer between bit lines was additionally etched away until the top of CP1 polysilicon was exposed. CP2 (cell pad2, storage node contact) was patterned with the same procedure the CP1 formation. CP2 was separated by the deposition of ILD layer and CMP. Fig. 11 shows the mask pattern of CP2 and the corresponding SEM image after fabrication. As shown in Fig. 11, the PPP process has an advantage in the aspect of the CP2 process since the patterning for the line type CP2 is much easier than that of the conventional hole type in the SAC process. The typical capacitance characteristics of Ta<sub>2</sub>O<sub>5</sub> capacitor is 26~30 fF/cell. It exhibits good leakage characteristics, as shown in Fig. 12, which are 0.02 fA/cell and 0.3 fA/cell at 1.0 V and 1.26 V of the plate voltage, respectively. Fig. 13 and 14 show the cross sectional SEM images after full integration. Fig. 15 shows the photograph of a fabricated 256Mbit DRAM. One of the major concerns of the polymetal gate stack is the gate oxide reliability. Comparing the charge to breakdown(QBD) characteristics between the W polymetal gate and the

Table 3. Key technologies of 0.15µm-256Mbit DRAM with W polymetal gate.

| Lithography     | 248nm KrF, I line (PSM)                                       |

|-----------------|---------------------------------------------------------------|

| Isolation       | STI (3000 Å )                                                 |

| Gox             | 60 Å                                                          |

| WL              | $W/WN_x/poly-Si$ , $L/S = 0.14$ ц $m/0.15$ ц $m$              |

| ILD1(WL spacer) | TEOS (SiNx in the case of SAC)                                |

| Cell pads       | Pre Poly Plug(PPP) WL spacer +poly deposition +CMP+Etch       |

| Bit line        | W                                                             |

| Storage contact | PPP, BL spacer + poly deposition + Etch+ ILD3 deposition+ CMP |

| Cap dielectric  | $Ta_2O_5$                                                     |

| Plate           | TiN                                                           |

(b) CP1 poly Si deposition and CMP. CP1 pattern and etch

(c) ILD deposition and bit line contact formation

(d) CP2 poly-Si deposition and etch

(e) ILD deposition and CMP

Fig. 9. Process flow of cell formation using PPP(pre poly plug) scheme (W/L direction:A-A', B/L direction:B-B').

**Fig. 10.** (a) Schematic view of CP1 (cell pad) mask, (b and c) Planar SEM view of CP1 after fabrication.

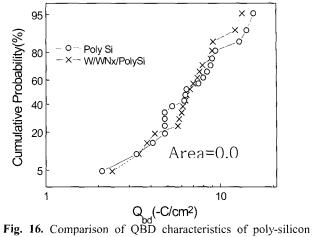

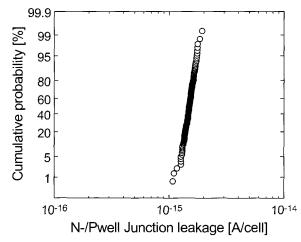

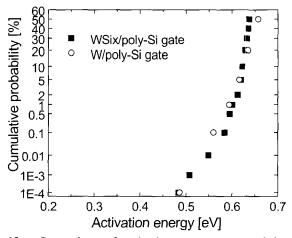

poly-silicon gate, as shown in Fig. 16, no difference was observed. Fig. 17 shows the comparison of n<sup>-</sup> to p-well cell junction leakage characteristics. The characteristics of W/WN<sub>x</sub>/poly-silicon are comparable to those of the conventional W polycide gate. Fig. 18 compares the activation energy measured by the retention time characteristics versus temperature. The activation energy with W polymetal gate cells is also comparable to that of the conventional W polycide gate cells. These results also exhibits that the contamination by W gate is not a significant problem in our integration technology.

**Fig. 11.** (a) Schematic view of CP2(storage node contact) mask (b) Planar SEM view of CP1 and CP2 after fabrication.

**Fig. 12.** Leakage characteristics of MIS(metal insulator Si)- $Ta_2O_5$  with rugged type inner surface(inner cylinder). The capacitor leakage is 0.02 fA/cell and 0.3 fA/cell at 1.0 V and 1.26 V of plate voltage, respectively.

**Fig. 13.** Cross sectional SEM view of CP1(cell pad) and CP2 (storage node) in the direction of word line.

**Fig. 14.** Cross sectional SEM image of core and peripheral area of fabricated device.

Fig. 15. Photograph of a fabricated 256Mbit DRAM.

**Fig. 16.** Comparison of QBD characteristics of poly-silicon gate and W/WN<sub>x</sub>/poly-silicon gate. They show comparable QBD characteristics.

**Fig. 17.** Comparison of N-/Pwell junction leakage haracteristics of W polymetal gate and W polycide gate. They show comparable leakage characteristics.

**Fig. 18.** Comparison of activation energy measured by retention time characteristics versus temperature. Activation energy of W/poly-silicon gate is also comparable to that of conventional WSix/poly-silicon gate.

#### IV. Conclusions

W polymetal gate technology for giga bit DRAM are presented. Key module processes for polymetal gate, which include etching, cleaning, and post oxidation are studied in detail. W/WN<sub>x</sub>/poly-silicon adopted for a word line of 256Mbit DRAM has good gate oxide integrity and junction leakage characteristics through full integration, which is comparable to those of conventional WSi<sub>x</sub>/Poly-silicon gate. These results undoubtedly show W/WN<sub>x</sub>/poly-silicon is the strongest candidate as a word line for Giga bit DRAM.

#### REFERENCES

- [1] Y. Hiura, A. Azuma, K. Nakajima, Y. Akasaka, K. Miyano, H. Nitta, A. Honjo, K. Tsuchida, Y. Toyoshima, K. Suguro, and Y. Kohyama, "Integration technology of polymetal dual gate CMOS for 1Gbit DRAMs and beyond," in *IEDM Tech. Dig.*, pp. 389-392, 1998.

- [2] Kinam Kim, "Perspectives on giga-bit scaled DRAM technology generation," *Microelectronics reliability* 40, pp. 191-206, 2000

- [3] B. H. Lee, D. K. Sohn, J. S. Park, C. H. Han, Y. J. Huh, J. S. Byun, and J. Kim, "In-situ barrier formation for high reliable W/barrier/poly-silicon gate using denudation of WNx on polycrystalline Si," in *IEDM Tech. Dig.*, pp. 385-388, 1998.

- [4] H. Wakabayashi, T. Andoh, K. Sato, K. Yoshisa, H. Miyamoto, T. Mogami, and T. Kunio, "Highly reliable W/TiN/pn-poly-silicon gate CMOS technology with simultaneous gate and source/drain doping process," in *IEDM Tech. Dig.*, pp. 447-450, 1996.

- [5] M. T. Takagi, K. Miyashita, H. Koyama, K. Nakajima, K. Miyano, Y. Aksaska, Y. Hiura, S. Inaba, A. Azuma, H. Koike, H. Yoshimura, K. Suguro, and H. Ishiuchi, "A novel 0.15µm CMOS technology using W/WNx/polysilicon gate electrode and Ti silidiced source/drain diffusions," in *IEDM Tech. Dig.*, pp. 455-458, 1996.

- [6] K. Ohinishi, N. Yamamoto, T. Uchino, Y. Hanaoka, T. Tsuchiya, Y. Nonaka, Y. Tanabe, T. Umezaya, N. Fukuda, S. Mitani, and T. Shiba, "Improving gate oxide intergrity (GOI) of a W/WNx/dual-poly SI stacked-gate by using wet-hydrogen oxidation in 0.14-μm CMOS devices," in *IEDM Tech Dig.*, pp. 397-400, 1998.

- [7] J. W. Jung, S. W. Lee, Y. G. Sung, B. H. Lee, J. H. Choy, B. J. Lee, R. H. Park, and S. B. Han, "A fully working 256Mbit DRAM technology with polymetal (W/WNx/polysilicon)gate," in *IEDM Tech. Dig.*, pp. 365-368, 2000.

- [8] Jong-Wan Jung, S. W. Lee, Y. K. Sung, B. H. Lee, M. H. Lim, H. S. Kim, J. H. Choy, B. J. Lee, N. H. Park, and S. B. Han, "Polymetal (W/WN<sub>x</sub>/poly-silicon) gate technology in 256 MDRAM and beyond," in *Semicon Korea technical symposium*, pp. 407-411, 2001.

- [9] K. Nakajima, Y. Akasaka, K. Miyano, M. Takshashi. S. Suehiro, K. Suguro, "Formation mechanism of ultrathin WSiN barrier layer in a W/WNx/Si systen," *Applied surface science*, 117/118, pp. 312-316, 1997.

- [10] T. H. Yoon, K. C. Joung, J. H. Kim, W. C. Cho, W. Y. Yang, and D. H. Song, "A new process integration-P3(pre poly plug)-for Giga bit DRMA era," in *Symp. on VLS1 Tech. Dig.*, pp. 37-38, 1999.

- [11] Jong-Wan Jung, Y. G. Sung, S. H. Lee, S. W. Park, J. H. Choy, and B. J. Lee, "Impact of gate etch on retention time of DRAM with polymetal gate," in δ<sup>th</sup> Korean conference on semiconductor, pp. 681-682, 2001.

Jong-Wan Jung received the B.S. degree from Kyung-Pook University, and the M.S. and Ph.D. degrees from KAIST, in 1991 and 1996, respectively, all in electrical engineering. He joined LG semicon. in 1996, where he was engaged in the R&D of CMOS logic devices. Since 1999, he has been

researching DRAM devices in memory R&D division, at Hyundai electronics industries.

Sang Beom.Han received his B.S in ceramic engineering from Yonsei University, Seoul, Korea and his Ph.D. in materials science and engineering from Stevens Institute of Technology, New Jersey, USA. He is director of the DRAM product development at Hyundai electronics industries.

**Kyungho Lee** received the B.S. degree in electronics engineering from Seoul National University in 1984 and the M.S. and Ph.D. degrees in electrical engineering from the University of Minnesota in 1990 and 1993, respectively. From 1984 to 1988 and 1993 to 1999, he was with LG Semicon

Co., Ltd., in Korea, where he worked on the development of DRAM. In 2000 he joined the faculty of electronics engineering at Hongik University, Chochiwon, Korea. His present research areas include new processes, devices, and circuit developments and modeling based on silicon, both for high density memory and RF IC