# A New Two-Dimensional Model for the Drain-Induced Barrier Lowering of Fully Depleted Short-Channel SOI-MESFET's

S. Jit, Prashant Pandey, and B.B.Pal

Abstract - A new two-dimensional analytical model for the potential distribution and drain-induced barrier lowering (DIBL) effect of fully depleted short-channel Silicon-on-insulator (SOI)-MESFET's has been presented in this paper. The two dimensional potential distribution functions in the active layer of the device is approximated as a simple parabolic function and the two-dimensional Poisson's equation has been solved with suitable boundary conditions to obtain the bottom potential at the Si/oxide layer interface. It is observed that for the SOI-MESFET's, as the gate-length is decreased below a certain limit, the bottom potential is increased and thus the channel barrier between the drain and source is reduced. The similar effect may also be observed by increasing the drain-source voltage if the device is operated in the near threshold or sub-threshold region. This is an electrostatic effect known as the drain-induced barrier lowering (DIBL) in the short-gate SOI-MESFET's. The model has been verified by comparing the results with that of the simulated one obtained by solving the 2-D Poisson's equation numerically by using the pde toolbox of the widely used software MATLAB.

Index Terms—SOI-MESFET, threshold voltage, potential distribution, channel barrier, drain-induced barrier lowering (DIBL).

E-mail: sjit@bhu.ac.in, prashant\_15\_03@rediffmail.com, bbpaul@bhu.ac.in

#### I. Introduction

Si-MESFET fabricated on silicon-on-insulator (SOI) has drawn considerable attention in recent years due to its possibility as a good replacement of MOSFET for ULSI technology. The I-V characteristics of SOI-MESFET was first investigated experimentally by Vogt et.al.[1] but they overlooked the short-channel effects of such devices. The drain-induced barrier lowering (DIBL) is the most pervasive effect in short-channel devices which arises from the two-dimensional electric field distribution in FET's. DIBL is an electrostatic effect that causes the channel charge and current of short-channel FET's to be partially controlled by the drain potential rather than the gate potential. Thus, in order to understand and optimize the device characteristics with dimensions in the deep submicrometer regime, there is a need to develop an analytical model for the twodimensional potential distribution functions by solving the two-dimensional Poisson's equation.

Hou and Wu [2] have reported a model for the two-dimensional distribution function and threshold voltage of SOI-MESFET's by using the Green function technique. Recently, Chang et al.[3] have presented another analytical model for the same by using superposition method. Despite the accuracy of the above models, it involves a lot of mathematical complexity and makes its understanding and application difficult. In this paper, we have presented a simple analytical model for characterizing the DIBL in short-channel SOI-MESFET's. The potential distribution function is approximated as a parabolic function as considered in ref.[4] for the SOI-MOSFET's and consequently the

Manuscript received July 18 2003; revised November 4, 2003. Authors are with Department of Electronics Engineering Institute of Technology Banaras Hindu University Varanasi-221005, INDIA Tel: +91-542-2307014

bottom potential function at the active/oxide layer interface has been obtained by solving the two-dimensional Poisson's equation with suitable boundary conditions. The bottom potential is used to monitor the DIBL in the short-channel SOI-MESFET's. Finally, the proposed model has been verified by comparing the result with the simulated one obtained by solving the 2-D Poisson's equation using the pde toolbox of the widely used software MATLAB. A good agreement has been obtained between the two results.

### II. THEORETICAL MODEL

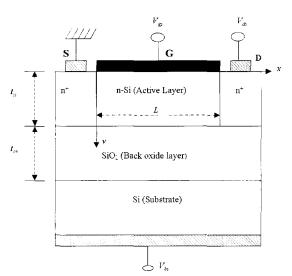

The schematic structure of a fully depleted SOI-MESFET under consideration has been shown Fig.-1. Assuming a uniform impurity doping density in the channel region, the two dimensional potential distribution  $\Psi(x, y)$  in the fully depleted silicon film may be obtained by solving the 2D Poisson's equation given by

$$\frac{\partial^{2} \Psi(x, y)}{\partial x^{2}} + \frac{\partial^{2} \Psi(x, y)}{\partial y^{2}} = -\frac{qN_{d}}{\varepsilon_{si}}$$

$$0 \le x \le L, \ 0 \le y \le t_{si}$$

(1)

Fig. 1. Schematic structure of n-channel Si-SOI MESFET's. The 2-D potential function  $\Psi(x,y)$  is obtained by solving the Poisson's equation inside the rectangular domain  $0 \le x \le L$ ,  $0 \le y \le t_{si}$ .

where  $N_d$  is the doping density,  $\varepsilon_{st}$  is the permittivity of the silicon film, L is the length of the channel, and  $t_{st}$  is the thickness of the silicon film. From the simulation results as reported in refs.[2,3], it is observed that the y-dependence of  $\Psi(x,y)$  may be approximated by a simple parabolic function as considered in ref.[4] for the SOI-MOSFET and may be given by

$$\Psi(x, y) = k_0(x) + k_1(x) y + k_2(x) y^2$$

(2)

where  $k_0(x)$ ,  $k_1(x)$  and  $k_2(x)$  are the functions of x. This approximation differs from the one proposed by Toybe and Asai [5] for the bulk-silicon MOSFET case, which employs a cubic function of y. The boundary conditions for solving the Poisson's equation (see eqn.(1)) may be given as [2]:

$$\Psi(x,y)\big|_{y=0} = V_{gs} - \Phi_{bi}$$

(3)

$$\Psi(x,y)\big|_{y=t_{Si}} = \Psi_{bp}(x) \tag{4}$$

$$\left. \frac{\partial \Psi(x, y)}{\partial y} \right|_{y=t_{si}} = \frac{\varepsilon_{ox}}{\varepsilon_{si}} \cdot \frac{V_{bs} - V_{fb} - \Psi_{1d}(y)|_{y=t_{si}}}{t_{ox}}$$

$$=\alpha (say) (5)$$

$$\Psi(x,y)\big|_{x=0} = V_{bi} \tag{6}$$

$$\Psi(x,y)\Big|_{x=L} = V_{bi} + V_{ds} \tag{7}$$

where  $V_{gs}$  is the gate-source voltage,  $V_{ds}$  is the drain-source voltages,  $\Phi_{bi}$  is the built-in voltage of the Schottky barrier at gate,  $V_{bi}$  is the built-in voltage between the channel to source (drain) junction,  $V_{bs}$  is the substrate bias,  $V_{fb}$  is the flat band voltage of SiO<sub>2</sub>,  $\varepsilon_{ax}$  is the permittivity of the oxide layer,  $t_{si}$  is the thickness of the active silicon film and  $t_{ax}$  is the thickness of the back oxide layer.  $\Psi_{bp}(x)$  is the bottom potential at the silicon and oxide layer interface and  $\Psi_{td}(x)$  in eqn.(5) is the one dimensional potential distribution for long channel SOI-MESFET which may be given by [3]

$$\Psi_{1d}(y) = -\frac{qN_d y^2}{2\varepsilon_{si}} + a y + V_{gs} - \Phi_{bi}$$

(8a)

where

$$a = E_{y}\Big|_{x=L/2,y=0}$$

$$= \frac{c_{ov}\left(\left(V_{hv} - V_{fh} + \left(qN_{d}t_{v}^{2}/2\varepsilon_{v}\right) - V_{gv} + \Phi_{hv}\right)/t_{v}\right) + qN_{d}}{c_{v} + c_{ov}}$$

(8b)

is the electric field at x = L/2, y = 0;  $c_{ox} = \varepsilon_{ox}/t_{ox}$  is oxide capacitance per unit area and  $c_{si} = \varepsilon_{si}/t_{si}$  is the capacitance of the silicon film per unit area.

Using eqns.(3)-(5) in eqn.(2), we get

$$\Psi(x,y) = \left(V_{gs} - \Phi_{bi}\right) + \left(\alpha + \frac{2\left(\Psi_{bp}(x) - V_{gs} + \Phi_{bi} - \alpha t_{si}\right)}{t_{si}}\right)y + \left(\frac{V_{gs} - \Phi_{bi} + \alpha t_{si} - \Psi_{bp}(x)}{t_{si}^{2}}\right)y^{2}$$

$$(9)$$

Substituting  $\Psi(x,y)$  from eqn.(9) in eqn.(1) and putting  $y = t_{si}$  in the resultant equation, we may express the bottom potential  $\Psi_{bp}(x)$  in terms of a differential equation given by

$$\frac{\partial^{2} \Psi_{hp}(x)}{\partial x^{2}} - \left(\frac{2}{t_{si}^{2}}\right) \Psi_{hp}(x)$$

$$= -\left(\frac{qN_{d}}{\varepsilon_{si}} + \frac{2(V_{gs} - \Phi_{hi} + \alpha t_{si})}{t_{si}^{2}}\right) \tag{10}$$

Using the boundary conditions from eqns.(6) and (7), the solution of eqn.(10) may be given by

$$\Psi_{bp}(x) = \Phi_D \sinh\left(\sqrt{2} x/t_{si}\right) + \Phi_S \cosh\left(\sqrt{2} x/t_{si}\right) + \beta$$

(11)

where

$$\beta = \frac{c_{si} \{ (qN_d t_{si}^2 / 2\varepsilon_{si}) + V_{gs} - \Phi_{bi} \} + c_{ox} (V_{bs} - V_{fb})}{c_{ox} + c_{si}}$$

(12)

$$\Phi_{S} = V_{bi} - \beta \tag{13}$$

$$\Phi_{D} = \frac{V_{ds} + \Phi_{S} \left( 1 - \cosh \left( \sqrt{2} L / t_{si} \right) \right)}{\sinh \left( \sqrt{2} L / t_{si} \right)}$$

(14)

Substituting the expression of  $\Psi_{hp}(x)$  from eqn.(11) in eqn.(9), we may get the expression for the two-dimensional potential distribution function for the short-channel SOI-MESFET's.

The DIBL effect of the short-channel SOI-MESFET's may be demonstrated by observing the bottom potential  $\Psi_{hp}(x)$ . Since the subthreshold leakage current often occurs at the position of the minimum channel bottom potential, the effect of DIBL on the device behavior in the subthreshold region may be monitored by the minimum bottom potential  $\Psi_{min} = \Psi_{hp}(x = x_{min})$

where  $x_{min}$  is the position of the minimum bottom potential which may be obtained by solving the equation:

$$\left. \frac{d\Psi_{bp}(x)}{dx} \right|_{x=x_{\min}} = 0 \tag{15}$$

and may be given by

$$x_{\min} = \left(t_{si} / \sqrt{2}\right) \tanh^{-1} \left(-\Phi_D / \Phi_S\right)$$

(16)

Note that, for

$$V_{ds} = 0$$

,  $-\Phi_D / \Phi_S = \tanh(L / \sqrt{2} t_{ss})$

(see eqn. (14)) and thus  $x_{\min} = \frac{L}{2}$ , i.e. the minimum bottom potential occurs at the middle of the channel. Since  $\tanh(x)$  is decreased as x is decreased, therefore, for  $V_{ds} = 0$ , if the channel length L is decreased, the term  $(-\Phi_D/\Phi_S)$  of eqn.(16) is also decreased and hence the position of the minimum bottom potential  $x_{\min}$  is shifted toward the source side. Further, from eqn. (14), it may be observed that if the  $V_{ds}$  is increased,

$-\Phi_D$  is decreased and thus for a fixed channel length,  $x_{\min}$  is decreased and shifts toward the source.

## III. RESULTS AND DISCUSSIONS

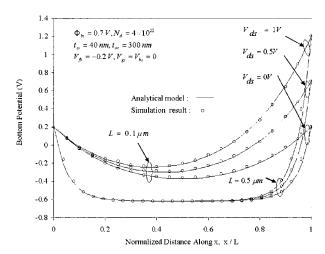

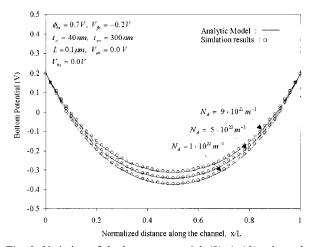

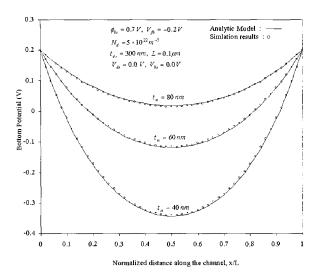

In this section, we have presented some numerical results for the bottom potential at the Si/oxide layer interface to demonstrate the DIBL effect in shortchannel Si-SOI MESFET's. In Fig.2, the variation of the bottom potential along the channel with a gate length  $L = 0.5 \mu m$  and 0.1  $\mu m$  has been shown for different drain-source voltages. From the figure, it is observed that as the drain - source voltage  $V_{ds}$  is increased, the bottom potential is increased at the drain side whereas the position of the minimum potential remains almost unchanged for  $L = 0.5 \mu m$ . This is due to the fact that for  $\sqrt{2}L/t_{si} \ge 4$ ,  $\Phi_D \approx V_{ds} \exp\left(-\sqrt{2} L/t_{si}\right) - \Phi_S$  (using  $\sinh(x) \approx \cosh(x) \approx \frac{1}{2} \exp(x) [5]$  in eqn.(14)). Since the exponential term is very small for  $L = 0.5 \mu m$  and  $t_{ci} = 40nm$ , therefore, from eqn.(16), it may be observed that  $x_{\min}$  is almost independent of the  $V_{ds}$ . The increase in the bottom potential at the drain side due to the increase in  $V_{ds}$  lowers the channel barrier (i.e. potential difference between the channel and source) of the device which is known as the DIBL in the short channel FET's. It is to be noted from the figure that as the channel length is decreased from  $L = 0.5 \mu m$ to 0.1  $\mu m$ , the DIBL effect becomes more dominant i.e. as the channel length is reduced, the bottom potential is increased and thus the channel barrier is lowered. In this case,  $x_{min}$  is shifted toward the source as  $V_{ds}$  is increased. The graph of the bottom potential vs. the normalized channel distance for different doping concentration in the silicon film is presented in Fig.-3. It is observed from the figure that the DIBL effect is increased with the increase in the doping concentration. Finally, the variation of the bottom potential along the channel is presented for different thickness of the silicon film as shown in Fig.-4. It may be observed that as the silicon film thickness is decreased, the DIBL effect is

reduced. Thus, if the channel length is reduced, the short-channel effect may be minimized by reducing the thickness of the active layer of the device. The result has been compared with the simulated one obtained by solving the 2-D Poisson's equation by using the pde toolbox of the widely used software MATLAB and a fairly good agreement is observed between the two. It may be mentioned that the boundary conditions described by eqns.(3)-(7) are the key requirements for solving the 2-D Poisson's equation numerically using MATLAB. Since, the above boundary conditions are already verified by Chiang et.al.[3], the comparison

Fig. 2. Variation of the bottom potential  $\Psi_{hp}(x/L)$  along the channel with normalized distance (x/L) for different gate lengths (L) and drain-source voltages  $(V_{ds})$ .

**Fig. 3.** Variation of the bottom potential  $\Psi_{hp}(x/L)$  along the channel at the Si-SiO<sub>2</sub> interface with normalized distance x/L for different doping concentration.

Fig. 4. Variation of the bottom potential  $\Psi_{hp}(x/L)$  along the channel at Si-SiO<sub>2</sub> interface with normalized distance x/L for different silicon-film thicknesses.

between the data obtained from our proposed model and simulation results obtained from the MATLAB is sufficient to show the validity of the analytical model described in this paper.

## IV. CONCLUSION

A new two-dimensional analytical model for the potential distribution and the drain-induced barrier lowering (DIBL) effect in short-channel SOI-MESFET is presented in this paper. The variation of the bottom potential at the active/oxide layer interface is determined to monitor the DIBL. It has been shown that as the channel length is reduced, the minimum bottom potential is increased which further reduces the channel barrier. If the drain-source voltage is increased, the position of the minimum bottom potential is shifted toward the source. The model presented in this paper is very simple as compared to the other reported models in the literature and may be used to predict accurately the channel barrier variation with the gate and drain voltages in the subthreshold regime including DIBL effects.

## REFERENCES

[1] H. Vogt, G. Burbach, J. Belz, and G. Zimmer,

- "MESFET's in thin silicon on SIMOX," *Electron Lett.*, vol.25, no. 23, pp.1580-1581, 1989.

- [2] Chin-Shan Hou, and Ching-Yuan Wu, "2-D analytic model for the threshold-voltage of fully depleted short gate-length Si-SOI MESFET's," *IEEE Trans. Electron Devices*, vol.42, no.12, pp.2156-2161, 1995.

- [3] T.K. Chiang, Y.H. Wang, and M.P.Houng, "Modeling of threshold voltage and subthreshold swing of shortchannel SOI MESFET's," *Solid State Electron.*, vol.43, pp.123-129, 1999.

- [4] K.K. Young, "Short-channel effect in fully depleted SOI MOSFET's," *IEEE Trans. Electron. Devices*, vol.36, no.2, 1989

- [5] T.Toyabe and S. Asai, "Analytical models of threshold voltage and breakdown voltage of short-channel MOSFET's derived from two-dimensional analysis," *IEEE J. Solid-State Circuits*, vol. SC-14, pp.375-383, 1979.

- [6] J. D. Marshal, and J. D. Meindl, "An analytical twodimensional model for silicon MESFET's," *IEEE Trans. Electron Devices*, vol.35, no.3, pp.373-383, 1988.

S. Jit was born in the Midnapore district of West Bengal, India, on November 02, 1970. He received B.E. degree from the Department of Electronics and Telecommunication Engineering, Bengal Engineering College of the University of Calcutta, West Bengal, in 1993, M.Tech. degree from the Department of Electrical

Engineering, Indian Institute of Technology (I.I.T.), Kanpur, in 1995, and Ph. D. degree from the Department of Electronics Engineering, Institute of Technology, Banaras Hindu University (I.T.,B,H,U.), India, in 2002.

He is a Faculty Member in the department of Electronics Engineering, I.T.,B.H.U. He is a Life Member of The Institution of Electronics and Telecommunication Engineers (I.E.T.E.), India. His present research interests concern modeling and simulation of submicron devices, optically controlled microwave devices and circuits, and GaN MESFET's.

Prashant Pandey was born in the Mirzapur district of Uttar Pradesh (U.P.), India, on March 15, 1977. He received B.Sc.(Physics) degree from the Purvanchal University, U.P., India in 1996 and M.Sc. degree from the Department of Physics, Banaras Hindu University (B.H.U.), Varanasi, India, in

1998. He is currently pursuing the Ph.D. degree in the Department of Electronics Engineering, Institute of Technology, Banaras Hindu University (I.T.,B.H.U.), Varanasi, India.

He is a Senior Research Fellow in the Centre of Advanced Studies, Department of Electronics Engineering, I.T.,B.H.U., Varanasi, India. His present research interests concern 2-D modeling and simulation of submicron SOI-MESFET's and MOSFET's.

**B.B.Pal** is a Professor in the Department of Electronics Engineering, Institute of Technology, Banaras Hindu University, Varanasi, India. He has published more than 200

technical papers in journal and conference proceedings. His present areas of interests include VLSI design, high-speed and novel semiconductor devices, and optoelectronic devices.

Dr. Pal is a Life Member of Semiconductor of India (Founder), The Optical Society of India, and Nikhil Bharat Bengali Literature Society. His name has been included in several *Who's Who* publications. He is the recipient of the Outstanding Man of the Twentieth Century certificate and 2000 Millennium Medal of Honor. He is the Coordinator of the Special Manpower Development Project in VLSI design sponsored by the Ministry of Information Technology, Government of India. He is also the Coordinator of the Center of Research in Microelectronics and Center of Advanced Studies in Microelectronics and Microwave Engineering.