논문 2005-42TC-11-2

# 디지털 오디오/비디오, 통신용 전자기기를 위한 Reed Solomon 복부호기 설계에 대해

(Reed Solomon CODEC Design For Digital Audio/Video,Communication Electronic Devices)

안 형 근

(Hyeong-Keon An)

요 약

현대의 디지털통신기기나 ,오디오/비데오 전자기기엔 항상 비바이나리 에러정정복부호기가 사용되는데 그중 필수적으로 사용되는 Reed-Solomon 복부호화기기의 설계에 대해 기술했다. 2,3 symbol RS 복호기설계법을 설명 후, 새로운 RS 부호화기의 설계법을 제시한다. 각각의 복부호화기기의 동작여부를 예를들어 test해보고 잘 동작함을 확인했다.

#### **Abstract**

For Modern Consumer and Communication Electronic Devices, Always Error Protecting HW and SW is used. The Core is RS(Reed Solomon) Codec in Galois Field GF(2<sup>8</sup>). Here New 2 to 3 Symbol RS Decoder Design and Encoder design Method using Normalized error position Value is described. Examples are given to show the methods are working well.

**Keywords:** RS(Reed Solomon), Syndrome, Encoder, Decoder, Error Locator polynomial, Galois Field(GF)Digital Compact Cassette (DCC), Mini Disc(MD), Audio/Video(A/V)

# I. Introduction

Reed Solomon coding theory is very famous well known nonbinary error correction method for Digital Electronic Devices (Consumer and Communication products.)<sup>[3]</sup>

In this paper, new RS(Reed Solomon) Decoder, which is correcting 2 and 3 symbol errors, and encoder design method is proposed using Normalized error position stored ROM<sup>[7]</sup>. Here New encoder is designed using Erasure correcting decoding algorithm

so removing separate encoding hardware so saving total gate counts of the Codec. The New RS Codec is much simpler and faster than before, So More efficient RS CODEC SOC(System On Chip) design is Possible<sup>[1,2]</sup>.

In chapter II, we briefly described RS(Reed Solomon) ECC algorithm<sup>[9]</sup>. For example we describe how to calculate syndromes, solve Newtonian identitiy equations. In chapter III, we describe the New RS Decoder algorithm which is correcting 2 symbol error in the codeword RS(32,28) in GF(2<sup>8</sup>). This Decoder is used for CDP(Compact Disc Player). Example is showing the algorithm is working well. In MD(Mini Disc Player), DCC, HDTV, Main computer magnetic storage system, 3 symbol error correcting RS decoder is used. And 3 symbol Error

<sup>·</sup> 정회원, 동명정보대학교 정보통신과 (Dept. of Information and Telecommunication Engineering, Tong Myung University of Information Technology.)

접수일자: 2005년8월3일, 수정완료일: 2005년11월10일

Correcting New algorithm is described in Chapter IV. Here we also show the example to verify the algorithm.

In chapter V, the new RS encoder, in GF(2<sup>8</sup>), design method is described. Here as we already mentioned, 4 Erasure correcting RS decoding algorithm is used for RS(32,28) encoder. For more clarity, we show Encoding example to describe the step of the algorithm and finally we find the syndromes of the output of Designed encoder is Zero so acknowledges that the New RS encoding process is working correctly<sup>[3]</sup>.

In chapter VI conclusions are made. Future works on 4 symbol error correcting RS decoder is briefly mentioned. Also Divider in GF(2<sup>8</sup>) design method is also discussed.

# II. Syndromes and Error Locator polynomial

An RS(Reed Solomon) codes are based on finite fields, often called Galois fields.

In CDP, RSC(32,28), on GF(2<sup>8</sup>) field, codes is used and up to 2 symbol errors can be corrected<sup>[2]</sup>.

An RS code with 8bit symbols will use a Galois field  $GF(2^8)$ , consisting of 256 symbols. In decoding Reed-Solomon code, we should calculate the Syndromes as in equation 1.

Let

$$C(X) = \sum_{j=0}^{n-1} C_j X^j$$

Be the Transmitted polynomial, and let

$$r(X) = \sum_{j=0}^{n-1} r_j X^j$$

Be the received polynomial. Then error pattern of the channel is

$$E(X) = \sum_{j=0}^{n-1} E_j X^j$$

Where  $E_{i}(j=0 \text{ to } n-1)$  are error values. Here Syndrómes are defined as

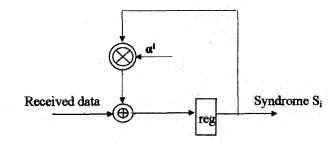

그림 1. RS 복부호기의 신드롬 계산기 Fig. 1. Syndrome calculator of RS codec.

$$S_i = E(\alpha^i)(i = 0, 1, \dots, 2t - 1)$$

(1)

For t error correction coding.

In this paper, for finding Error values and positions, syndrome calculator shown in Fig.1 is used<sup>[5,6,8]</sup>.

Now if there are t errors, error values are  $E_n \, (n=0,2\cdots,t-1)$  and their positions are  $\alpha^{jn} \, (n=0,1\cdots,t-1)$ .

Then Let

$$\beta_{\mathbf{j}}\left(\mathbf{j}=0,1,\cdots,\mathbf{t}-1\right)=\alpha^{\mathbf{j}\mathbf{n}}\left(\mathbf{n}=0,1,\cdots,\mathbf{t}-1\right)$$

and Error Locator polynomial is defined as

$$\delta(\mathbf{X}) = (\mathbf{X} - \beta_0)(\mathbf{X} - \beta_1) \cdots (\mathbf{X} - \beta_{t-1})$$

$$= \sum_{k=0}^{t} \mathbf{X}^k \delta_{t-k}$$

(2)

Now Newton's identities are following set of equations.

$$\sum_{j=1}^{t} S_{t-j+v} \delta_{j} = S_{v+t} (v = 0, 1, 2 \cdots, t-1)$$

(3)

These equations are for t error correcting Reed-Solomon codec<sup>[4]</sup>. If we apply these equations to 3 symbol error correction case (t=3), all the  $\delta_i$  (i=1,2,3) are got as described in the next section<sup>[8]</sup>.

# III. Two Symbol Error Correcting Reed Solomon Decoder Design for CDP

This algorithm can be used for RS decoder of CDP. Now we describe the way briefly as follows.

Normalize first to derive the new method, the error

location polynomial for 2 errors<sup>[2,9]</sup>.

$$\delta(\mathbf{x}) = \mathbf{X}^2 + \delta_1 \mathbf{X} + \delta_2$$

by  $\mathbf{X} = \delta_1 \mathbf{x}$

we get

$$\delta(x) = X^2 + x + K$$

, where  $K = \delta_2/\delta_1^2$  (4)

$$T_2(K) = \sum_{i=0}^{m-1} K^{2^i} \text{ and } m = 8$$

(5)

Hence

$$T_2(K) = \sum_{i=0}^{m-1} K^2 = K + K^2 + K^4 + K^8 + K^{16} + K^{32} + K^{64} + K^{128}$$

(6)

(Theorem) If  $\theta = \lambda - \lambda^2$ ,  $\lambda \in \mathrm{GF}\,(2^{\,\mathrm{m}})$ , then  $\mathrm{Tr}\,(\theta) = \mathrm{T}_2(\theta) = 0$ .

Here

$$Tr(K) = T_2(K) = \sum_{i=0}^{m-1} K^{2^i}$$

From the thorem, equation (4) has a solution when equation (5)  $Tr(K) = T_2(K) = 0[3]$ .

In this case, if  $K=(k_0,k_1,k_2,k_3,k_4,k_5,k_6,k_7)$ ,  $k_i\in G^F(2)$ , then  $k_5=0$ . And 2 solutions  $x_1,x_2$  of equation (4) can be got as in equation (7).

$$x_2 = 1 + x_1 (7.b)$$

Now real solutions  $X_1, X_2$  are

$$X_1 = \delta_1 x_1, X_2 = \delta_1 x_2$$

(8)

Also two errors values are calculated as follows.

$$S_2 = e_1 X_1^2 + e_2 X_2^2$$

$S_1 = e_1 X_1^2 + e_2 X_2^2$  (9)

Hence

$$X_2$$

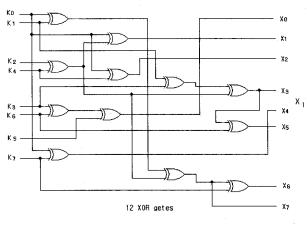

그림 2. K vector를 2개의 정규오류위치로 변환하는 논 리회로

Fig. 2. Logic circuit which converts k to 2 normalized error locations.

$$E_{1} = \frac{S_{1}X_{2} + S_{2}}{X_{1}X_{2} + X_{1}^{2}}$$

$$E_{2} = \frac{S_{1}X_{1} + S_{2}}{X_{1}X_{2} + X_{2}^{2}}$$

(10)

In this way, 2 error locations and error values are all found. Equation (7) can be drawn as in Fig.2. Circuit. From K to 2 error locations, we use Fig.2 circuit.

(EXAMPLE) In  $GF(2^8)$ , when code polynomial  $C(\mathbf{x}) = 0$  is transmitted to the receiver, the received polynomial.

$$r(x) = \alpha^2 x + \alpha^3 x^4.$$

So two error values and locations are  $\alpha^2$  at and  $\alpha^3$  at  $\alpha^4$ . Verify these values using the new method.

$$S_1 = \alpha^3 + \alpha^7 = \alpha^{103}$$

$S_2 = \alpha^4 + \alpha^{11} = \alpha^{116}$

$S_3 = \alpha^5 + \alpha^{15} = \alpha^{26}$

$S_4 = \alpha^6 + \alpha^{19} = \alpha^{105}$

The error locator polynomial is  $\delta\left(\mathbf{X}\right)=\mathbf{X}^{2}+\delta_{1}\mathbf{X}+\delta_{2},$  where

$$\begin{pmatrix} \delta_2 \\ \delta_1 \end{pmatrix} = \begin{pmatrix} \mathbf{S}_1 \mathbf{S}_2 \\ \mathbf{S}_2 \mathbf{S}_3 \end{pmatrix}^{-1} \begin{pmatrix} \mathbf{S}_3 \\ \mathbf{S}_4 \end{pmatrix} = \begin{pmatrix} \alpha^5 \\ \alpha^{224} \end{pmatrix}$$

hence

$$K = \delta_2/\delta_1^2 = \alpha^{67} = (01000011)$$

So from equation (7).

We get 2 normalized error locations as follows.

$$=\alpha^{32}$$

These are correct 2 error locations.

Two error values are from equation (10),

$$\begin{aligned} \mathbf{Y}_1 &= \frac{\mathbf{S}_1 \mathbf{X}_2 + \mathbf{S}_2}{\mathbf{X}_1 \mathbf{X}_2 + \mathbf{X}_1^2} = \frac{\alpha^{107} + \alpha^{116}}{\alpha^5 + \alpha^2} = \frac{\alpha^{227}}{\alpha^{225}} = \alpha^2 \\ \mathbf{Y}_2 &= \frac{\mathbf{S}_1 \mathbf{X}_1 + \mathbf{S}_2}{\mathbf{X}_1 \mathbf{X}_2 + \mathbf{X}_2^2} = \frac{\alpha^{104} + \alpha^{116}}{\alpha^5 + \alpha^8} = \frac{\alpha^{231}}{\alpha^{228}} = \alpha^3 \end{aligned}$$

These are correct 2 error values.

# IV. Triple Symbol Error Correcting Reed Solomon Decoder Design for DCC,MD(Digital Compact Cassette, Mini Disc Player)

This 3 Symbol Error Correcting RS decoder can also be used for Digital Communicating Modem LSI. In  $GF(2^8)$ , If there are 3 symbol errors in the received codeword, we can find 3 error positions and Error values as follows<sup>[4,7]</sup>.

Here we use ROM tables as in 2 symbol error case <sup>[2]</sup>. In this case, Error Locator polynomial is

$$X^{3} + \delta_{1}X^{2} + \delta_{2}X + \delta_{3} = 0$$

(11)

Here

< Zi ROM table >

| Address(δ/Œ <sup>3/2</sup> ) | data (Zi, i=1,2,3)                                     |

|------------------------------|--------------------------------------------------------|

| 0                            | 0,1,1                                                  |

| 1                            | *                                                      |

| Œ.                           |                                                        |

| α2                           |                                                        |

| •                            |                                                        |

|                              | *                                                      |

| •                            | 10                                                     |

|                              | ·                                                      |

| α <sup>239</sup>             | α <sup>157</sup> , α <sup>181</sup> , α <sup>156</sup> |

| •.                           |                                                        |

| α <sup>254</sup>             |                                                        |

그림 3. 방정식 15에대한 ROM 테이블

Fig. 3. ROM table corresponding to equation 15. When Address = 0, Only 2 roots exist.

$$\begin{split} \delta_1 &= \left( S_1 S_3^2 + S_1^2 S_5 + S_2^2 S_3 + S_0 S_2 S_5 + S_0 S_3 S_4 + S_1 S_2 S_4 \right) / \chi, \\ \delta_2 &= \left( S_0 S_4^2 + S_2 S_3^2 + S_2^2 S_4 + S_0 S_3 S_5 + S_1 S_2 S_5 + S_1 S_3 S_4 \right) / \chi, \\ \delta_3 &= \left( S_3^3 + S_1 S_4^2 + S_2^2 S_5 + S_1 S_3 S_4 \right) / \chi \end{split}$$

(11-1)

where  $\chi = S_2^3 + S_0S_3^2 + S_1^2S_4 + S_0S_2S_4$  From equation

13, if

$$X = \delta_1 + y$$

, also if

$$E = \delta_1^2 + \delta_2, \delta = \delta_1 \delta_2 + \delta_3$$

then

We get

$$Y^3 + EY + \delta = 0 \tag{12}$$

If

$$E = 0$$

,  $Y = (\delta)^{1/3}$ , otherwise

Let's define

$$Z_i = E^{-1/2}Y_i$$

(i = 1,2,3)

$$Z^{3} + Z + \delta/E^{3/2} = 0 \tag{13}$$

From Equation 6, corresponding to Add=  $\delta/(E^{3/2})$  we can construct ROM table of root of equation (13) as in Fig.3.

Once we find  $Z_i\,(i=1,2,3),\,Y_i\,(i=1,2,3)=(E^{\,1/2}Z_i\,)\,So$  exact Error positions are

$$X_i = Y_i + \delta_1 (i = 1, 2, 3)$$

(14)

Also Error values are

$$E_{i} = (S_{0}\delta_{3}/X_{i} + S_{1}(\delta_{1} + X_{i}) + S_{2})/(X_{i}^{2} + \delta_{2})$$

$$(i = 1, 2, 3)$$

(15)

| 40                                                      | D016 |        |

|---------------------------------------------------------|------|--------|

| <square< td=""><td>ROM</td><td>table&gt;</td></square<> | ROM  | table> |

| Address ai       | Data α <sup>2i</sup> |

|------------------|----------------------|

| 0                | 0                    |

| 1                | 1.                   |

| α                | $\alpha^2$           |

| α²               | or <sup>4</sup>      |

| α3               | $\alpha^6$           |

|                  | •                    |

|                  | •                    |

| a <sup>254</sup> | $lpha^{253}$         |

- 1) 자승을 계산하는 ROM표

- 1) Square calculation using ROM

$\alpha^{i}$

- 2) 곱셈기를 이용한 자승계산기

- 2) Square calculation with Multiplier

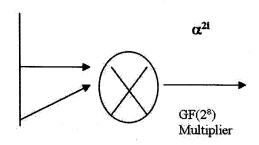

그림 4. ROM을 사용 않는 자승계산기

Fig. 4. Square calculator with and without ROM.

As we see, there are many  $\mathrm{GF}(2^8)$  Arithmatic operations to compute the Error values and positions. In Fig.4. we show how to compute square values. Other operations needed are  $\alpha^{1/2}, \alpha^{\mathrm{j}}/\alpha^{\mathrm{j}}$ . Allthese operations can be done using only Inverse calculator and Multiplier.

Next section, we show how to design Reed-Solomon Encoder using RS Erasure Decoder<sup>[4]</sup>.

# <Example> Triple Error correcting Reed Solomon Decoder example :

From the Transmitter, we send all 0 data so

Code polynomial C(x) = 0. In Receiver, Received polynomial  $R(x) = \alpha + \alpha x + \alpha^2 x^2$ .

In this case, find 3 error values and positions. All code symbols are 8 bits wise so  $GF(2^8)$  field elements are used.

## <Solution>

We first find Syndromes:

$$\begin{split} &S_0 = \alpha^2, S_1 = \alpha + \alpha^2 + \alpha^4 = \alpha^{239} \, S_2 = \alpha^{37}, \, S_3 = \alpha^{75}, \\ &S_4 = \alpha^{219}, \, S_5 = \alpha^{24}. \, \text{From Equations (11-1 ), we find} \\ &\text{out} \quad \delta_1 = \alpha^{198}, \, \delta_2 = \alpha^{199}, \, \delta_3 = \alpha^3 \, . \quad \text{So} \quad \text{from} \\ &\text{equations} \quad \text{(12),} \quad E = \alpha^{248}, \, \delta_2 = \alpha^{101}. \quad \text{Hence} \\ &\delta /\!E^{3/2} = \alpha^{239}. \end{split}$$

So from following equation,

$$Z^3 + Z + \alpha^{239} = 0$$

So Using ROM table in fig.3, we find that

$$Z_i = \alpha^{157}, \alpha^{181}, \alpha^{156}$$

Therefore

$$Y_{i} = E^{1/2} Z_{i} = \alpha^{26}, \alpha^{50}, \alpha^{25} (i = 1, 2, 3)$$

So from equation(14),

$$X_i = Y_i + \delta_1(i = 1, 2, 3) = \alpha^0, \alpha^1, \alpha^2$$

These are 3 correct Error ositions and 3 error values are calculated from equation (15), as  $\alpha$ ,  $\alpha$ ,  $\alpha^2$ . These are also correct 3 error values as we see from received polynomial r(x).

# V. New Reed Solomon Encoder Design For Digital A/V Devices

When we design a Reed Solomon Encoder, normally we use separate Encoderfor RS Codec. But VLSI H/W of this method becomes very complex, because there is separate RS Encoder and Decoder and Encoder itself is not so simple in HW wise also.

Here to save the Encoding HW(Hardware) we briefly describe the encoding hardware ,which is the Erasure corrector of the RS Decoder. So Encoder is part of the RS decoder and we neednot design the separate Encoder saving the Encoder HW<sup>[4,5]</sup>.

# <Encoding Steps>

- 1. Assume arbitrary parity values ( Normally assume 0 ) :  $P'_0, P'_1, P'_2, \dots, P'_{k-1}$

- Using K syndromes calculated by the cct in Fig. 3, Erasure Decoder get the K Erasure Values.

- K Erasure values are added to the assumed Parities and the result values Are True Parities.

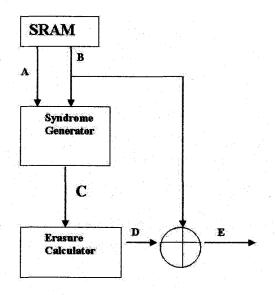

The New Encoder Block Diagram is shown in Fig. 5.

# <Example>

In RS(32,28) code system of GF(2<sup>8</sup>), let's assume all '0' parities. The \ codeword polynomial  $C\left(x\right) = P_0 + P_1x + P_2x^2 + P_3x^3 + D_4x^4 + \cdots + D_{31}x^{31}$ , where  $P_i\left(i=0,1,2,3\right)$  are parities and  $D_j\left(j=4,5,\cdots,31\right)$  are data bytes. If  $D_j\left(j=3,4,\cdots,30\right)$ ,

$A: D_0, D_1, ..., D_M$  (Data)

B: P'0,P'1, ..., P'k-1 (Error Parities)

$C : S_0, S_1, ..., S_{k-1}$

D: E<sub>0</sub>, E<sub>1</sub>, ..., Ek-1 (Erasure Values)

E: Po, P1, ..., Pk-1 (Correct Parities)

그림 5. 새로운 RS 부호화기의 블록그림

Fig. 5. Block Diagram of New RS Encoder.

$D_{31} = \alpha^0 = 1$ , Find the Correct Parities  $P_i$  (i = 0 to 3)

### <Sol>

Parity positions are known so this is the Erasure Correction case. Because all assumed Parities are 0 and using given data bytes, we calculate syndromes.

$$S_0 = C(\alpha^0) = 1$$

$$S_1 = C(\alpha^1) = \alpha^{31}$$

$$S_2 = C(\alpha^2) = \alpha^{62}$$

$$S_3 = C(\alpha^3) = \alpha^{93}$$

(16)

Now we setup following equations to find 4 erasure values  $E_0$ ,  $E_1$ ,  $E_2$ ,  $E_3$ .

$$E_{0} + E_{1} + E_{2} + E_{3} = S_{0}$$

$$E_{0} + E_{1}\alpha + E_{2}\alpha^{2}, E_{3}\alpha^{3} = S_{1}$$

$$E_{0} + E_{1}\alpha^{2} + E_{2}\alpha^{4}, E_{3}\alpha^{6} = S_{2}$$

$$E_{0} + E_{1}\alpha^{3} + E_{2}\alpha^{6}, E_{3}\alpha^{9} = S_{3}$$

(17)

From equations (1) and (2),

$$\begin{pmatrix}

E_{0} \\

E_{1} \\

E_{2} \\

E_{3}

\end{pmatrix} = \begin{pmatrix}

1 & 1 & 1 & 1 \\

1 & \alpha & \alpha^{2} & \alpha^{3} \\

1 & \alpha^{2} & \alpha^{4} & \alpha^{6} \\

1 & \alpha^{3} & \alpha^{6} & \alpha^{9}

\end{pmatrix}^{-1} \begin{pmatrix}

S_{0} \\

S_{1} \\

S_{2} \\

S_{3}

\end{pmatrix} =$$

$$\alpha^{108} \begin{pmatrix}

\alpha^{110} & \alpha^{50} & \alpha^{48} & \alpha^{104} \\

\alpha^{50} & \alpha^{30} & \alpha^{149} & \alpha^{45} \\

\alpha^{48} & \alpha^{149} & \alpha^{27} & \alpha^{44} \\

\alpha^{104} & \alpha^{45} & \alpha^{44} & \alpha^{101}

\end{pmatrix} \begin{pmatrix}

\alpha^{0} \\

\alpha^{31} \\

\alpha^{62} \\

\alpha^{93}

\end{pmatrix} = \begin{pmatrix}

\alpha^{148} \\

\alpha^{67} \\

\alpha^{205} \\

\alpha^{249}

\end{pmatrix}$$

(18)

So From Fig.5 and Equation (18), we find correct Pasrities as follows.

$$P_{1}, = 0 \text{ to } 3] = [E_{1} + \text{Initial } P_{1}] = \begin{cases} \alpha^{148} & T \\ i = 0 \text{ to } 3 \end{cases}$$

$$= [\alpha^{148}, \alpha^{67}, \alpha^{205}, \alpha^{249}]$$

$$\alpha^{249}$$

$$\alpha^{249}$$

$$\alpha^{249}$$

Using this Correct Parities, we find all syndromes  $S_j$ , j=0 to 3 are zeros and this is correct.

# VI. Conclusions

In this Paper, we described how to implement 2 to 3 symbol error correcting RS ECC decoder. Here Tracing K vector and Normalized error position stored ROM is used. We also study how to implement RS ECC encoder using Erasure correcting RS decoder. For DAT(Digital Audio Tape Recorder) case, 6 parities are used for the Encoder, and we use 6 Erasure correcting RS Decoder for the Encoder.

Later We will study how to implement 4 symbol error correcting RS decoder using GF(2<sup>4</sup>) sub field, resulting in even further greately reducing RS codec HW circuitry

This Kind of RS Codec is used for most of the Current Digital Audio/Video and Communication devices, for example CDP, MP3, MD, HDTV, DMB, Digital Cellular phone, etc.

In Our future we will study how to implement Galois Field Arithmatic Operator in  $GF(2^8)$  field using Subfield  $GF(2^4)$  arithmetic operation, for example Divider. Here both direct divider and indirect divider can be used using Inverse calculator and Multiplier in  $GF(2^4)$  field [1].

# References

- [1] US patent number 5227992, "Operational Method and Apparatus over GF(2<sup>m</sup>) using a Subfield GF(2<sup>m/2</sup>)", Man-young Lee, Hyeong-Keon An et al., 1993 Jul. 13

- [2] Hyeong-Keon An, "2 Error Correcting RS Decoder design", IDEC Conference Paper, 2004.

- [3] Hyeong-Keon An, TS Joo et al, "The New RS Ecc Codec For Digital Audio and Video", IEEE CES Conference paper, PP112-115, 1992.

- [4] Lee Man Young, "BCH coding and Reed-Solomon Coding theory", 1990, Minumsa(Daewoo Academic Press).

- [5] Sunghoon Kwon and Hyunchul Shin, "Anarea-efficient VLSI architecture of Reed-Solomon decoder/encoder for digital VCRs", IEEE Transactions on Consumer Electronics, Vol. 43, No.4, Nov. 1997.

- [6] Kwang Y.Liu, "Architecture for VLSI design of Reed-Solomon Decoders", IEEE Transactions on Computers. Vol.33, No.2, Feb. 1984.

- [7] 岡野博: "ROM used 2 to 3 error correcting BCH Decoder Improvement", 信學技報 ,AL 82-56 (1982).

- [8] Hsu, I.K., I.S.Reed, "The VLSI Implementation of

- a Reed-Solomon Encoder Using Berlekamp's Bit-Serial Multiplier Algorithm", IEEE Trans. On Computer, Vol.C-33, No.10, pp.906-911(1984).

- [9] Shu Lin, Daniel J. Costello, Jr., "Error Control Coding", Prentice-Hall, pp.240 -261(20044).

# - 저 자 소 개 -

### 안 형 근(정회원)

- He received B. Engineering Degree in electrical engineering from Seoul National University, Seoul, KOREA, in 1979 and M.S degree in electrical science from Korea Advanced Institute of Science and Technology, Seoul, Korea in 1981, and the Ph.D. degree in electrical engineering from State University of New York at Stony Brook, NY, USA., in 1988.

- In 1988, he joined Samsung Electronics Co.Ltd as a Senior Researcher working for design ing System LSI for 10 years.

- From 1998 to 1999, He worked for Telson Electronics Corp. working for CDMA handphone design.

- In 2000, he joined Tong Myoung University in Busan as a Professor in Dept. Of Information and Telecommunication engineering.

- He has interests in designing CDMA and GSM hand phone and also in System LSI (Non Memory ) design.

- He also operates Venture Comapany for Producing various Mobile phones and GPS/MP3Engines.