# Device Characteristics of AlGaN/GaN MIS-HFET using Al<sub>2</sub>O<sub>3</sub> Based High-k Dielectric

Ki-Yeol Park, Hyun-Ick Cho, Eun-Jin Lee, Sung-Ho Hahm and Jung-Hee Lee

Abstract—We present an AlGaN/GaN metal-insulator-semiconductor-heterostructure field effect transistor (MIS-HFET) with an Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated high-k dielectric, deposited by plasma enhanced atomic layer deposition (PEALD). Based on capacitance-voltage measurements, the dielectric constant of the deposited Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated layer was estimated to be as high as 15. The fabricated MIS-HFET with a gate length of 1.2 μm exhibited a maximum drain current of 500 mA/mm and maximum transconductance of 125 mS/mm. The gate leakage current was at least 4 orders of magnitude lower than that of the reference HFET. The pulsed current-voltage curve revealed that the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated dielectric effectively passivated the surface of the device.

Index Terms— Insulator, high-k dielectric, AlGaN/GaN HFET, MIS, Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated dielectric

## I. Introduction

AlGaN/GaN heterostructure field effect transistor (HFET) have great potential for use in high voltage, high current, and high power device applications due to their excellent material characteristics[1]. It has been observed that the characteristics of HFETs with a conventional Schottky gate tend to degrade with a large gate leakage current and occasionally a current collapse phenomenon occurs when the HFETs are operating under high power

and high frequency conditions[2]. As such, to solve the serious gate leakage problem by passivating the surface and effectively reducing the gate leakage current, various gate insulation layers, such as SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Ga<sub>2</sub>O<sub>3</sub>, and Al<sub>2</sub>O<sub>3</sub> have been additionally deposited on the surface of the AlGaN/GaN heterostructure, although the transconductance of the device decreases due to the increase in the effective barrier thickness[3-5]. Another advantage of using an insulating layer is that it increases the gate breakdown voltage, thereby positive gate biasing is possible[4].

Al<sub>2</sub>O<sub>3</sub> has excellent dielectric properties, good adhesion to various surfaces, and thermal and chemical stability, yet it has a relatively small dielectric constant (ε<sub>τ</sub>-9) to fully replace SiO<sub>2</sub>(ε<sub>τ</sub>-3.9). Conversely, HfO<sub>2</sub>(ε<sub>τ</sub>-30) has excellent characteristics as a high-k dielectric, except it has relatively small bandgap[6]. Therefore, to utilize the combined advantages of both materials, the current study proposes the use of an Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated layer as the gate insulator for an AlGaN/GaN metal-insulator-semiconductor (MIS)-HFET and investigates the electrical properties of the fabricated device.

## II. EXPERIMENTAL DETAILS

Both AlGaN/GaN HFET(reference device) and MIS-HFET used in the current study were first grown by metal organic chemical vapor deposition (MOCVD) on a sapphire substrate. The thickness of the undoped AlGaN and GaN was 250 Å and 2.5  $\mu$ m, respectively, and the Al composition of the AlGaN layer was 30 %. For the device isolation, mesa etching (1500 Å deep) was performed on

the AlGaN surface using transfomer-coupled-plasma (TCP) reactive ion etching (RIE) with a Cl<sub>2</sub> and BCl<sub>3</sub> gas mixture. For the MIS structure, an additional Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated layer was then sequentially deposited by plasma-enhanced atomic layer deposition(PEALD) on the surface of the AlGaN/GaN heterostructure, as shown in Figure 1[7] Thermal annealing in N<sub>2</sub> ambient at 800 °C was then performed to stabilize the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated layer / AlGaN interface characteristics.

A contact-hole opening for source and drain was made by TCP-RIE using a CF4 and Cl2 gas mixture. The Ti/Al/Ni/Au layer was deposited using an electron beam evaporator with respective thicknesses of 300, 800, 200, and 500 Å, which was followed by rapid thermal annealing at 900 °C for 10 sec to form ohmic contacts. The contact resistivity was  $10^{-5} \sim 10^{-6} \ \Omega \cdot \text{cm}^2$ , which was measured using the transfer length method. The gate metal was finally deposited by evaporating Ni/Au. The source to drain spacing was 5 µm, and the gate length was 1.2 µm.

# III. RESULTS AND DISCUSSIONS

Before and after the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> dielectric deposition, the 2-dimensional electron gas(DEG) mobilities and sheet carrier densities were measured by Hall measurements. The sheet carrier concentration increased to  $2.6 \times 10^{13}$  /cm<sup>2</sup> after the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> deposition, which was almost two times larger than the  $1.2 \times 10^{13}$  /cm<sup>2</sup> value before the Al2O3-HfO2 deposition. Although the reason for the significant increase in the sheet carrier concentration was not apparent, it is believed that it was strongly related to a reduction in the surface states of the passivated AlGaN surface with the deposition of Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub>[8] Meanwhile, the carrier mobility decreased from 1200 to 800 cm<sup>2</sup>/V·s, possibly due to increased electron-electron scattering and/or interface roughness scattering with such a high carrier concentration in 2-DEG channel[9]. From the ns· µ value, the current handling capability of the MIS-HFET is expected to be increased to 1.5 times larger than that of the conventional HFET.

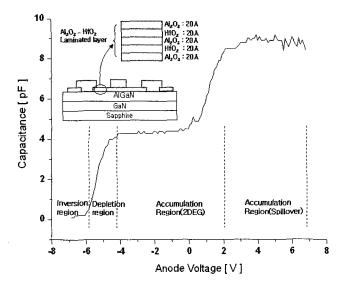

Figure 1 shows the capacitance-voltage characteristics of the MIS ring diode with 50 μm diameter, measured using an HP4280 at 1 MHz. The total capacitance(C<sub>tot</sub>) of

the MIS structure can be modeled by four parallel plate capacitances in series, the gate dielectric capacitance (C<sub>dielectric</sub>), the AlGaN barrier capacitance (C<sub>barrier</sub>), the 2DEG Capacitance (C<sub>2DEG</sub>), and the depletion capacitance of GaN (C<sub>dep</sub>), neglecting C<sub>inv</sub> possibly formed at high negative gate bias (at -6 v in Fig.1) [10].

Fig. 1. Capacitance voltage curve of a ring diode and transconductance curve for fabricated MIS-HFET

$$\frac{1}{C_{tot}} = \frac{1}{C_{dielectric}} + \frac{1}{C_{barrier}} + \frac{1}{C_{DEG}} + C_{dep}$$

(1)

Each capacitance can be expressed as

$$C = \frac{A\varepsilon_0 \varepsilon_i}{d}$$

(2)

, where  $\epsilon_0$  is the permittivity of air,  $\epsilon_i$  is the relative dielectric constant of each layer, A is the area of capacitor, and d is the thickness of each layer.

At accumulation bias(above -5 V) C<sub>dep</sub> can be neglected. From the measured value of C<sub>tot</sub> of 4.4 pF, the calculated value of C<sub>barrier</sub> of 6.26 pF, and C<sub>2DEG</sub> of 33 pF, assuming the 2DEG thickness of approximately 50 Å. The capacitance(Cdielectric) of the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated layer was then calculated as 26.8 pF and the corresponding effective dielectric constant of the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated layer was estimated to be as high as approximately 15. This value is well agree to the value of 15.4 calculated from simple linear approximation of dielectric constant for the laminated layer (60% of Al<sub>2</sub>O<sub>3</sub> and 40 % of HfO<sub>2</sub>),

assuming respective dielectric constants of 9 and 25 for both materials. The increase in C<sub>tot</sub> to ~ 8 pF observed at biases larger than 2 V, was seemingly due to a charge spillover from the 2DEG to the AlGaN barrier, which decreases the effective thickness of AlGaN barrier and thus increases the C<sub>barrier</sub> and the C<sub>tot</sub>. The charge spillover cause parallel conduction in AlGaN layer leading to rapid transconduction decrease which is evident in Figure. 2[11].

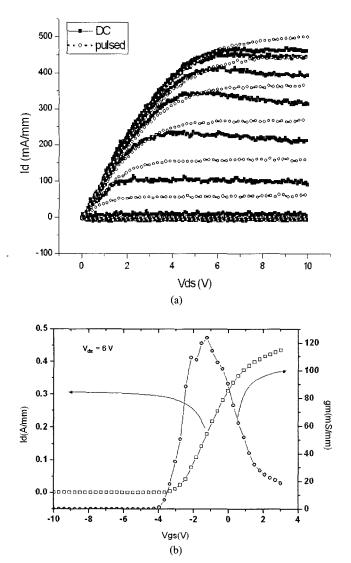

Fig. 2. DC and Pulsed I-V cruve(a) and transconductance characteristics(b) of the AlGaN/GaN MIS-HFET

The gate insulator must have a high dielectric constant to have a high device transconductance. Yet, the insertion of an insulator between the gate metal and the channel region can decrease the transconductance due to an increased effective barrier thickness, and thus, decreased gate capacitance. Therefore, the use of a high-k dielectric material as the gate insulator can compensate for the reduction in transconductance.

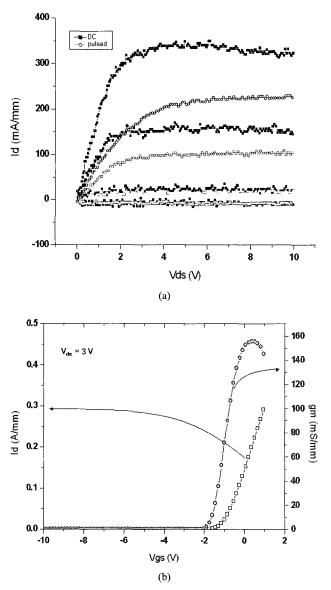

The DC characteristics of the fabricated MIS-HFET were measured using an HP4155B while the pulsed I-V characteristics were measured using a DiVA<sup>TM</sup>. Figure 3 shows both DC and pulsed I<sub>d</sub>-V<sub>d</sub> curves, and transconductance characteristics of the fabricated HFET. The gate bias was from V<sub>g</sub>= 1 to -4V with -1V step and the pulse width was 500 ns with the pulse duration of 0.5 ms. The drain current was 330 mA/mm at V<sub>gs</sub>= 1 V and the maximum transconductance of the device was 160 mS/mm at V<sub>gs</sub>= 0 V, exhibiting severe current collapse during the pulse measurement.

Fig. 3. DC and Pulsed I-V curve(a), transconductance characteristics (b) of the AlGaN/GaN HFET

Measurements were also performed for the MIS-HFET at same conditions except driving the gate bias up to +3 V. The drain current increased to 420 mA/mm at  $V_{gs}$ = 1 V (500 mA/mm at V<sub>gs</sub>= 3 V) with a slight current collapse, about 30 % larger than that of the reference HFET, and the maximum transconductance of the device was decreased to 125 mS/mm at  $V_{gs}$ = -2 V. However, this value is still high compared to other MIS-HFETs with similar device dimensions and cut off voltage was about -3.5 V which was lower than low-k MIS-HFETs[7]. Also, the DC characteristics, such as transconductance, maximum drain current, and gate leakage current, of the fabricated device are superior to Al<sub>2</sub>O<sub>3</sub> MIS-HFET, which was fabricated by other group[8]. As a results, the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated dielectric layer effectively passivated the AlGaN surface, although a slight current collapse was observed in the saturation region. The breakdown voltage of fabricated MIS-HFET was measured to be about 100 V at  $V_{gs}$ = -3 V.

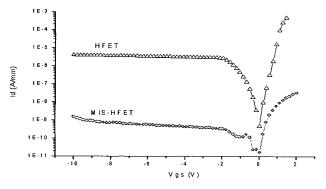

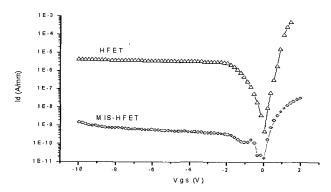

Figure 4 shows the gate leakage currents of both HFET and MIS-HFET in the negative drain bias region, showing that the leakage current of the MIS-HFET is at least 4 orders of magnitude lower than that of the reference AlGaN/GaN HFET. This value is also comparable to other MIS-HFETs using low-k dielectrics, such as SiO<sub>2</sub> or Si<sup>3</sup>N<sub>4</sub>[4]. As such, this result shows that the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated layer played an excellent role as a gate insulator and surface passivation material, while also minimizing the reduction in the transconductance of the device.

Figure 5 shows the small signal s-parameter measurement using Agilent N-5250 PNA system for a 0.3  $\mu$ m gate device at  $V_{ds} = 6V$  and  $V_{gs} = -6V$ . The cut-off frequency( $f_T$ ) is about 45GHz.

Fig. 4. Gate leakage current for the fabricated AlGaN/GaN HFET and MIS-HFET

Fig. 5. RF performance for 0.3 µm gate MIS-HFET

### IV. Conclusions

The AlGaN/GaN HFET and MIS-HFET using PEALD deposited Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated dielectric which was used both as reliable gate dielectrics for an AlGaN/GaN MIS-HFET and as a surface passivation layer were fabricated. The dielectric constant of the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated layer was as high as 15. The current density was almost two times larger than that of HFET at same gate bias, and tranconductance was slightly lower than that of HFET. These results mainly attributed to the increased n<sub>5</sub>·µ value due to the surface passivation and high value of the dielectric constant of the Al<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> laminated layer. The gate leakage current was measured to be at least 4 orders magnitude lower than that of HFET.

# ACKNOWLEDGMENTS

This work partially supported by grant R01-2003-000-10769-0 from the Basic Research Program of the Korea Science & Engineering Foundation, the Brain Korea 21 (BK21).

# REFERENCES

[1] S.J. Pearton, F. Ren, A.P. Zhang, and K.P. Lee, "Fabrication and performance of GaN electronic devices," *Materials Science and Engineering*, R30, pp.

55-212, 2000.

- [2] M. A. Khan, M. S. Shur, Q. C. Chen, and J. N. Kuznia, "Current/voltage characteristic collapse in AlGaN/GaN heterostructure insulated gate field effect transistors at high drain bias," *Electron. Lett.*, vol. 30, p.2175-2176, Dec. 8, 1994.

- [3] M. Asif Khan, X. Hu, A. Tarakji, G. Sumin, J. Yang, R. Gaska, M. S. Shur, , "AlGaN/GaN Metal Oxide Semiconductor Heterostructure Field Effect Transistors on SiC substrates," *Applied Physics Lett.* vol. 77 No. 9, pp.1339-1341, 2000.

- [4] M. Asif Khan, X. Hu, G. Sumin, A. Lunev, J.Yang, M. S. Shur, "AlGaN/GaN Metal Oxide Semiconductor Heterostructure Field Effect Transistor," *IEEE Electron Device Lett.* vol. 21 No. 2, pp.63-65, 2000.

- [5] S. Ootomo, T. Hashizume, H. Hasegawa, "A Novel Thin Al2O3 Gate Dielectric by ECR-Plasma Oxidation of Al for AlGaN/GaN Insulated Gate Heterostructure Field-Effect Transistors," *Phys. stat. Sol. (c)*, 0, 90, 2002.

- [6] J. Y. Lee, B. C. Lai, "The electrical properties of high dielectric constant and ferroelectric thin films for very large scale integration circuits," *Handbook of Thin Films Materials: Ferroelectric and dielectric thin films*, Academic press, pp. 1-98, 2002.

- [7] S. W. Choi, C. M. Jang, D. Y. Kim, J. S. Ha, H. S. Park, W. K. Y. Koh, C. S. Lee, *Journal of the Korean Physical Society*, Vol. 42, pp. S975-S979, February 2003.

- [8] D.H. Yoon, V. Kumar, J. H. Lee, R. Schwindt, W. J. Chang, J. Y. Hong, C. M. Jeon, S. B. Bae, M. R. Park, K. S. Lee, J. L Lee, I. Adesida, *IEE Electronics Lett.*, vol. 39, pp. 566, 2003.

- [9] O. Katz, A. Horn, G. Bahir, J. Salzman, *IEEE Trans*. *Electron Devices*. vol. 50, No. 10, pp.2002, 2003.

- [10] W. Liu: Fundamentals of III-V devices-HBTs, MESFETs, and HFETs/HEMTs (A Wiley-Interscience publication) Chap. 5, pp.337, 1999.

- [11] P. A. Ivanov, M. E. Levinshtein, G. Simin, X. Hu, J. Yang, M. A. Khan, S. L. Rumyantsev, M. S. Shur, R. Gaska, vol. 37, No. 24, pp.1479, 2001.

**Ki-Yual Park** He was born in Seoul, Korea, in 1970, He received the B.S degree in electronic engineering from Kyungpook National University, Taegu, in 1993 and the M.S degree in electronic engineering from Kyungpook

National University, Taegu, in 1995. From 1995 to 2000, he worked with System IC design team, LG Semicon. Ltd and Hyundai Microelectronics, Ltd. His current research interests are the Growth of III-Nitride Semiconductor using MOCVD and Gallium Nitride devices

Hyun-Ick Cho He was born in Taegu, Korea, in 1974, He received the B.S and M.S degree in Electronic Engineering from Kyungpook National University, Taegu, korea in 2000 and 2002 respectively. He is currently

pursuing the Ph.D degree in Department of Electronics, Kyungpook National University, where His research interest is growth of GaN - based materials and devices fabrication.

Eun-Jin Lee She received the B.S. degree in Electric and Electronics engineering from Kyungpook National University, Korea, in 2004. Currently, she is studying at Kyungpook National University. Her research interests

include AlGaN/GaN MIS-HFET and HFET device.

Sung-Ho Hahm He was born in Wonju, Korea, in 1962. He received the B.S. degree in electronic engineering from Kyungpook National University, Taegu, in 1985, and the M.S. and Ph. D. degrees from Korea

Advaced Institute of Science and Technology(KAIST), in 1987 and 1991, respectively. His doctoral research topic was a lensed LED using the LPE melt back effect. From 1992 to 1996, he was with Korean Ministry of Trade and Industry as a Deputy Director for semiconductor Division.

He has been with Sensor Technology Research Center and school of electronic and electrical engineering at Kyungpook National University since 1996. His current research interests are vacuum micro-electronic devices and III-nitride devices.

Jung-Hee Lee He was born in Taegu, Korea, in 1957. He received the B.S. and M.S. degree in electronic engineering from Kyungpook National University, Taegu, in 1979 and 1983, and he received the M.S. degree in

electrical and computer engineering from Florida Institute of Technology in 1986. He received the Ph.D. degree in electrical and computer engineering from North Carolina State University in 1990. His doctoral research concerned carrier collection and laser properties in monolayer-thick quantum well heterostructures. From 1990 to 1993, he joined Electronics and Telecommunication Research Institute(ETRI), Daechun, Korea, where he worked in compound semiconductor research group. From 2002, he has been professor of school of electronic and electrical engineering at Kyungpook National University. His current work is focused on atomic layer epitaxy(ALE), and Gallium Nitride-based electronic devices.