# 실리콘 포토닉스 기술

Silicon Photonics

| 정보통신 | 미래기술 | 특집 |

|------|------|----|

|      |      |    |

박래만 (N.M. Park) 신재헌 (J.H. Shin) 허철 (C. Huh) 김경현 (K.H. Kim) 김태엽 (T.Y. Kim) 성건용 (G.Y. Sung) 정태형 (T.H. Zyung) 신기능정보소자팀 선임연구원 신기능정보소자팀 선임연구원 신기능정보소자팀 선임연구원 신기능정보소자팀 선임연구원 신기능정보소자팀 연구원 신기능정보소자팀 팀장 미래기술연구본부 본부장

#### 목 차

- 1 . 서론

- Ⅱ. 실리콘 포토닉스 기술의 응용

- Ⅲ. 집적화

- Ⅳ. 국내외 연구 현황

- V . 결론

실리콘 포토닉스 기술은 차세대 실리콘 기술로서 optoelectronic integrated circuit을 위한 실리콘 기반 광기술에 대한 것이다. 본 고에서는 이러한 실리콘 포토닉스 기술을 이용한 단일 집적화에 있어서 응용과 문제점 및 연구개발 동향에 대해 알아본다. 특히, 세부 기술들에 대한 현재의 기술적 수준을 단일 집적화 측면에서 검토하였으며, 가장 큰 문제점으로 인식되는 실리콘 발광원의 국내외 기술 현황을 살펴보았다.

### I. 서론

1Gb/s 이상의 데이터 전송속도를 갖는 광전송 기술에 대한 그 요구는 점점 증가하고 있다. 이와 같은 고속 전송기술은 전자전송기술로는 한계가 있어보인다. 그 이유 중에 하나가 전송속도가 증가할수록 전송거리가 크게 줄어들기 때문이다. 그러나, 만약 실리콘 광집적 칩이 개발된다면 가격과 소비전력 및 소자 크기에 있어서 차세대 통신산업에 일대 혁신을 불러일으킬 것이다.

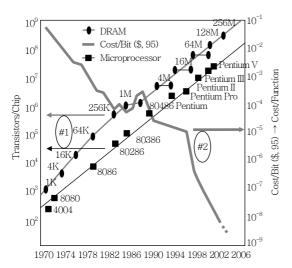

본 기술에서는 실리콘 포토닉스 소자기술에 대해 알아본다. 현재 하나의 초고속 마이크로 프로세서 칩에는 5억 개 이상의 트랜지스터가 들어 있으며, 실리콘은 반도체 시장에서 가격과 기술적인 이점을 여전히 누리고 있어서 산업 및 기술연구 분야에서 가장 매력적인 전자재료로 평가되고 있다. 이러한 기술의 진보는 더 싸고 더 고성능의 제품을 생산할수 있는 여건을 만들었다. (그림 1)은 1970년 이후 칩 당 트랜지스터의 증가율과 단위 프로세스 당 비용 감소율을 보여준다.

만약, 실리콘 포토닉스가 이와 유사한 기술발전을 이룬다면 아마도 놀라운 통신환경을 창조해 낼 것이다.

(그림 1) 칩 당 트랜지스터의 개수 및 단위프로세스 당 비용

광소자는 파장에 의해 그 크기가 제한을 받는다. 예를 들어, 실리콘은 굴절률이 높기 때문에 굴절률이 작은 다른 물질보다 더 작은 광소자를 제작할 수 있다. 그러나, 측벽에 의한 손실이나 커플링 또는 편광 손실과 같은 해결해야 할 과제도 남아 있다[1]. 많은 전문가들은 아직까지 양질의 광소자를 실리콘으로 제작하기에는 한계가 있다고 생각한다. 세가지 중요한 문제점으로 광원, 고속 광변조기, 광접속기를 들고 있다. 그러나, 화합물 반도체를 접목한 광집적 기술에 있어서도 재성장에 의한 여러 가지 문제들로 인해 여전히 가격이나 성능에서 큰 진보를이루지 못하고 있다. 따라서, 실리콘 기반의 포토닉스 기술이 개발된다면 저가의 그리고 양질의 광전 집적 소자를 제작할 수 있을 것으로 기대된다.

# Ⅱ. 실리콘 포토닉스 기술의 응용

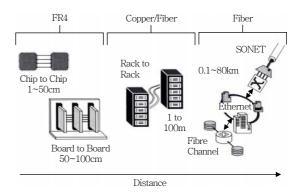

현재 단거리는 전자통신이, 장거리는 광통신이 그 역할을 담당하고 있으며, 100m 이상의 거리에서 도 1Gb/s 이상의 속도를 유지하고 있다. (그림 2)는 거리에 따른 통신기술을 보여주고 있는데 광통신 기술은 1550nm 파장을 이용하여 레이저, 증폭기, 다중분할기 등으로 현재 활용되고 있다. 1~100nm 통신영역은 구리배선과 광연결이 공존하는 영역이다. 여기에서 이용되는 광기술은 상대적으로 단순하다. 더 짧은 거리의 통신영역에서는 구리배선을 이용한 정보전송 수단이 거의 이용되고 있다.

(그림 2) 거리에 따른 통신기술

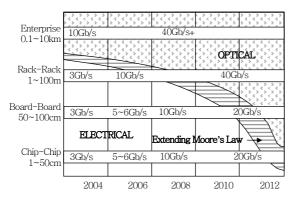

(그림 3)은 데이터 전송속도와 전송거리에 따른 전자통신과 광통신의 기술발전 추이를 나타내는 그 림이다. 정확하게 예측하기는 어렵지만 보드간 또는 랙간의 광전송 기술은 곧 실현될 것으로 기대된다. 칩간의 광전송 기술은 다른 응용영역과는 요구사항 들이 달라서 좀 더 시간이 걸릴 것으로 예상된다.

반도체 칩셋의 기본적인 구조에서 보면 지난 20년 동안 마이크로 프로세서의 속도는 급속도로 증가하지만 마이크로 프로세서와 메모리 조절 허브와의접속 버스기술은 이것을 따라가지 못하고 있다. 이것은 컴퓨터의 속도가 마이크로 프로세서의 속도에의해 좌우되지 못함을 의미한다. 유사한 문제는 멀티 프로세서에도 존재하게 된다. 이것을 극복하기위해 캐시 메모리를 사용하고 있지만 근본적인 해결책은 아니다. 많은 연구들이 이 문제를 해결하기위해 광연결에 대한 기술을 개발중에 있다.

칩간 광연결을 위해 현재 제안되는 기술은 크게 세 가지이다. 첫째는 단일 집적화이고[2], 둘째는 부분 이종 집적화[3], 셋째는 완전 이종 집적화이다 [4]. 단일 집적화란 실리콘 기판 위에 실리콘 광원과 광검출기를 모두 적층하는 것을 의미하며, 부분이종 집적화는 광원은 외부에 있고 광검출기만 칩에 집적된 것을 말한다. 그리고, 완전 이종 집적화는 화합물 광원과 광검출기가 실리콘 기판 위에 모두 접합되는 것을 말한다. 어떤 것이든 2010년까지 각 채널 당 전송속도 20Gb/s, 제작비 10달러 이내를 목표로 하여 개발되고 있다. 단일 집적화에서는 실리

(그림 3) 전자통신과 광통신의 기술발전 추이

콘 광원이 가장 큰 문제점으로 10년 이상 이 부분에 대해 많은 연구가 진행되고 있다[5]. 변조기 부분에 있어서는 SOI 기판이나 특수 기판을 사용하여 waveguide 형태의 실리콘 소자로 극복하고 있다. 하지만, 전자소자와 접목하기에는 전기적 특성에 대한 최적화 연구가 필요하다. 따라서, 화합물 반도체레이저를 광원으로 이용하는 이종 집적화가 차선책으로 여겨지고 있다. 통신용 파장을 선택하는 것 또한 매우 중요한데 1100nm 보다 짧은 파장은 실리콘이 흡수하기 때문에 waveguide나 변조기에서 loss가 심하게 일어나고, 1550nm 파장을 이용하면 SiGe 광검출기를 이용할 수 있지만 비용이 증가하게 된다. 또한, 상업적으로 이용할 만한 SiGe 광검출기는 아직 개발되지 않았다. 그래서 1000~1310nm 파장이 가장 활용 가능성이 있는 것으로 여겨진다.

광통신에 있어서 실제적인 문제점 중에 하나가 광소자 주변의 온도이다. 실제 동작하는 마이크로 프로세서의 중심온도는 약 100도 정도이고, 가장 낮은 주변온도도 50도가 넘는다. 따라서, 화합물 반도체 광원이 오랜 시간 수명을 유지하기에는 열악한환경이다. 미래의 실리콘 광원 역시 고온에서는 출력 세기가 감소할 것이다. 변조기나 검출기 같은 다른 소자들도 고온에 의해 굴절률이나 전류, 효율 등이 변하기 때문에 성능에 크게 영향을 받을 것이다. 이것이 앞으로 해결해야 할 과제로 남아 있다.

Moore의 법칙에 의하면 CMOS가 발전함에 따라서 동작전압도 감소한다. 현재 마이크로 프로세서의 동작전압은 1.3V이다. 이러한 규정에 크게 위배되지 않는 범위에서 다른 광소자들도 동작하여야 하는데 그 기준값이 대략 10V 정도이다. 이것도 전하펌프를 사용할 경우로써 특별한 회로를 필요로 한다.

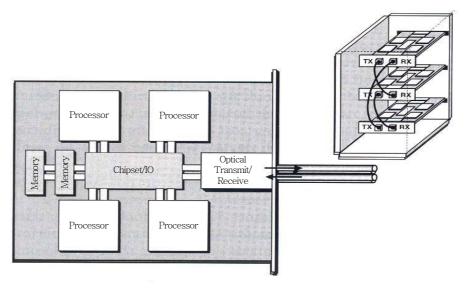

실리콘만큼 비용이나 소자크기 면에서 유리한 반도체가 없기 때문에 광원이 필요 없는 병렬 집적화에는 실리콘이 이점을 가지고 있다. 따라서, 칩간 광통신보다 좀더 장거리에 속하는 보드간 또는 랙간 광통신에 있어서 실리콘 포토닉스는 세 가지 장점을 갖는다. 1) 장거리 광통신보다는 단거리이기 때문에일반 광통신에서 필요로 하는 몇몇 기능이 필요가

(그림 4) 보드간 광통신의 예시도

없다. 2) 데이터 전송에서 서버와 컴퓨터가 더 중요한 비중을 차지한다. 3) 단거리이기 때문에 부품간 신호손실이 크게 문제가 되지 않는다. (그림 4)는 보드간 광통신의 한 예를 보여주고 있는데 트랜시버가 화합물 반도체 레이저와 실리콘 광검출기로 집적되어 있다. 제시된 응용 환경은 또한 주변온도가 60도이하이고, 동작전압이 10V 이상으로 칩간 광통신보다 비교적 유리하다.

#### Ⅲ. 집적화

집적화를 하는 이유는 성능이 향상되고 그만큼 비용이 절감되기 때문이다. 많은 수의 동일한 트랜 지스터를 한 칩에 집적시키는 전자소자 집적화와는 달리 광소자 집적화는 서로 다른 기능을 하는 소자 들을 집적하는 것이다. 단일 집적화의 일반적인 개 념은 모든 소자들을 기판과 동일한 재료로 제작하는 것을 의미한다.

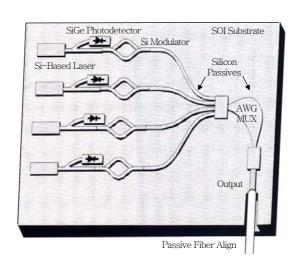

(그림 5)는 단일 집적화의 한 예로써, 실리콘 광원과 SiGe 광검출기, 실리콘 변조기, 실리콘 waveguide 등이 실리콘 기판 위에 제작되어 있다. 좀더폭넓은 의미의 단일 집적화는 화합물이나 고분자 소

(그림 5) 단일 실리콘 집적화 예시도

자가 실리콘 기판 위에 적충될 수 있다. 이것은 소자 선택에 있어 보다 유연성이 있지만, 실리콘의 장점 을 살리기 위해 주로 광원에 제한된다.

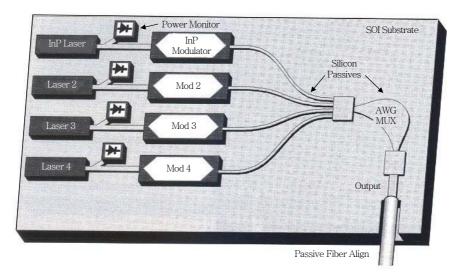

이종 집적화는 (그림 6)에서처럼 서로 다른 재료로 된 소자를 동일 기판 위에 집적하는 하는 것으로이 기술의 장점은 기능별로 가장 우수한 소자들을이용할 수 있다는 것이다.

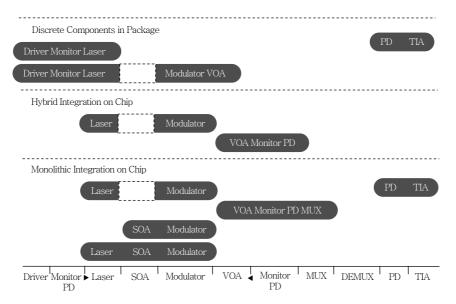

(그림 7)은 어느 소자들이 함께 집적화 될 수 있는지를 보여준다. 소자 서열은 일반적인 광연결에서

(그림 6) 이종 집적화 예시도

(그림 7) 상용화된 소자를 이용한 집적화 방법

나타나는 서열을 따르고 있다. 단일 집적화에서는 광검출기와 광증폭기를 제외한 거의 대부분의 소자 가 InP로 구현된다.

집적화된 광부품들은 30년 전이나 크게 나아진 것이 없지만 전자소자의 경우에는 실리콘 공정기술의 발전으로 인해 성능이 크게 진보하고 있다. 이러한 실리콘 전자소자의 기술적 성숙이 광전 집적화연구 개발에 큰 영향력을 행사하고 있어서 실리콘

포토닉스는 매우 큰 이점을 가지게 된다. 더불어 기존의 공정들을 사용할 수 있기 때문에 연구 및 생산비용을 크게 낮출 수 있는 장점도 있다. 그러나, 실리콘 기반의 이종 집적화 기술은 근본적으로 비용절감에 한계가 있기 때문에 단일 실리콘 집적화 기술이 최종 목표가 될 것이다. 이를 위해서는 새로운실리콘 광부품 연구에 대한 투자가 더 활성화되어야한다.

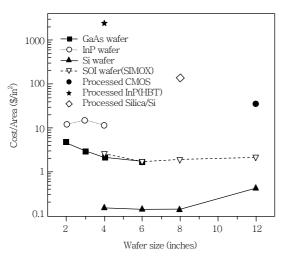

(그림 8)은 몇몇 광반도체 단가와 소자제작 비용을 나타내고 있다. InP 물질이 가장 재료단가가 비싼 것을 알 수 있다. 또한, 5가지의 메탈을 패턴 중착하는 실리콘 공정의 경우 제조단가는 약  $40/\text{in}^2$ 달러이지만, InP DFB laser의 경우에는  $2000/\text{in}^2$ 달러가 넘는다. 이러한 정보는 집적화의 경우에 어떤물질로 각 부품을 제작할지를 결정하는 데 중요한변수가 된다.

이처럼 실리콘 단일 집적화에 대한 장점에도 불구하고 아직까지 실리콘 평면 광소자와 전자소자를 접목하려는 노력이 결실을 맺지는 못하고 있다. InP는 우수한 광소자와 우수한 전자소자를 동시에 구현할 수 있는 전형적인 물질이지만, 기술적 어려움과수요부족으로 산업계에서는 이를 상용화하는 것을 포기하고 있다. 가장 큰 요인은 위에서 언급했듯이높은 제조비용이다.

비용 측면 외에 단일 집적화 기술이 갖는 이점은 소자정렬과 계면 문제가 매우 적다는 것이다. 이 경우에 정렬문제는 패턴 기술에 의해서만 좌우되고 비슷한 굴절률을 갖는 물질을 이용하기 때문에 계면에 의한 정보손실이 매우 적다.

전자소자와는 달리 광소자는 쉽고 빠르면서 하나의 공정 테스트가 최종결과를 예측할 수 있는 검사 방법이 없다. 따라서, 광전 집적화된 시스템의 성능 테스트는 간단하지 않고 자동화하기가 쉽지 않다. 현재 가장 유력한 방법은 프리즘이나 그레이팅 또는 테이퍼를 이용한 waveguide형 검사법이다. 이것은 광손실이나 투과에 대한 정보를 얻을 수 있다.

광소자 테스트에서 문제가 될 수 있는 다른 한 가지는 결함 검사이다. 이것도 전자소자와는 달리 광소자에서는 완성된 방법이 없다. 실제로 guide와 cladding 층 사이의 굴절률 변화는 가장 잘 알려진문제 중에 하나이다. 이 변화는 결함이나 조성 및 두께 불균일 등에 의해 야기된다.

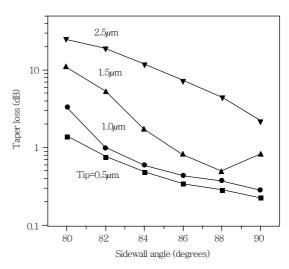

빛을 실리콘 칩과 결합시키는 것은 집적화에 있어서 어려운 기술이다. 특히, 광섬유와 waveguide 사이의 광결합은 모드 불일치로 인해 가장 어렵다. 이 문제도 효율적인 실리콘 광원이 개발된다면 어느정도 극복이 되겠지만 다른 광원을 이용하는 이종 집적화 기술에서는 필연적으로 발생하는 문제이다. 하지만, 이 문제를 최소한 줄이기 위해서 테이퍼 기술을 적용한다. 이 기술은 또한 광소자를 효과적으로 정렬하는 데에도 유용하다. 이 중에서도 (그림 9)는 pseudo-vertical 테어피링 기술의 특징을 보여준다. 측벽 가도가 90도이고 팁의 크기가 500nm일 경우에 결합 손실률은 약 0.2dB 정도로 매우 작다. 이 기술의 핵심은 테이퍼의 길이와 폭이다. 손실을줄이기 위해서는 팁의 폭을 줄여야 한다.

(그림 8) 광반도체들의 재료비 및 소자 제조단가

(그림 9) 테이퍼의 측벽 각도에 따른 광 결합 손실률

(그림 9)에서는 측벽 거칠기에 의한 손실이 없고, 전송파장 1550nm, 테이퍼 길이를 1mm로 가정했 을 경우이다.

그러나, 아쉽게도 현재의 에칭 기술로는 팁을 날 카롭게 만들기가 매우 어렵다. Grayscale 인쇄법을 이용할 수도 있지만 추가 비용이 들며 복잡하다는 문제점이 있다. 테이퍼 제작공정에서 또 다른 문제점은 측벽 거칠기에 의한 손실이다. 이 손실은 waveguide 크기에 의존하기 때문에 팁에서 손실이가장 크게 나타난다. 따라서, 팁에서의 측벽 및 표면거칠기를 최소화하는 것이 손실을 줄이는 방법이다. 또한 테이퍼의 측면 각도가 중요하다는 것을 (그림 9)에서 알 수 있다. 각도가 80도에서 90도로 향상될 경우에 손실은 거의 10분의 1로 줄어들게 된다. 다른 대안들이 계속해서 연구되고 있는데 이것에 대해서는 참고문헌 [1]을 참고하기 바란다.

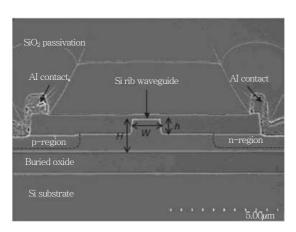

실리콘 광원이 없는 이상 광전 집적화를 위해서 는 화합물 반도체 광원을 이용해야 한다. 이 경우에 레이저를 정렬시키는 기술이 또한 중요하게 된다. 정렬기술에는 두 가지가 있는데, 하나는 실시간으로 레이저 정렬을 조절하는 능동 조절법이다. 그런데, 이 기술에서 레이저를 조절하기 위해 필요한 전자소 자들이 복잡하고 크기에 문제가 있다. 쉽게 조정하 기 위해서는 커야 하는 반면 정렬을 쉽게 하기 위해 서는 작은 것이 유리하다. 다른 방법은 정렬을 위한 전자소자가 필요 없는 수동 조절법이다. 이종 집적 화의 단점인 고비용을 어느 정도 해결하기 위해서는 이 수동 조절법이 유리하다. 수동 조절법에서 레이 저를 정렬시키는 것은 waveguide의 크기나 모양, 시스템에 따라 다르지만 보통 1µm 이하의 위치 정 확성을 요구한다. 이 정확도는 접합기술이나 식각 기술에서는 고도의 정밀성을 요구하기 때문에 보다 쉽게 충족시키기 위해 pillar를 사용한다. Pillar는 식각법에 의해 만들어지기 때문에 위치를 정확히 제 어할 수 있다. (그림 10)은 실리콘 기판 위에 화합물 반도체 레이저가 장착된 단면 그림이다.

레이저를 접합하기 위해서는 일반적으로 금을 사용하는데 레이저 주변의 trench의 깊이가 대략 5내

(그림 10) 화합물 반도체 레이저가 장착된 단면

지 15 $\mu$ m이다. 따라서, 금속 패턴의 크기나 높이 등이 광인쇄법의 정확도에 크게 의존하게 된다. 또한, 광손실을 줄이기 위해 소형 렌즈를 사용하기도 하지만 제조비용을 증가시키는 요인이 된다.

일반적으로 측면 레이저의 광모드는 near field 에서 타원과 수평 모드이고, far field에서 수직 모드이다. 반면, SOI waveguide는 비대칭 모드이다. 따라서, 레이저와 SOI waveguide의 모드 중첩을 증가시키기 위해서는 하나 또는 두 개의 광모드가 레이저에서 waveguide로 전달되어야 한다. 이를 위해서 모드 변환기가 이용된다. 그러나, 아직까지 반도체 레이저 die에 적용된 적이 없다.

#### Ⅳ. 국내외 연구 현황

실리콘 포토닉스의 중요성을 외국에서는 이미 일찍 간파하고, 이를 실용화 하고자 하는 노력이 산한 연 전반에 걸쳐 광범위하게 이루어지고 있다. 이중 높은 impact의 연구를 가장 활발하게 진행하고 있는 국가는 아무래도 Silicon Valley와 Boston High Tech Corridor를 보유하고 있는 미국이라고할 수 있다. Intel사의 경우 silicon photonics 전담연구실을 운영하고 있으며, 이를 바탕으로 1GHz modulator, Raman laser((그림 11) 참조) 등 최첨단 기술 개발에 성공하여 이를 Nature 등 최고 권위의 잡지에 연달아 발표하고 있다[6]. 또한 Caltech의 Kerry Vahala 교수와 Axel Scherer 교수가 참여하고 있는 벤처회사인 Luxtera에서는 Intel의 결과를 뛰어넘는 10GHz modulator의 개발에 성공하여 New York Times에 소개된 바 있다.

(그림 11) Intel에서 제작한 실리콘 라만 레이저의 단면 구조

대학의 경우 Stanford의 Mark Brongersma 교수가 plasmonics를 연구하고 있으며, Caltech의 Kerry Vahala 교수는 silica toroidal ultra-high Q cavity를 응용한 레이저, 센서 등 다양한 광소자의 성공적 개발을 발표해오고 있다. 동부에서는 Cornell의 Michal Lipson 교수가 SOI 기술을 이용한 modulator, switch 등 다양한 나노 전광소자들을 성공적으로 개발하고 있으며, Univ. of Rochester 에서는 Phillippe Fauchet 교수가 나노결정 실리콘을 이용한 전광소자들을 연구하고 있다. 이들의 연구결과는 Nature 등의 최고 권위의 잡지에 지속적으로 발표되고 있으며, MIT에서 발행하는 Technology Review지 2005년 5월호에 발표된 미래 10대기술 중의 하나로 실리콘 포토닉스 기술이 선정되었다.

이러한 연구들은 국가의 전반적인 지원 없이는 성공할 수 없다. 현재 미국의 AFSOR는 실리콘 포토 닉스의 개발을 다양한 연구과제를 통해 적극적으로 지원하고 있으며, DARPA 역시 EPIC를 통해 실리 콘 포토닉스를 지원하고 있다.

국내의 경우 이러한 실리콘 포토닉스에 관한 연구에 가장 이상적인 조건을 갖추고 있다고 할 수 있다. 이미 국내의 실리콘 반도체 공정 기술과 인력은 세계 최고이며, 최근 나노팹의 설립에 따라 나노기술 및 공정에도 세계적 수준에 도달하고 있다. 또한

폭넓은 초고속 인터넷 망의 보급에 따라 광통신 망역시 세계 최고의 수준을 유지하고 있으며, 광기술에 대해서도 세계적 결과를 꾸준히 발표하고 있는 연구그룹들이 다수 포진하고 있다. 그러나 불행하게도 이러한 위상과 달리 실리콘 포토닉스를 비롯한 차세대 정보기술을 위한 핵심원천 기술에의 연구는 아직 외국에 비하여 극히 미비하다고 할 수 있다. 현재 한국의 반도체 업체에서 실리콘 포토닉스 기술에 대한 연구 및 투자는 전무한 상태이며, 국가적으로 지원받는 대규모 연구단이 하나도 존재하고 있지 않다.

국내 연구자들을 살펴보면 실리콘 포토닉스를 이 끌어나갈 세계적 수준의 연구를 하고 있는 연구자들이 다수 존재하고 있다. KAIST의 이용희 교수는 광결정 분야에서 세계를 선도하는 연구를 하고 있고, ETRI의 성건용 박사 팀은 (그림 12)와 같은 실리콘 나노결정을 이용한 가시광선 LED 분야에서 세계최고 효율을 가진 LED 구조 개발에 성공하여 이를 발표한 바 있다[7],[8]. 이 외에도 서울대, 고려대, 경희대 등에서 다수의 연구진이 우수한 연구를 발표하고 있어 이들의 연구를 집중하고 조율할 수 있다면 한국이 지닌 우수한 인프라와 조합되어 세계를 선도하는 연구를 수행할 수 있으리라 기대된다.

(그림 12) ETRI에서 개발한 실리콘 발광소자의 전계발광 장면

# V. 결론

이상과 같이 전자소자의 기술발전 흐름과 시스템

의 기능 향상에 대한 기대에 부응하여 광전 집적화가 요구되고 있으며 이를 위해서 실리콘 포토닉스가기술적 및 경제적 이점을 가지고 활발히 연구 개발되고 있다. 하지만, 위에서 언급된 것과 같이 아직까지 많은 문제점들을 안고 있으며 특히 실리콘 광원부재는 큰 문제점으로 대두되고 있다. 그러나, 실리콘 반도체가 지난 30년간 전자소자 분야에서 혁신적인 기술적 진보를 이루어 온 만큼 이제 막 시작되고 있는 실리콘 포토닉스 기술에서도 앞으로 놀라운진보가 있을 것으로 기대된다.

# 약어 정리

| CMOS | Complementary Metal-Oxide           |

|------|-------------------------------------|

|      | Semiconductor                       |

| DFB  | Distributed Feedback                |

| EPIC | Electronic and Photonics Integrated |

|      | Circuits on Si                      |

LED Light-Emitting Diode SOI Silicon-on-Insulator

#### 참고문헌

- [1] G.T. Reed and A.P. Knights, Silicon Photonics: An Introduction, Wiley Interscience, New York, 2004.

- [2] R. Soref, "Silicon-Based Optoelectronics," *Proc. IEEE*, Vol.81, 1993, p.1687.

- [3] B. Schuppert et al., "Integrated Optics in Silicon and SiGe-heterostructures," J. Lightwave Tech. Vol.14, 1996, p.2311.

- [4] Y. Liu, "Heterogeneous Integration of OE Arrays with Si Electronics and Microoptics," *IEE Trans. Adv. Packaging*, Vol.25, 2002, p.43.

- [5] M. Castagna et al., "Si-based Materials and Devices for Light Emission in Silicon," *Physica E*, Vol.16, 2003, p.547.

- [6] H. Rong et al., "A Continous-wave Raman Silicon Laser," *Nature*, Vol.433, 2005, p.725.

- [7] T.Y. Kim et al., "Quantum Confinement Effect of Silicon Nanocrystals in Situ Grown in Silicon Nitride Films," Appl. Phys. Lett., Vol.85, 2004, p.5355.

- [8] K.S. Cho et al., "High Efficiency Visible Electroluminescence from Silicon Nanocrystals Embedded in Silicon Nitride Using a Transparent Doping Layer," Appl. Phys. Lett., Vol.86, 071909, 2005.