### 송전선 직렬보상을 이용한 순시전압강하 보상기

論 文 55P-1-4

# Instantaneous Voltage Sag Corrector Using Series Compensator in Transfer Power Line Generator

李尚勳\*·洪鉉文<sup>†</sup>·閔完基\*\*·全炳錫\*\*\*·李大鍾\*\*\* (Sang-Hoon Lee·Hyun-Mun Hong·Wan-Ki Min·Byeong-Seok Jeon·Dae-Jong Lee)

Abstract - This paper describes the novel control techniques design of VSC(Voltage Sag Corrector) for the purpose of power line quality enhancement. A fast detecting technique of voltage sag is implemented through the detection of instantaneous value on synchronous rotating dq-reference frame. The first order digital filter is added in the detection algorithm to protect the insensitive characteristics against the noise. The relationship between the total detection time and cut-off frequency of the filter is described. The size of the capacitor bank used as the energy storage element is designed from the point of view of input/output energy with circuit analysis. Finally, the validity of the proposed scheme is proven through the simulated results.

Key Words: VSC(Voltage Sag Corrector), Power Quality, Faults, Series Compensation, PSCAD/EMTDC

#### 1. Introduction

The voltage sag is the most frequent problem among them, and it is caused by the following two reasons. One is the line fault, especially SLGF(Single Line-to-Ground Faults). The other is caused by the load characteristics, for example motor starting. Until a few years ago, the voltage sag seldom affected to most of system. But it can induce the fatal results to the load today; automatic manufacturing processor using computer electronic equipment with high accuracy, sensitive communication equipment, and high-technology medical facilities. So the regulation of the line voltage or the compensation of the line voltage sag has become one of the most prolific issues in the power quality industry.[1]

It proposed that the CVTs(Constant Voltage Transformers) for the compensation of voltage sags.[1]

This is easy and economic to install, but not efficient under the variable load condition or the large inrush current condition as the fixed output voltage. The UPS(Uninterruptible Power Supply) is more excellent than CVTs, which can generates the constant voltage and constant frequency ac power at any load conditions. But

it needs frequent maintenance and repair, and its cost is too high. So it is not proper to apply to the power distribution line. The other solution is a VSC(Voltage Sag Corrector) using series compensator. The VSC protects the sensitive load against the voltage sag at the PCC(Point of Common Coupling). This scheme has a good dynamic characteristics and relatively economical advantage to the former case, so the research has progressed in active. But the existing studies made no mention for the following terms in spite of the importance. [2]~[6]

- 1. Fast detecting technique when the voltage sag occurs

- 2. Insensitive operation against the noise

- 3. Design process for the rating of an energy storage system (dc capacitor)

This paper proposes the novel control techniques of VSC to overcome the above limits. The fast detecting technique of voltage sag is accomplished through the detection of instantaneous value on synchronous rotating dq-reference frame. The robust characteristic against the noise is available by inserting the first order LPF(Low Pass Filter) in the detection circuit. The relationship between the detecting speed and the cut-off frequency of the filter is induced as a numerical formula. Because the VSC system supplies the active power to load, it is required to design the proper size of the ESS(Energy Storage Element), such as the capacitor bank, battery or

E-mail: hmhong@unikorea.go.kr

接受日字: 200年 5月 25日 最終完了: 200年 1月 27日

<sup>\*</sup> 正 會 員:(予)포스콘 技術研究所 研究員・工博

<sup>†</sup> 교신저자, 正會員: 統一俯 行政事務官・工博

<sup>\*\*</sup> 正 會 員: 朝鮮理工大學 電氣電子科 制教授・工博

<sup>\*\*\*</sup>正 會 員: 忠北大學校 電氣工學科

flywheel system, and etc. In this paper, the capacitor bank is used as an ESS, and the size of the capacitor is designed from the point of view of input/output energy as the output power rating and the magnitude and duration time of the voltage sag. The filter design process is described properly with the mathematical equations. This paper consists of 4 terms: basic theory of the VSC, detection method of the line disturbances, design of the DC capacitor and simulation results.

#### 2. Basic Theory of The VSC

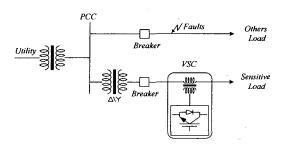

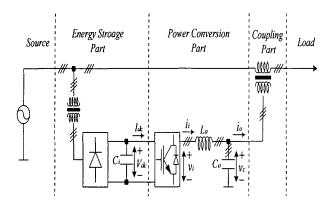

Fig. 1 shows the basic configuration of VSC system in distribution. In a caseof a fault on one of the other feeders from the utility or a fault somewhere on the distribution line, the sensitive load will experience a voltage sag during the period that the fault is actually on the system. As soon as breakers open to clear the fault, normal voltage will be restored to the customer.

#### 2.1. Faults and series compensation

Voltage sags and interruptions are generally caused by faults(short circuits) on the utility system. Most faults are generated from natural phenomenon such as lightning, weather condition, tree branch or animal(bird) contact, and insulation failures or human activity. SLGF(Single Line-to-Ground Fault) is the most common event and rarely a DLGF(Double Line-to-Ground Fault) or TLGF (Three Line-to-Ground Fault) is happened. The vector diagram and magnitude of voltages under SLGF condition for  $\Delta/Y$  connected transformer is shown in Fig. 1 and Table 1 respectively. As shown in Table 1, the secondary voltage is 58% of nominal voltage for  $\Delta/\Delta$  or  $\Delta/Y$  connection in case of SLGF condition and the voltage compensation is considered concretely.

Fig. 1 Control block diagram

There are many kinds of method to regulate the load voltage, such as UPS, CVTs, VSC, and etc. The series compensation has the advantage of the parallel system in power rating of compensator and dynamic response.

The proposed VSC in this paper is the series compensator similar in structure to the existing TCSC

(Thyristor Controlled Series Compensator). But VSC is different from TCSC in objective and control method. In general, the objective of TCSC is to maximize the transmission power rating by the control of line impedance, otherwise VSC supplies active power to load by the control of secondary voltage of series transformer using power conversion equipment.

Table 1 Transformer secondary voltage(p.u.) under SLGF condition.

| Transformer secondary voltage |          | $\Delta/Y$ | $\Delta/\Delta$ | Y/Y  |

|-------------------------------|----------|------------|-----------------|------|

| Line-to-Line<br>Voltage       | $V_{ab}$ | 0.88       | 0.58            | 0.58 |

|                               | $V_{bc}$ | 0.88       | 1.00            | 1.00 |

|                               | $V_{ca}$ | 0.33       | 0.58            | 0.58 |

| Phase Voltage                 | $V_a$    | 0.58       | _               | 0.33 |

|                               | $V_b$    | 1.00       | ~~              | 0.88 |

|                               | $V_c$    | 0.58       | -               | 0.88 |

#### 2.2. System and Control Algorithm

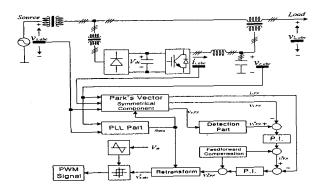

The general requirements to be met by a voltage sag corrector are the following; fast dynamic response, robust characteristic for noise, and insulation of harmonics. The last requirement is not mentioned in this paper. The control block diagram is shown in Fig. 2. The proposed control scheme is based on instantaneous control scheme with double control structure to improve dynamic response. During the fault conditions, the controller is operated constantly to keep the load voltage. Otherwise during normal conditions, the DC capacitor is charged from source and the controller is not operated at this time.

The proposed controller is consisted of 4 parts; detection part, PLL part, feedforward and feedback compensator with general PI( Proportion Integrator) controller, and PWM part. In general, the feedforward compensator has two main objects. First, it can remove the coupling terms which is resulted in synchronous reference frame transformation. Second, inherent disturbances which is included in the inverter system, can be canceled by feedforward compensation of capacitor voltage and load current. Moreover, the dynamic response of controller can be improved in the predictive technique of load current.

The feedback compensator is double control structure which is combined with voltage controller as outer loop and current controller as inner loop. Because the response of capacitor voltage is very slow, fast dynamic response is available by the adding a reactor current controller. The significant issue in the feedback compensator must be decided in the reference voltage. In the next, the positive and negative symmetric components of injected voltage to load are given by:

Fig. 2 Control block diagram

$$v_{c,P} = v_{ref,P} - v_{s,dqP} \tag{1a}$$

$$v_{c,N} = v_{ref,N} - v_{s,dqN} \tag{1b}$$

where,  $v_{ref,\,P}$  is a peak value of the source voltage and  $v_{ref,\,N}$  is zero. Thus, the capacitor voltage controller is compared with reference voltage and actual load voltage, the difference being supplied by the VSC.

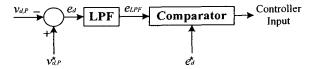

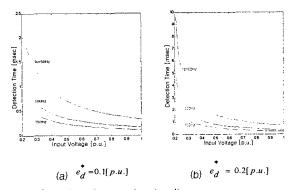

In Fig. 3, if  $e_{LDF}$  is less than  $e_d^*$ , the controller regards  $e_d$  as a noise. As a consequence, total detection time is the time when  $e_{LDF}$  is same  $e_d^*$ . And the total detection time is calculated using transfer function such as (2).

From (2), the relationship between the detection time and cutoff frequency of LPF is shown in Fig. 4. The figure describe that the cutoff frequency is the higher to the detection time is the shorter, but sensitivity for noise is increased.

$$T_{\text{det}} = -\frac{1}{2\pi f_c} \ln \left( 1 - \frac{e_d^*}{e_d} \right) \tag{2}$$

Fig. 3 Detection block diagram.

Fig. 4 Detection time vs input voltage

#### 2.3. Design of DC Capacitor

Generally, the VSC consists of three parts: energy conversion part, energy storage part, and coupling part. Specially, because the VSC system supply the active power to load, it is required ESS, such as capacitor with rectifier, battery, FES, and SMES. In this paper, the capacitor is used as an ESS.

The capacitor is charged from source in the normal condition, and it supplies the active power to load in the fault condition. The critical issue in the design of the capacitor is amplitude and duration time of the faults. So, if we know those parameters, we can calculate the capacitance from the point of view input/output energy.

First for convenience, it is need assume such as:

- neglect of losses in switching elements and output filter.

- · neglect of losses in transformer

- the capacitor voltage is 1.35 times of line-to-line voltage

From Fig. 5, we can write input/output power such as (3), when load power factor is cos.

$$P_{in} = V_{dc} \cdot I_{dc}[W] \tag{3a}$$

$$P_{out} = \sqrt{3} v_{c,n} i_o \cos \Phi [W] \tag{3b}$$

The input/output energy is given by:

$$W_{in} = \frac{1}{2} C_i (V_{dc} - V_{low})^2 [J]$$

$$= \frac{0.24}{860} \frac{1}{2} C_i (V_{dc} - V_{low})^2 [Wh]$$

(4a)

$$W_{out} = P_{out} \cdot T_{duration} [Wh]$$

(4b)

where, the  $V_{low}$  is lower limit of DC voltage which is mean controllable area of inverter and its value changes according to fault conditions. The T duration is a fault duration time. Thus, if we know output power and T duration, we can calculate the DC capacitance from (4).

$$C_i = \frac{860 \cdot 2 \cdot W_{out}}{0.24 \cdot (V_{dc} - V_{low})^2} [F]$$

(5)

#### 3. SIMULATION RESULTS

The simulation is accomplished by PSCAD/EMTDC using the parameter of Table 2. All variables are changed to per unit, and the voltage in table is mean peak value of phase voltage. The voltage ration of main transformer(  $T_m$  in Fig.5) is 22900/220[V] and  $\Delta/Y$  connected. The winding ratio of series and parallel transformer(  $T_S$ ,  $T_P$

in Fig.5) is 1:1 and the primary of series transformer is connected. The switching element is used IGBT(Insulated Gate Bipolar Transistor) and PWM(Pulse Width Modulation) technique is used triangular wave comparison method.

Fig. 5 Structure of VSC system

The Fig. 6, 7, and 8 are simulated results for VSC's operation under SLGF, DLGF, and TLGF condition respectively. All of the figures show main transformer secondary voltage, compensation voltage, load voltage, DC link voltage, and fault current from top. The fault is sustained for 300 millisecond. The fault resistance and capacitance for fault conditions is shown in Table 3. The simulated results show that proposed VSC has a good dynamic performance and capacitance is well designed by (5).

The Fig. 9 is simulated result for temporary outage. The outage duration time is 100 millisecond and 20[mF] of capacitor is used. From Fig. 9, we can know that the proposed VSC system is able to compensate temporary outage.

Table 2 Simulation parameters

| parameter       | value                    | parameter            | value         |

|-----------------|--------------------------|----------------------|---------------|

| Power<br>rating | 10[KVA]                  | Switching frequency  | 5[kHz]        |

| Voltage         | $311[V_{peak}]$          | Impedance            | $8.4[\Omega]$ |

| Current         | 37.1[A <sub>peak</sub> ] | DC Link<br>Voltage   | 514[V]        |

| Frequency       | 60[Hz]                   | LPF cutoff frequency | 100[Hz]       |

Table 3 Fault resistance and DC capacitance

| Parameters  | SLGF     | DLGF     | TLGF    |

|-------------|----------|----------|---------|

| Resistance  | 0.005[Ω] | 0.005[Ω] | 1.5[Ω]  |

| Capacitance | 5.9[mF]  | 53[mF]   | 5.9[mF] |

#### 4. CONCLUSION

This paper has presented power quality enhancement through compensation using VSC for instantaneous voltage sag caused by faults in distribution line. The simple detection algorithm which is implemented in synchronous reference frame, has a fast detection time. The robust characteristic against the noise is available by inserting the LPF. Also the relationship between the detection time and the cut-off frequency is induced in a numerical formula. The DC capacitor is designed from point view of input/output energy as the output power rating and the amplitude and duration time of the faults. The simulated results is shown that the proposed scheme has a good performance and protects to sensitive load for temporary outage.

#### References

- Mark F. McGranaghan et al, "Voltage Sags in Industrial Systems", IEEE Trans. on Industry Applications, Vol.29, No.2, pp.397-403, March/April, 1993.

- [2] Alexander Kara et al, "Power Supply Quality Improvement with a Dynamic Voltage Restorer(DVR)", IEEE APEC, Vol.2, pp.986-993, 1998.

- [3] R. Tounsi et al, "Series Compensator for Voltage Dips: Control Strategy", EPE, pp.4929-4934, 1997.

- [4] G. Joos, "Three-Phase Static Series Voltage Regulator Control Algorithms for Dynamic Sag Compensation", IEEE ISIE, pp.515-520, 1999.

- [5] R. S. Weissbach et al, "Dynamic Voltage Compensation on Distribution Feeders using Flywheel Energy Storage", IEEE Trans. on Power Delivery, Vol.14, No.2, pp.465-471, April, 1999.

- [6] M. F. Granaghan, "Dynamic Sag Corrector: Cost Effective Industrial Power Line Conditioning", IEEE IAS, pp.1339-1344, 1999.

- [7] G. Andria et al, "Inverter Drive Signal Processing via DFT and EKF", IEE Proc., Vol.137, pt. B, March, 1990.

## 저 자 소 개

#### 홍 현 문 (洪 鉉 文)

1965년 11월 11일생. 1992년 충북대 전기공 학과 졸업. 1994년 동대학원 졸업(석사). 2002년 동대학원 졸업(박사). 1998년 3월 ~ 2005년 11월 동해대학교 전기전자공학과 조 교수. 2005년11월 ~현재 통일부 행정사무관.

Tel: 02-2100-5903, Fax: 02-2100-5899

E-mail: hmhong@unikorea.go.kr

#### 이 상 훈 (李 尙 勳)

1969년 7월 13일생. 1994년 충북대학교 전 기공학과 졸업. 1997년 동 대학원 졸업(석 사). 2001년 박사 졸업. 2001년 6월~현재 (주)포스콘 기술연구소 근무. IEEE, KIEE, KIPE 정회원.

Tel: (02) 3290-4447

Fax: (02) 925-1812

E-mail: shlee@poscon.co..kr

#### 민 완 기 (閔 完 基)

1989년 충북대학교 전기공학과 졸업. 1993년 동 대학원 졸업(석사). 2000년 동 대학원 졸업(박사). 1988년~1991년 LG 연구원 및 LG 반도체 근무. 1994년~1997년 한전전력연구원 연구원. 1997년~2003년 현재

조선이공대학 전기과 부교수, 2001년 1월~2001년 7월 일본 치토세과학기술대학 객원교수. 2004년 3월~2006년 현재 대 한전기학 P권 편집위원

Tel: (062) 230-8357

E-mail: wkmin@mail.chosun-c.ac.kr

#### 전 병 석 (全 炳 錫)

1969년 9월 25일생. 1995년 충북대학교 전기공학과 졸업. 1998년 충북대학교 대학원전기공학과 졸업(석사). 2005년 동대학원 전기공학과 졸업(박사). 2000년-현재 (주) 세화폴리텍 근무. 2005년-현재 충주대학교 정보제어공학과 겸임교수.

Tel: (043) 261-2419

E-mail: koamma88@chungbuk.ac.kr

#### 이 대 종 (李 大 鍾)

1969년 2월 25일생. 1995년 충북대학교 전기공학과 졸업. 1997년 충북대학교 대학원전기공학과 졸업(석사). 2002년 동대학원 전기공학과 졸업(박사). 2003년~현재 충북대학교 컴퓨터정보통신연구소 연구원. 2004년 -2005년 7월 University of Alberta, Postdoctor.

Tel: (043) 261-2419

E-mail: leebigbell@hotmail.com