# New Voltage Programming LTPS-TFT Pixel Scaling Down VTH Variation for AMOLED Display

Woo-Jin Nam\*\*a, Jae-Hoon Lee\*\*a, Hee-Sun Shin\*\*a, Jae-Hong Jeon b and Min-Koo Han a

### **Abstract**

A new voltage-scaled compensation pixel which employs 3 p-type poly-Si TFTs and 2 capacitors without additional control line has been proposed and verified. The proposed pixel does not employ the  $V_{TH}$  memorizing and cancellation, but scales down the inevitable  $V_{TH}$  variation of poly-Si TFT. Also the troublesome narrow input range of  $V_{DATA}$  is increased and the  $V_{DD}$  supply voltage drop is suppressed. In our experimental results, the OLED current error is successfully compensated by easily controlling the proposed voltage scaling effects.

**Keywords**: OLED, Current-scaling, Capacitance

## 1. Introduction

Recently, organic light emitting diodes (OLEDs) displays demonstrate good-features such as high brightness and wide viewing angle by self-emissive characteristics [1]. However, the inevitable current non-uniformity of poly-Si TFT arrays due to the threshold voltage ( $V_{TH}$ ) and the mobility ( $\mu_{eff}$ ) variations, which are caused mainly by crystallization such as excimer laser annealing (ELA), need to be improved for high-quality images [2]. Many pixel circuits have been reported in order to compensate the non-uniform OLED current ( $I_{OLED}$ ) variation by the voltage or current programming methods [2-5].

In voltage programming method, the pixel panel is easily interfaced with the widely used voltage driver. However, each pixel circuit requires various considerations for compensating the V<sub>TH</sub> and mobility non-uniformities of poly-Si TFTs as well as the supply voltage drop in the V<sub>DD</sub> line [3-4]. The compensation pixel circuits use typically 4~6 poly-Si TFTs, 1~2 capacitors, 1~3 scan signals, 1~2 supply voltages. Therefore, the large area consumption of the compensation circuit in pixel layout seems inevitable.

Manuscript received August 27, 2006; accepted for publication September 15, 2006.

Corresponding Author: Woo-Jin Nam

**E-mail**: jhlee@emlab.snu.ac.kr Tel: +02 880-7992 Fax: +02 871-7992

Furthermore, although the recent efficiency improvement of the OLED luminance is desirable, it may cause another side-effect reducing the input data range. Since the required current for full-brightness OLED should be in the 1  $\mu$ A-level, the input voltage range will be determined within 1~2 V due to the high-performance of poly-Si TFTs. The small range of the input data would cause the variation error in the OLED current controls. If the input data range is small, the variation effect of  $V_{TH}$  is dominant for the OLED current variation. The current variation may be too severe with regard to the small  $V_{TH}$  variation ( $\pm 15$  %).

The purpose of our work is to propose a new voltageprogrammed pixel design theory employing the voltagescaled programming. The proposed scheme increases the input data range and compensates the  $V_{TH}$  variation. In this paper, the simulation and experimental results successfully verified the proposed compensation theory.

# 2. Proposed Voltage Scaling Theory

Until now, in the voltage programmed pixel circuits, almost researches related to the high quality AMOLED pixel have focused on the  $V_{TH}$  memorizing and cancellation, which requires rather complicated compen-sation circuits in each pixel [3-5]. However, based on the improvements of the device process uniformity in the near-future, the  $V_{TH}$  variation would be reduced in progress. Therefore, the non-uniformity 'reduction' of poly-Si TFTs rather than the non-

<sup>\*\*</sup>Student Member, KIDS

<sup>&</sup>lt;sup>a</sup> School of electrical engineering, Seoul National University, Seoul, Korea.

<sup>&</sup>lt;sup>b</sup> School of Electronics, Telecommunications and Computer Engineering, Hankuk Aviation University, Gyeonggi-do, Korea.

uniformity 'cancellation' may also be effective and feasible for compensating the non-uniformity.

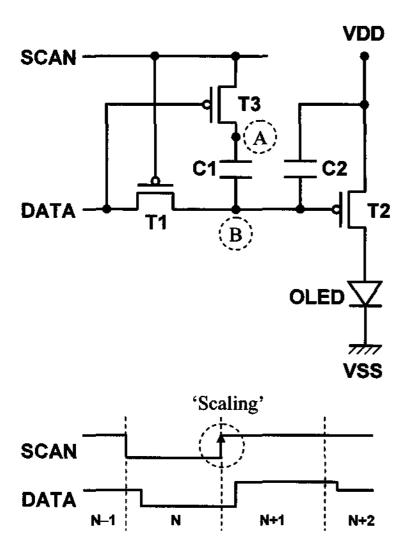

In this paper, we propose a new voltage programming method which compensates the current non-uniformity by the voltage scale-down scheme. Fig. 1 shows the proposed voltage-scale driving pixel, which is composed of 3 p-type poly-Si TFTs and 2 capacitors. The transistor T1 is a switch to address the data voltage (DATA) to pixel, and T2 is a driving transistor to flow an OLED current by its saturation regime. T3 is a transistor for compensation scheme and gives a capacitive coupling of C1 to the gate node of T2. Each capacitor C1 and C2 is a storage capacitor in parallel pair and the storage capacitance  $(C_{ST})$  is C1+C2. In this circuit operation, the data voltage as well as  $V_{TH}$  is modulated and scaled down by the capacitive-coupling through C1 and C2 so that I<sub>OLED</sub> is scaled down and the I<sub>OLED</sub> variation is compensated by scaling down the nonuniform current flows.

Fig. 1. Proposed AM-OLED pixel circuit (3 p-type poly-Si TFTs and 2 capacitors) employing a voltage-scaled programming.

The proposed circuit operates as follows. When the SCAN is turned on from  $V_{DD}$  to  $V_{SS}$  and the DATA is still the previous one  $(V_{DATA.N-1})$ , the voltage  $(V_A)$  of node A is set to  $V_{DATA.N-1} - V_{TH\_T3}$  by T3 and the voltage  $(V_B)$  of node B is set to  $V_{DATA.N-1}$  by T1. T3 is turned off because the SCAN is  $V_{SS}$ . When the present data  $V_{DATA.N}$  is addressed,  $V_B$  is changed to  $V_{DATA.N}$  and  $V_A$  is also changed from  $V_{DATA.N-1} - V_{TH\_T3}$  to  $V_{DATA.N} - V_{TH\_T3}$  by C1 coupling from the node B. The  $I_{OLED}$  flows by T2 without scale-down and

is the same with  $I_{\text{CONV}}$  of the conventional 2-TFT.

$$\begin{split} I_{OLED} &= 1/2 \cdot k \cdot \left( V_{GS\_T2} - V_{TH\_T2} \right)^2 \\ &= 1/2 \cdot k \cdot \left( V_{DATA.N} - V_{DD} - V_{TH\_T2} \right)^2 = I_{CONV} \cdot \cdot \cdot \cdot (1) \\ \text{(Here, k is $\mu_{eff} \cdot C_{OX} \cdot W_{T2} / L_{T2}$ and $V_{TH} < 0$)} \end{split}$$

When the *SCAN* is turned off from  $V_{SS}$  to  $V_{DD}$ , T1 is turned off. T3 is turned on at the condition  $V_{SCAN} > V_{DATA.N} - V_{TH\_T3}$  during the *SCAN* off-transition. The node A is charged by the SCAN from  $V_{DATA.N} - V_{TH\_T3}$  to  $V_{DD}$ . It is noted that the node B is capacitively-coupled by the node A fluctuation  $(V_{fluc})$  of  $V_{DD} - V_{DATA.N} + V_{TH\_T3}$ . Fig. 3-17 illustrates the fluctuation of the node A by capacitive coupling from the SCAN signal. Denoting the node B coupling as  $\Delta V_{B}$ , the  $I_{OLED}$  is expressed as follows,

$$I_{OLED} = 1/2 \cdot k \cdot (V_{DATA.N} + \Delta V_B - V_{DD} - V_{TH\_T2})^2$$

$$= 1/2 \cdot k \cdot \{C2/(C1+C2) \cdot (V_{DATA.N} - V_{DD} - V_{TH\_T2})\}^2$$

$$= \{C2/(C1+C2)\}^2 \cdot I_{CONV} \cdot \dots \cdot (2)$$

Here, the  $\Delta V_B$  is determined by C1 and C2:  $\Delta V_B =$  $\{C1/(C1+C2)\}\cdot V_{fluc}$ . And  $V_{TH}$  of T2 and T3 is assumed to be the same  $(V_{TH T2} = V_{TH T3})$  by the identical line beam irradiation of excimer laser annealing [2,4]. In this equation, the scaling factor ( $\alpha$ ) is defined as C2/ (C1+C2). The I<sub>OLED</sub> of the proposed pixel is finally scaled-down by a factor of  $\alpha^2$  compared with I<sub>CONV</sub> of the conventional 2-TFT. If the capacitance C1 and C2 is the same, the scaling factor  $\alpha$  is 0.5 and the OLED current is scaled down by  $0.5^2 = 0.25$  of the conventional one. The current compensation scheme may be analyzed in equation (2). It is noted that the parameter V<sub>DATA</sub>, V<sub>DD</sub>, V<sub>TH</sub> are scaled down by the scaling factor ( $\alpha$ ). The fact that the addressed  $V_{DATA}$  is scaled down indicates that the V<sub>DATA</sub> input range is scaled up for the same  $I_{OLED}$ . In the viewpoint of  $V_{TH}$ , the proposed pixel circuit provides an effective reduction of the V<sub>TH</sub> variation due to the process variation. If the scaling factor  $\alpha$  is 1/3, for example, the inherent  $V_{TH}$  variation of  $\pm 15\%$  from its average would be reduced to  $\pm 5\%$  by a circuit effect.

## 3. Simulation and Fabrication

In order to verify the proposed pixel circuit, the SPICE simulation and the fabrication were carried out. The SPICE model is RPI poly-Si TFT model (level = 36) and the simulation parameters for TFT and OLED are

extracted from the measurements. The low-temperature (450 °C) p-type poly-Si TFTs are fabricated by the typical TFT process such as PECVD a-Si film deposition, ELA with line beam laser irradiation, and ion implantation for doping [6]. The size of poly-Si TFT is  $W/L = 10 \ \mu m/10 \ \mu m$ , and the measured  $V_{TH}$  is -2.11V and  $\mu_{eff}$  is 80 cm<sup>2</sup>/V·s. The OLED is modeled as a diodeconnected TFT by fabrication and the threshold voltage of OLED is about 2 V.

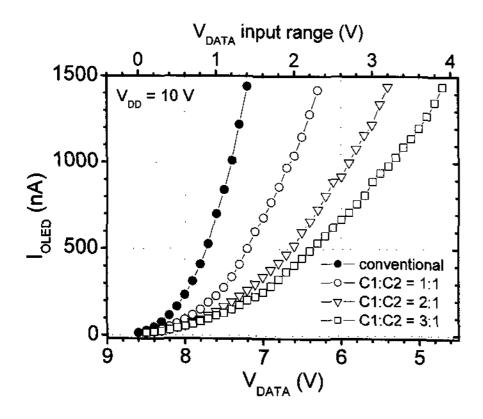

Fig. 2 shows the  $I_{OLED}$  measurement results according to the DATA inputs. In the conventional 2-TFT circuit, the DATA input required for  $I_{OLED} = 0 \sim 1000 nA$  is from 8.6 V to 7.4 V, thus the data input range is 1.2 V. In the proposed circuits, in which the ratio of C1:C2 is 1:1, 2:1, 3:1, the DATA input required for  $I_{OLED} = 0 \sim 1000 nA$  is increased up to 2.0 V, 2.7 V, 3.3 V, respectively. Since  $I_{OLED}$  varies sensitively according to  $(V_{DATA} - V_{DD} - V_{TH})$ , the increased input range of  $V_{DATA}$  contributes to suppressing the affect of  $V_{TH}$  variations.

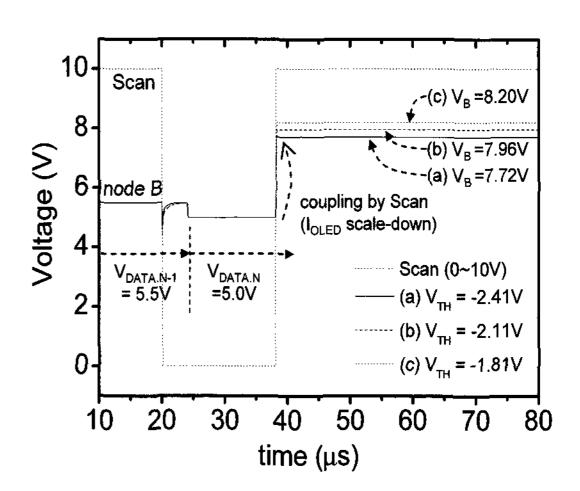

Fig. 3 shows the transient curves of voltage node B in the proposed pixel circuit. Node B changes with respect to 15 %  $V_{TH}$  variation ( $\pm$  0.3 V), while that of conventional 2-TFT pixel does not change. From the equation of  $\Delta V_B$ , the change of  $\Delta V_B$  due to  $\Delta V_{TH}$  is {C1/(C1+C2)}· $\Delta V_{TH}$ . If C1:C2 = 5:1 and  $\Delta V_{TH}$  =  $\pm$  0.3 V,  $\Delta V_B$  would be changed by  $\pm$  0.25 V. It is well consistent that the simulation results of the curve (a) and (c) exhibit  $\pm$  0.24 V from 7.96 V of the curves (b). This shows that the proposed pixel reduces and compensates the  $V_{TH}$  non-uniformity of poly-Si TFTs.

**Fig. 2.** Measurement results of the pixel current ( $I_{OLED}$ ) according to the input data voltages in the conventional 2-TFT pixel and the proposed pixel with various scaling conditions (C1:C2 = 1:1, 2:1, 3:1).

Fig. 3. Simulation results of the voltage node B of the storage capacitor when the same data voltage is addressed to the proposed pixel of C1:C2=5:1 which has a different threshold voltage (a) -2.41 V, (b) -2.11 V, and (c) -1.81 V.

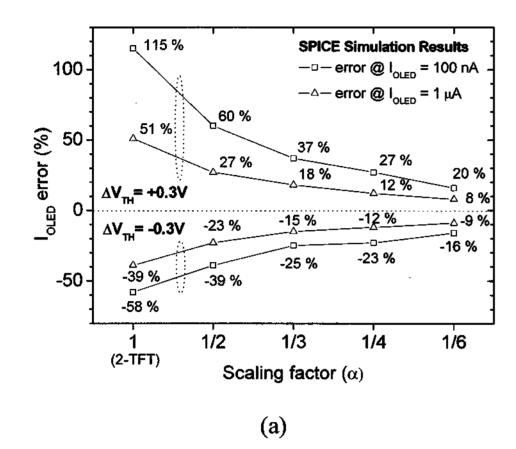

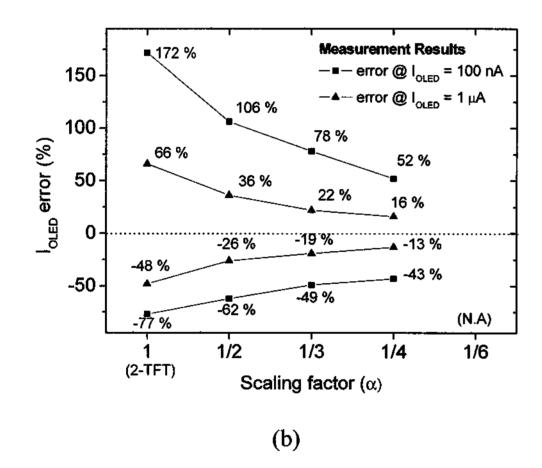

Fig. 4 shows the  $I_{OLED}$  error comparison when the  $V_{TH}$  of T2 and T3 is varied by  $\pm$  0.3 V ( $\pm$  15 %) from -2.1 V. The  $I_{OLED}$  errors were investigated at two reference current levels of  $I_{OLED}$  = 100 nA and 1  $\mu$ A around. The SPICE simulation results (Fig. 4a) show that, in the conventional pixel of which we can say the scaling factor ( $\alpha$ ) is 1, the OLED current variation due to +0.3 V variation of  $V_{TH}$  is 115 % at the 100 nA level and 51 % at the 1  $\mu$ A level, respectively.

In the proposed pixels, the capacitance ratio of C1:C2 is varied from 1:1 to 5:1, thus the scaling factor from 1/2 to 1/6 is determined. The OLED current compensation is improved as the scaling effect is enhanced. When  $\alpha$  is 1/6, the non-uniformity of  $I_{OLED}$  is considerably reduced to 20% from 115% at the 100 nA and no more than 8% from 51% at the 1 $\mu$ A, respectively, compared with the 2-TFT pixel. More over, since the  $V_{GS}$  (=  $V_{DATA} - V_{DD}$ ) for  $I_{OLED}$  = 100 nA is relatively smaller than that for 1 $\mu$ A,  $V_{TH}$  variation portion in  $(V_{DATA} - V_{DD} - V_{TH})$  is relatively large and the error would be increased in the small current level.

The measurement results also present a similar trend with the simulation results as shown in Fig. 4b. To investigate the  $I_{OLED}$  error due to  $\pm$  0.3 V of  $V_{TH}$  variation in real device, we used the equivalent measurement condition that the  $V_{DATA}$ , rather than  $V_{TH}$ , is varied with  $\pm$  0.3 V in the identical circuit sample, as is reasonable from the equation (2). When  $\alpha$  is 1/4, the

non-uniformity of  $I_{OLED}$  is considerably reduced to 52 % from 172 % at the 100 nA and 16 % from 66 % at the 1  $\mu$ A, res-pectively, compared with the 2-TFT pixel. Based on the simulation and the measurement results, the error would be reduced to below 5 % when the scaling factor is optimized.

Fig. 4. (a) Simulation and (b) measurement results of the  $I_{OLED}$  error comparison in the conventional 2-TFT pixel and the proposed pixel with various scaling factor ( $\alpha$ ) when the  $V_{TH}$  of T2 and T3 is varied by  $\pm$  0.3 V ( $\pm$  15 %) from -2.1 V.

## 4. Conclusions

We have proposed a novel compensation scheme employing the voltage-scaled programming pixel which reduces the  $V_{TH}$  variation of poly-Si TFT rather than the  $V_{TH}$  memorizing and cancellation. By the proposed circuit effect, the  $V_{TH}$  could be scaled down and the non-uniform OLED current was successfully reduced and compensated for. The data input range was also increased by the scaling

factor and the current variation sensitivity to  $V_{TH}$  variation could be lowered. The scaling factor was easily controlled by the capacitance ratio of C1 to C2. The proposed scheme also contributes to the suppression of the  $V_{DD}$  drop problem by employing the reported supply line elimination design. The proposed driving theory is promising for achieving uniform image in the voltage programming method.

### 6. References

- [1] M. Stewart, R.S. Howell, L. Pires, and M.K. Hatalis, *IEEE Trans. on Electron Devices*, **48**, 845 (2001).

- [2] S. J. Bae, H.S. Lee, J.Y. Lee, J.Y. Park, and C.W. Han, in *International Display Research Conference (IDRC) Dig.* (2000), p. 358.

- [3] S.H. Jung, W.J. Nam, and M.K. Han, *IEEE EDL*, **25**, 690 (2004).

- [4] S. M. Choi, and O.K. Kwon, in *Society for Information Displays (SID) Tech. Dig.* (2004), p. 260.

- [5] J.H. Lee, W.J. Nam, S.H. Jung, and M.K. Han, *IEEE EDL*, **25**, 280 (2004).

- [6] Y. M. Ha, in Society for Information Displays (SID) Tech. Dig. (2000), p.1116.