# Review of alternative gate stack technology research during the last decade

⊒ \_ Byoung Hun Lee¹, Paul Kirsch¹, Husam Alshareef², Prashant Majhi³, Rino Choi, Seungchul Song, Hsing Huang Tseng⁴ and Raj Jammy¹ ||

SEMATECH, 2706 Montopolis Drive, Austin, Texas, USA, <sup>1</sup>IBM,

<sup>2</sup>Texas Instruments, <sup>3</sup>Intel, <sup>4</sup>Freescale assignee byoung.hun.lee@sematech.org

#### **Abstract**

Scaling of the gate stack has been one of the major contributors to the performance enhancement of CMOS-FET devices in past technology generations. The scalability of gate stack has diminished in recent years and alternative gate stack technology such as metal electrode and high-k dielectrics has been intensively studied during the last decade. Today the performance of high-k dielectrics almost matches that of conventional SiO<sub>2</sub>-based gate dielectrics. However, many technical challenges remain to be resolved before alternative gate stacks can be introduced into mainstream technology. This paper reviews the research in alternative gate stack technologies to provide insights for future research.

#### 1. Introduction to device scaling trend

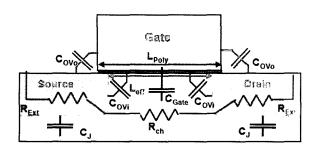

The performance of a CMOS device is determined by many factors, as shown in Fig.1. For example, a IR drop in the source-drain bias ( $V_{SD}' = V_{SD}$ - $I_d*R_{ext}$ ) reduces the effective source-to-drain bias applied to the channel region. Thus, when external resistance components are increased by high silicide resistance or low extension doping, device

performance degrades proportionally. To simplify the discussion, if the external impedance factors shown in Fig.1 are ignored, the drive current of MOSFETs can be expressed by equation (1),

$$I_{D,Sat} \sim \frac{\mu_n C_{OX}}{2} * \frac{W}{L_{Eff}} * f(V_{GS}, V_{DS}),$$

(1)

$V_{GS}$  and  $V_{DS}$  are the biases applied to substrate and source. Since the MOSFET has capacitance components, its speed can be expressed by the time constant  $\tau$ , indicating how fast the capacitor components of the MOSFET can be charged or discharged through  $I_{d,sat}$ .  $\tau$  can be expressed by equation (2).

$$\tau = \frac{CV}{I} = \frac{C_{OX} * f(V_{GS}, V_{DS})}{2 * I_{DSu}} \sim \frac{L_{Eff}}{\mu_n}$$

(2)

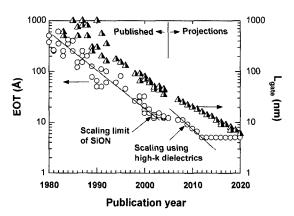

In this equation,  $C_{ox}$  in the numerator is canceled out by  $C_{ox}$  in the  $I_{d,sat}$  and the effective channel length  $L_{eff}$  and channel carrier mobility  $\mu_n$  dominate the speed of signal propagation through the MOSFET. Note that parasitic capacitance components are not included in this calculation. However, qualitatively, it is clear that physical scaling is the only way to improve device operation speed. Thus, over the last four decades, the performance of the modern CMOS device has been improved primarily by  $L_{eff}$  scaling, as shown in Fig.2.<sup>1</sup>

Fig. 1. A Schematic of MOSFET showing various device parameters.

**Fig. 2.** Scaling trend of gate oxide thickness and L<sub>gate</sub> over the past five technology generations from the 0.18 μm to 65 nm node. Experimental data or L<sub>gate</sub> and equivalent oxide thickness (EOT) are collected from device papers presented at major technical conferences and projected value f is based on the 2005 ITRS. When only inversion oxide thickness ( $T_{inv}$ ) is provided in the literature, 8 Å is subtracted from  $T_{inv}$  to account for the additional capacitance components due to poly depletion at the gate side and the quantum mechanical effect at the channel side.

The physical scaling of MOSFETs using shorter wavelength lithography and advanced patterning technologies accompanies many other challenges. As the L<sub>eff</sub> scales, the cross talk between the source-side junction and the drain-side junction causes various short channel effects. To avoid detrimental short channel effects, all other dimensions of the device such as junction depth and gate oxide thickness need to be scaled together with L<sub>eff</sub>. The physical scaling of source/drain depth requires a low energy-high current implantation, low resistance silicide, and low heat cycle rapid thermal activation. In partic-

ular, gate stack scaling has been one of the key technologies enhancing the performance of semiconductor devices. Gate oxide thickness has been scaled approximately 0.75 times per each technology generation, assuming a 3-year cycle per technology node, as shown in Fig. 2. However, the thickness of the gate oxide has scaled more slowly than the historical pace at an equivalent oxide thickness (EOT) of ~1 nm for the past two to three generations, because of issues such as process controllability, high leakage current, and reliability limitation. Although it was not clear at the time, the physical scaling of SiO<sub>2</sub> gate dielectric was effectively ended around 2002. However, the industry has not yet been able to implement an alternative gate stack and thus a major driver of performance enhancement has been lost, signaling an end to the scaling era and the advent of a new era of material and device evolution.

Since 2002, CMOS devices were continuously improved by controlling the transport properties of channel electrons using strain applied to silicon channels<sup>2-5</sup> and more elaborate control of short channel devices while the control of short channel effects became more difficult due to limited gate oxide scaling. The trade-off between short channel effects and device performance was offset by more precise device design and mobility improvement, another factor shown in equation (2). For more precise device control to optimize short channel devices and parasitic resistance, multiple spacers and precise control of extension doping using an advanced activation anneal such as laser and flash anneal were employed. However, the performance loss due to the trade-off cannot be fully compensated for in the coming technology generations without proper gate oxide scaling. That is why the International Technology Roadmap for Semiconductors (ITRS) requires that gate oxide scaling be resumed around 2008 using alternative gate stacks, as shown in Fig. 2.

### 2. Chronicles of alternative gate stack research

The demise of SiO<sub>2</sub> scaling has been predicted since the 1980s because of the increasing gate leakage current due to direct tunneling current. To reduce the tunneling current, the physical thickness of the gate dielectric had to be increased beyond the tunneling limit. Thus, as early as the 1970s, dielectric materials with dielectric constants higher than SiO<sub>2</sub> were proposed as a possible solution.

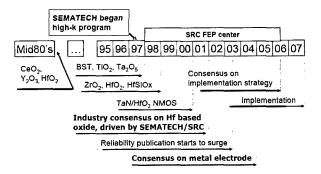

As shown in Fig. 3, in the 1980s, CeO<sub>2</sub> and Y<sub>2</sub>O<sub>3</sub> were actively studied to replace gate oxides with an EOT ~6 nm.<sup>69</sup> Since most of the high-k dielectrics demonstrated severe crystallization-induced leakage current and worse reliability in thick EOT regions, research on high-k dielectrics was phased out as nitrided SiO<sub>2</sub> was successfully implemented in CMOS technology.

In the mid-90s, interest in high-k dielectrics was renewed as the thickness of SiO<sub>2</sub> approached 2 nm, which is the electron tunneling limit of SiO<sub>2</sub>. Early work on alternative gate dielectrics focused on TiO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, and BaSrTiO<sub>3</sub>, which were inherited from DRAM capacitor dielectric research at that time. However, these materials showed relatively high leakage current due to their small band gap. Around 1998, research on high-k dielectrics quickly converged on the Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and ZrO<sub>2</sub> family, which has band gaps larger than 5.0 eV. HfO<sub>2</sub> and ZrO<sub>2</sub> received

Fig. 3. Summary of key research progress in alternative gate stack research.

the most attention in the late 1990s due to their better thermal stability with silicon.<sup>22-24</sup> It is interesting that HfO<sub>2</sub> and ZrO<sub>2</sub> were studied as early as the 1970s.<sup>25-27</sup> Various high-k dielectrics studied in this period are listed in Table 1, and a more detailed list of material characteristics is shown in Table 2. A more thorough review of the research during this time can be found in the paper by Wilk et al.<sup>27</sup>

The first metal gate/high-k dielectric MOSFET with an EOT ~1 nm was reported at the 2000 IEDM with a TaN/HfO<sub>2</sub> stack, as indicated in Fig. 3. However, at that time, introducing two different materials at the same technology node was unprecedented and considered too aggressive an approach. In 2002, a HfO<sub>2</sub>-based dielectric became widely accepted by a leading candidate, primarily driven by SEMATECH and SRC research groups, because ZrO<sub>2</sub> was found to be less stable with a polysilicon gate and can form Zr-silicide during the heat cycle when ZrO2 is dissociated by the hydrogen incorporated during polysilicon deposition. The difference in the thermal stability of HfO2 and ZrO2 can be deduced from the self-diffusion coefficient in Si shown in Table 2. ZrO2 shows a self-diffusion coefficient several orders of magnitude higher than that of HfO<sub>2</sub>, indicating a potential reaction with silicon atoms in the polysilicon gate.

Because of thermal stability issues when in contact with a polysilicon gate,<sup>30</sup> high-k dielectrics were often studied with metals such as Pt or Al at low temperature. Thus, it took some time to discover that the effective workfunction (EWF) of a polysilicon gate could not be easily altered by doping when it was used with high-k dielectrics, primarily because the EWF of a polysilicon gate/high-k dielectric stack is determined by Si-metal atom bonding instead of the Fermi level of the polysilicon gate.<sup>31</sup> This problem is often called 'Fermi-level pinning," referring to the phenomenon of the EWF of polysilicon being fixed at a certain point near the silicon conduction band edge. As a result, PMOS devices with a

Table 1. List of high-k gate dielectric materials with dielectric constant<sup>29</sup>

| Material                                       | ε        | Material                                         | ε       | Material                                         | ε       |

|------------------------------------------------|----------|--------------------------------------------------|---------|--------------------------------------------------|---------|

| Al <sub>2</sub> O <sub>3</sub>                 | 8-11.5   | LaScO <sub>3</sub>                               | 30      | Ta <sub>2</sub> O <sub>5</sub> -TiO <sub>2</sub> |         |

| Al <sub>x</sub> Si <sub>y</sub> O <sub>z</sub> |          | La <sub>2</sub> O <sub>3</sub> -SiO <sub>2</sub> | 5-16    | TiO <sub>2</sub>                                 | 86-95   |

| (Ba,Sr)TiO <sub>3</sub>                        | 200-300  | MgAl <sub>2</sub> O <sub>4</sub>                 | 8.3-9.4 | TiO <sub>2</sub> -SiO <sub>2</sub>               |         |

| BeAl <sub>2</sub> O <sub>4</sub>               | 8.3-9.43 | Pr <sub>2</sub> O <sub>3</sub>                   | 14.9    | TiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> |         |

| CeO <sub>2</sub>                               | 16.6-26  | PrAlO <sub>3</sub>                               | 25      | Y <sub>2</sub> O <sub>3</sub>                    | 8-11.6  |

| CeHfO <sub>4</sub>                             | 10-20    | NdAlO <sub>3</sub>                               | 22.5    | $Y_xSi_yO_z$                                     |         |

| CoTiO <sub>3</sub>                             |          | Sc <sub>2</sub> O <sub>3</sub>                   | 13      | ZrO <sub>2</sub>                                 | 22.2-28 |

| EuAlO <sub>3</sub>                             | 22.5     | Si <sub>3</sub> N <sub>4</sub>                   | 7       | Zr-Al-O                                          | 12-18   |

| HfO <sub>2</sub>                               | 26-30    | SmAlO <sub>3</sub>                               | 19      | Zr silicate                                      | 11-12.6 |

| Hf silicate                                    | 11       | SrTiO <sub>3</sub>                               | 150-250 | (Zr,Hf)SnTiO <sub>4</sub>                        | 40-60   |

| La <sub>2</sub> O <sub>3</sub>                 | 18-20.8  | Ta <sub>2</sub> O <sub>5</sub>                   | 25-45   | Ta <sub>2</sub> O <sub>5</sub> -TiO <sub>2</sub> |         |

| LaAlO <sub>3</sub>                             | 23.8-27  | TaON                                             |         | Y <sub>2</sub> O <sub>3</sub>                    | 8-11.6  |

polysilicon gate/high-k dielectric stack show very high threshold voltage ( $V_{th}$ ) values, beyond the practical range. This problem can be alleviated by using high-k materials with a pinning point close to the silicon valence band edge, favorable to PMOS. Very thin  $Al_2O_3$  or AlN capping has been proposed for this kind of application, but the usable range of EWF is limited even with these capping materials<sup>32-34</sup> and an impact on overall EOT and mobility degradation was pointed out as a limitation.

Around 2003, the limited Vth controllability was rec-

ognized as a serious challenge in the implementation of high-k dielectric because the EWF of NMOS and PMOS should be close to the conduction band (Ec~4.05eV) and valance band (Ev~5.15eV) of Si to obtain the best performing CMOS devices and the margin for effective workfunction should be less than 100mV<sup>35</sup>. The reduced adjustable effective workfunction range of polysilicon gate/high-k dielectric stack limits its application to low power applications where the requirement for threshold voltage is not as strict as in high performance devices.

Thus, around 2004, the industry reached a rough consensus that metal electrodes should be used with high-k dielectrics. It is ironic to see that the very reason for choosing Hf-based oxide was due to its compatibility with polysilicon gate, but polysilicon gate was discarded due to its incompatibility with Hf based high-k dielectrics. The search for the right metal electrode for nMOS and pMOS applications has not been as easy as it was thought to be in 2003, and it remains an ongoing challenge.

Table 2. Material properties of selected high-k materials.<sup>29</sup> Thermal expansion coefficient of silicon = 2.6x10<sup>-6</sup> K<sup>-1</sup>. Lattice constant of silicon = 5.43 Å.

|                                                | HfO <sub>2</sub>     | $ZrO_2$            | $CeO_2$ | $Y_2O_3$  | Al <sub>2</sub> O <sub>3</sub> | SiO <sub>2</sub> |

|------------------------------------------------|----------------------|--------------------|---------|-----------|--------------------------------|------------------|

| Bandgap (eV)                                   | 5.68                 | 5.16               | 5.5     | 5.5       | 8.3                            | 9                |

| Barrier height to Si (eV)                      | 1.6                  | 15                 |         |           | 2.08                           | 3.2              |

| Dielectric constant                            | ~30                  | ~25                | 26      | 14-17     | 8-10                           | 3.9              |

| Dielectric strength (MV/cm)                    | 2-4.5                |                    |         | 3-4.5     | >1.0                           | 5-10             |

| DC resistivity                                 | 4.5x10 <sup>-3</sup> | 106                | *       |           | 4014                           | 4014 4016        |

| (Ω/cm)                                         | @1100°C              | @385°C             |         |           | 1014                           | 1014-1016        |

| Dit                                            | ~1011                | ~1011              |         | ~1011     | ~1011                          | <5x10¹⁰          |

| Heat of formation (Kcal/mol)                   | 271                  | 261.9              |         | 454.3     | 399                            | - 1001           |

| ΔG for silicidation                            |                      | 5014               | 7.000   |           |                                | 100.0            |

| $(Si+MO_x \rightarrow MSi_x+SiO_2)$            |                      | 5.914              | 7.098   |           | n.a.                           | n.a.             |

| ΔG for reduction                               | 47.640               | 42.326             | 3629    | 116.8     | 64.39                          | n.a.             |

| $(Si+MO_x \rightarrow M+SiO_2)$                | 47.648               |                    |         |           |                                |                  |

| Refractive index                               | 2.2                  | 2.05               | 2.28    | 1.85-1.93 | 1.68-1.77                      | 1.468            |

| Density(g/cm³)                                 | 9.68                 | 5.9-6.1            | 6.86    | 5.03      | 3.94-3.98                      | 2.27             |

| Thermal conductivity (W/cm°C)                  |                      | 3.06               |         |           | 0.2                            | 0.014            |

| Melting point(°C)                              | 2900                 | 2677               | 2600    | 2420      | 2072                           |                  |

| Thermal expansion                              |                      | 501                |         | 0.0       |                                |                  |

| Coefficient(10 <sup>-6</sup> K <sup>-1</sup> ) | 5.3                  | 7.01               | İ       | 8.3       | 6.7                            | 0.5              |

| Lattice constant                               | 5.11                 | 5.10               | 5.411   | 10.60     | 4.7-52                         |                  |

| Self diffusion coefficient                     | 2.8227               | 6.0009             |         |           | 1.5048                         |                  |

| @900(°C)                                       | x10 <sup>-17</sup>   | x10 <sup>-10</sup> |         |           | x10 <sup>-7</sup>              |                  |

| Transition temperature(°C)                     | 1700                 | 1265               |         |           |                                |                  |

## 3. Recent advances in metal electrode/ high-k dielectric development

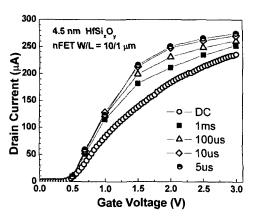

As mentioned above, around 2002, Hf-based oxides, including HfO2 and HfSiOx, emerged as promising candidates because of their excellent thermal stability with silicon. However, the mobility and reliability of these materials were not satisfactory for device applications. Mobility degradation of high-k dielectrics was thought to be an intrinsic characteristic due to optical phonon scattering and remote charge scattering. In 2003, A. Kerber et al. proposed that transient charging might have skewed the mobility measurement<sup>36,37</sup> and in 2004, B.H. Lee and C. Young et al. showed that there is very fast transient charging due to the carrier exchange between the channel carrier and trapping sites in high-k dielectric. 38,39 Fast transient charge trapping increases the threshold voltage of high-k devices in  $\mu$ seconds, reducing their drive current accordingly. Since conventional current-voltage (I-V) meters integrate signals on the order of milliseconds and the time scale of capacitance voltage (CV) measurements and I-V measurements does not exactly match, mobility calculations using I<sub>d</sub>-I<sub>g</sub> curves and CV curves tend to underestimate the mobility value, as shown in Fig. 4.38 In Fig. 4, the integration time to measure the drain current was set by the pulse width to measure the drain current and the drain current averaged during the pulse width was gradually recovered as the integration time was reduced. If mobility is recalculated using the I<sub>d</sub>-V<sub>g</sub> curve measured with a pulse measurement method, the intrinsic mobility degradation is much less than the value usually reported in the literature. Using the understanding from the pulse measurement, the intrinsic mobility of high-k devices was studied in detail and it was understood that reducing transient charging was the key to improving high-k device mobility. The key breakthroughs that enabled an enhancement in mobility were 1) understanding of transient charging

**Fig. 4.**  $I_d$ - $V_g$  curve measured with single pulse measurement. Each points of  $I_d$ - $V_g$  curves are the drain current values measured and averaged during the pulse width in a range of 5 µsec to 1 msec.

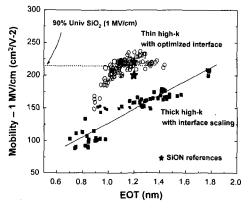

**Fig. 5.** Scatter chart of high field mobility (1 MV/cm) vs. EOT of various high-k devices fabricated at SEMATECH. Filled square data are obtained from devices with high-k dielectrics thicker than 30 Å while open circle data are obtained from devices with high-k dielectrics thinner than 25 Å. Reference line represents the 90% of SiO<sub>2</sub> universal mobility at 1MV/cm, which is close to the high field mobility of heavily nitrided oxides used in 90 nm technology. Three reference data points are also indicated by the star symbol.

behaviors in high-k devices <sup>3640</sup> and 2) scaling of the high-k thickness below the tunneling limit to eliminate residual tunneling carriers in the high-k layer. <sup>41-43</sup> In 2005, drastically improved mobility values, almost matching that of nitride oxide at an EOT of ~1 nm, were reported. <sup>44,45</sup>

By keeping the thickness of the high-k layer below 2 nm, the mobility degradation due to transient charging

effects can be eliminated. The high field mobility value vs. EOT curve shown in Fig. 5 clearly demonstrates this observation. However, thinning the high-k layer is only a temporary measure that works for a limited range of EOTs and leakage currents. Low standby power (LSTP) applications require a very low leakage current, and, to meet LSTP targets, the thickness of the high-k dielectric must be increased without degrading mobility. Careful optimization of the bottom oxide and Hf-silicate composition is also necessary. For high-performance applications, more aggressive EOT scaling is needed, but the physical scaling of the HfSiON layer can be limited to an EOT of ~0.8 nm to keep mobility above 85% of the universal curve.44 Thus, to scale the EOT of the total stack, the interfacial oxide layer should be further optimized. Scaling the interfacial layer, however, imposes serious limitations on the process window in terms of the applicable high-k layer and heat cycle. Additionally, mobility decreases rapidly as the thickness of the interfacial layer is scaled. When an interfacial oxide is thinner than 0.9 nm, the impacts of optical phonon scattering<sup>46</sup> or remote charge scattering <sup>47</sup> on channel carrier mobility rapidly increase. To avoid the trade-off between EOT scaling and mobility, it is important to 1) eliminate the charge scattering source within the high-k layer using elaborate passivation processes<sup>48-50</sup> and 2) increase the dielectric constant of the interfacial oxide with a minimal impact on interface state density.51 While HfSiON can be used for the 45 nm and 32 nm generations, any further extension of high-k dielectrics will require materials with a dielectric constant higher than HfO<sub>2</sub>. Lanthanide oxides have been proposed as higher-k materials, but many of them exhibit worse dielectric characteristics than Hf oxides. 52-54 An alternative path to future scaling is to use channel materials other than silicon. For example, the formation of interfacial oxide can be suppressed when a high-k dielectric is deposited on Ge or GaAs substrates.<sup>55-57</sup> While the quality of the interface may

be compromised with these channel materials, the scalability of the high-k dielectric stack will be enhanced. The challenges of this approach are to overcome the problems associated with the degraded interface and to make use of the benefits of high carrier mobility in Ge or other channel materials. If Hf-based oxide can be successfully implemented with these channel materials, Hf-based oxide might still be usable beyond the 32 nm node.

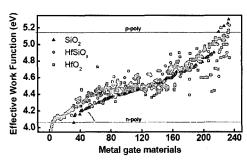

As mentioned above, the application of poly/high-k stacks is limited by V<sub>th</sub> controllability, poor reliability, dopant penetration, and inversion oxide thickness (T<sub>inv</sub>) scalability. Thus, n-type and p-type polysilicon gates must be replaced by metal electrode materials with proper EWFs close to Ec and Ev of the silicon substrate. Although the concept of the metal electrode is not new because the first semiconductor devices used Al electrode in the 1960s, there is a huge gap in understanding of the role of metal electrodes. The main technical challenge in this research is that the vacuum workfunction values of metals are not directly correlated to the V<sub>th</sub> of devices because of 1) dipole formation due to the charge transfer between metal atoms and dielectric atoms, 58 2) interface mixing during CMOS processing, 59 3) oxygen redistribution across the metal/highk interface, 60 4) formation of interface defects and charge redistribution around the defects, 5) the effect of impurities, 61 and 6) localized compositional variations in electrode materials. 62 Thus, overall electrode processes such as the deposition method, heat cycle, and dielectric composition need to be optimized together to develop a well defined metal electrode process. These problems have been recognized only recently; many of the issues listed above are not well understood for most materials.

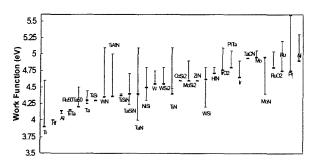

Since 2000, many publications have addressed metal electrodes, but there was little consensus on which electrode should be used with high-k dielectrics. For the same material, many different workfunction values have been reported, as shown in Fig. 6. One of the obvious rea-

Fig. 6. Workfunction values reported in the literatures vary widely for the same material system depending on deposition method and differences in subsequent processes.<sup>63</sup>

sons for such variation is the diverse factors affecting the EWF, but a less obvious reason is that the way the workfunction values were extracted was not accurate. In many publications, workfunction values were extracted using 3-5 points scattered around a linear curve, especially using thick oxide. However, an EWF that determines the threshold voltage of a device should be extracted at the thickness range where the device operates, i.e., at an EOT ~1 nm. Otherwise, the workfunction values extracted in the wrong thickness range or at limited data points do not have a practical meaning.

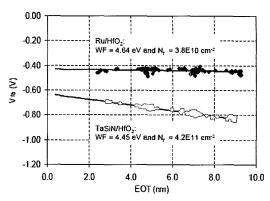

In 2005, SEMATECH proposed a "terraced oxide wafer technology," which uses a single wafer containing several bands of gate dielectric thicknesses with EOTs from 1.5 nm to 9 nm.64 Fig. 7 shows an example of EWF extraction using a terraced oxide wafer in the EOT range of 2.5 nm to 9 nm. In this method, more than 49 data points were used to extrapolate the workfunction. Using sufficient data points and extending the V<sub>fb</sub> vs. EOT curve into a thin oxide region ensure the accuracy of this extraction. Today, more groups are using methodologies similar to the terraced oxide wafer. Note that in this paper, "EWF" is used instead of "workfunction" to define the physical properties of electrodes because in the conventional meaning of workfunction, the work needed to extract an electron from the metal surface does not have a direct correlation with the threshold voltage of metal gate devices. The threshold voltage of

Fig. 7. An example of a  $V_{\text{fb}}$ -EOT curve generated from a terraced oxide wafer.

a device with a metal gate/high-k dielectric gate stack is determined by the bonding configuration at the interface between the metal electrode and high-k dielectric instead of the vacuum workfunction of the metal electrode, and the bonding configuration is influenced by the many factors listed above. Thus, very careful investigation is necessary to define the EWF of a metal electrode system, which cannot be separated from the underlying dielectric or subsequent processes. In short, EWF is no longer a characteristic of metal electrodes, but a characteristic of the overall gate stack and should be defined as such.

Finding a metal electrode system that meets the specifications for a scaled device has been challenging. Not only the scattered data in the literature, but also the limited infrastructure to study metal gate devices have constrained overall progress and the fierce competition to arrive at a metal electrode solution has forced the leading research group to refrain from sharing its learning. Thus, only limited information about metal electrode systems is available in the open literature. In 2003, Intel announced that their metal electrode solution was ready without disclosing the material system. <sup>65</sup> In 2005, SEMATECH also showed an EWF chart including material systems with a band edge electrode solution, again without specifying the metal electrode, as shown in Fig. 8. <sup>66</sup>

In Fig. 8, several metal systems showed EWF values

Fig. 8. EWF values of various metal systems extracted after 1000°C, 5sec anneal. The X axis represents the material systems and three groups of data points showed EWFs obtained with two different gate dielectrics (SiO2, and HfSiOx). Data included in Fig. 8 were obtained using a terraced oxide wafer.61 To study the change in EWF at the metal/high-k interface, very thin HfSiON layers were deposited on a terraced oxide wafer.

near the conduction and valence band edge of silicon even after high temperature processing, satisfying the requirements for gate-first CMOS integration (EWF of electrodes should be close to E<sub>csi</sub> for nMOS and E<sub>vsi</sub> for pMOS after the CMOS heat cycle, which is typically a 1100°C spike anneal or 1000°C, 5sec rapid thermal anneal). Metal electrode systems are not specified in Fig. 8 because the EWF of a metal/high-k stack can be controlled by many factors described above and, in fact, electrode and high-k dielectrics are better considered as a single materials system that requires simultaneous optimization. A detailed method of controlling the EWF of metal electrode/high-k dielectrics will be discussed in the future publications.

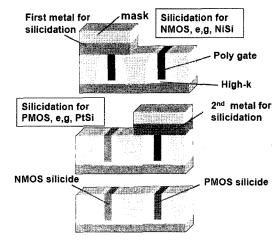

Due to difficulties associated with metal electrode research such as material definition and contamination control, several research groups have investigated the feasibility of silicide electrodes. Fully silicided (FUSI) gate has received considerable attention since 2001 because the polysilicon gate can be silicided with a relatively low heat cycle with minimal damage to the gate dielectric after device fabrication. Gate silicidation after source/drain silicidation eliminates the concern about metal contamination in the frontend process, and low heat cycle process appeared attractive. CoSi<sub>2</sub> was used in the initial demonstration of silicided gate, 67 but the focus quickly shifted to NiSi and NiSi<sub>3</sub> because the workfunction of Ni silicides could be modified with dopants in the polysilicon gate or a phase of Ni silicides. 68-71 However, the EWF range was still limited with silicide gate even though the FUSI process used only low temperature processes. Various silicides were studied to find a silicide gate with a band edge EWF. The most promising silicide gate materials are HfSi (~4.2 eV)<sup>72</sup> and ErSi (~4.2 eV) for NMOS and PtSi (~4.9 eV), Pt<sub>2</sub>Si(5.0eV) for PMOS.<sup>73</sup> Even though the EWF range is not wide enough for high performance applications, these silicide gates can still be used in low power applications or applications requiring quarter gap electrodes (~4.3 eV for NMOS, ~4.8 eV for PMOS) such as FinFETs or fully depleted silicon-on-insulator (FDSOI) devices.74 However, there are several potential challenges to the FUSI approach such as pattern dependent silicidation,75,76 strain control due to volume expansion, and process complexity for a dual silicide approach. Also, the need for two different silicide materials to achieve lower nMOS and pMOS threshold voltages actually complicates the overall integration process as shown in Fig. 9. The proposal to use metal layers with different thicknesses for dense and sparse patterns

Fig. 9. A potential integration scheme for dual workfunction fully silicided (FUSI) gate devices.

to solve the problem of pattern-dependent silicidation further increases the complexity of the FOSI process. While the reliability of FUSI devices has not been explored extensively, an initial study indicates that it might be degraded by the reliability degradation mechanisms that have affected polysilicon gate/high-k dielectric stack devices. Polysilicon gate devices show a much higher level of bias temperature instability than metal gate devices, potentially due to higher electron-hole pair generation at the polysilicon/high-k dielectric interface.<sup>77</sup>

One subject not addressed in this paper is the reliability of a metal electrode/high-k dielectric stack. Once the electrode materials are chosen for each application, the impact of reliability should be studied in detail. While there are many publications on the reliability of high-k devices, they are in some ways very preliminary works because the influence of metal electrodes has not been accounted rigorously. Metal electrodes can affect the reliability of gate dielectrics in many ways: 1) diffusion and intermixing with the dielectric, 2) oxygen and nitrogen redistribution, and 3) impurity contamination. None of these topics has been well investigated, primarily because the material systems are not finalized yet.

#### 6. Conclusion

In this article, the progress in alternative gate stack technology during the last decade has been reviewed and some current challenges described. Considering the rapid progress in recent years, an alternative gate stack with a metal gate/high-k dielectric will be implemented for silicon-based technology in the near future, but research on reliability will need significant acceleration.

#### **Acknowledgments**

The authors appreciate the technical support of team

members from the Front-End Process division at SEMAT-ECH.

#### References

- 1. B.H. Lee, J. Oh, H.H. Tseng, R. Jammy and H. Huff, "Gate Stack Technology for Nano Scale Devices: Current and Future Challenges," to be published in Materials Today (2006).

- A. Shimizu, K. Hachimine, N. Ohki, H. Ohta, M. Koguchi, Y. Nonaka, H. Sata, and F. Ootsuka, "Local mechanical-stress control (LMC): a new technique for CMOS-performance enhancement," Tech. Dig. of IEDM (2001), p.433.

- S. Pidin, T. Mori, K. Inoue, S. Fukata, N. Itoh, E. Mutoh, K. Ohkoshi, R. Nakamura, K. Kobayashi, K. Kawamura, T. Saiki, S. Fukuyama, S.Satoh, M. Kase, and K. Hashimoto, "A novel strain enhanced CMOS architecture using selectively deposited high tensile and high compressive silicon nitride films," Tech. Dig. of IEDM (2004), p. 213.

- 4. S. E. Thompson, M. Armstrong, C. Auth, S. Cea, R. Chau, G. Glass, T. Hoffman, J. Klaus, Z. Ma, B. Mcintyre, A. Murthy, B. Obradovic, L. Shifren, S. Sivakumar, S. Tyagi, T. Ghani, K. Mistry, M. Bohr, and Y. El-Mansy, "A logic nanotechnology featuring strained-silicon," IEEE Electron Dev. Lett. (2004), 25, p. 191.

- S.L. Wu, Y.M. Lin, S.J. Chang, S.C. Lu, P.S. Chen, and C.W.Liu, "Enhanced CMOS Performances Using Substrate Strained-SiGe and Mechanical Strained-Si Technology," IEEE Electron Dev. Lett., (2006), 27, p.46.

- L.Machanda and M.Gurvitch, "Yittrium oxide/silicon dioxide: A new dielectric structure for VLSI/ ULSI circuits," IEEE Electron Dev. Lett. (1988), 9, p.180.

- 7. H.Fukumoto, T.Imura, and Y.Osaka, "Heteroepitaxial growth of Y<sub>2</sub>O<sub>3</sub> films on silicon," Appl. Phys. Lett. (1989), 55, p.360.

- 8. T.Inoue, Y.Yamamoto, S.Koyama, S.Suzuki, and Y.Ueda, "Epitaxial growth of CeO<sub>2</sub> layer on silicon," Appl. Phys. Lett. (1990), 56, p.1332.

- S.Yaegashi, T.Kurihara, H.Hoshi, and H.Segawa, "Epitaxial growth of CeO<sub>2</sub> films on Si(111) by sputtering," Jpn. J. Appl. Phys. (1994), 33, p.270. S. Campbell, D.C.Gilmer, X.Wang, M.Hsieh, H.Kim, W.L.Gladfelter, and J.Yan, "MOSFET Transistor fabricated with high permittivity TiO<sub>2</sub> dielectrics," IEEE Trans. Electron Dev. (1997), 44, p.104.

- G. Efkekhari, "Electrical characteristics of Ta<sub>2</sub>O<sub>5</sub> films on Si prepared by dc magnetron reactive sputtering

and annealed rapidly in N<sub>2</sub>O," J. Vac. Sci. Technol. (1998), B16, p.2115.

- 11. H.F.Luan, B.Z.Wu, L.G.Kang, B.Y.Kim, R.Vrtis, D.Roberts, and D.L.Kwong, "Ultra thin high quality Ta<sub>2</sub>O<sub>5</sub> gate dielectric prepared by in situ rapid thermal processing," Tech. Dig. of IEDM (1998), p.609.

- B. Ho, T. Ma, S.A. Campbell, W.L. Gladfelter, "A

1.1 nm oxide equivalent gate insulator formed using TiO<sub>2</sub> on nitrided silicon," Tech. Dig. of IEDM (1998), p.1038.

- Q.Lu, D.Park; A. Kalnitsky, C.Chang, C. Cheng, S. P. Tay, T.-J. King, C. Hu, "Leakage current comparison between ultra-thin Ta<sub>2</sub>O<sub>5</sub> films and conventional gate dielectrics," IEEE Electron Dev. Lett. (1998), 19, p.341.

- 14. B. H. Lee, Y. Jeon, K. Zawadzki, W. Qi and J. C. Lee, "Effect of interfacial layer growth on the electrical characteristics of thin titanium oxide films on silicon," Appl. Phys. Lett. (1999), 74, p.3143.

- 15. W Lee, L.Machanda, F.Baumann, J.Bower, W.Brown, C.Case, R.Keller, Y.O.Kim, E.J.Laskowski, M.D.Morris, R.L.Opila, P.J.Silverman, T.W.Sorsch and G.R.Weber, "Gate quality doped high k films for CMOS beyond 100nm: 3-10nm Al<sub>2</sub>O<sub>3</sub> with low leakage and low interface states," Tech. Dig. of IEDM (1998), p.605.

- Z.D.Wilk, R.M. Wallace, "Stable zirconium silicate gate dielectrics deposited directly on silicon," Appl Phys. Lett. (2000) 76, p.112.

- 17. W. Qi, R. Nieh, B. H. Lee, L. Kang, Y. Jeon, K. Onishi, T. Nagai, S. Banerjee, and J. C. Lee, "MOSCAP and MOSFET characteristics using ZrO<sub>2</sub> gate dielectric deposited directly on Si," Tech. Dig. of IEDM (1999), p.145.

- 18. B. H. Lee, L. Kang, W. Qi, R. Nieh, K. Onishi, and J. C. Lee, "Ultrathin hafnium oxide with low leakage and excellent reliability for alternative gate dielectric applications," Tech. Dig. of IEDM, (1999), p.143.

- B.H. Lee, L. Kang, R. Nieh, W.-J. Qi, and J. C.Lee, "Thermal stability and electrical characteristics of Hafnium oxide gate dielectric reoxidized with rapid thermal annealing," Appl. Phys. Lett. (2000), 76, p.1926.

- D.A.Buchanan, E.P.Gusev, E.Cartier, H.Okorn-Schmidt, K.Rim, M.A.Gribelyuk, A. Mocuta, A.Ajmera, M. Copel, S. Guha, N. Bojarczuk, A. Callegari, C. D'Emic, P. Kozlowski, K. Chan, R.J. Fleming, P.C. JAmison, I. Brown, R.Arndt, "80 nm polysilicon gated n-FETs with ultra-thin Al2O3 gate dielectric for ULSI applications," Tech. Dig. of IEDM, (2000), p.223.

- 21. G.D.Wilk and R.M.Wallace, "Electrical properties

- of hafnium silicate gate dielectric deposited directly on silicon," Appl. Phys. Lett. (1999), 74, p.2854.

- 22. W. Qi, R. Nieh, E. Dhamarajan, B.H. Lee, Y. Jeon, L. Kang, K. Onishi, and J.C. Lee, "Ultrathin zirconium silicate film with good thermal stability for alternative gate dielectric application," Appl. Phys. Lett. (2000), 77, p.1704.

- 23. L. Kang, Y. Jeon, K. Onishi, B.H. Lee, W.-J. Qi, R. Nieh, S. Gopalan, and J.C. Lee, "Single-layer thin HfO<sub>2</sub> gate dielectric with n<sup>+</sup>-polysilicon gate," Proc. of the Symp. on VLSI technol. (2000), p.44.

- M.T. Thomas, "Preparation and properties of sputtered hafnium and anodic HfO<sub>2</sub> films," J. Electrochem. Soc. (1970), 117, p.396.

- 25. M.Balog, M.Schieber, M.Michiman, and S.Patai, "Chemical vapor deposition and characterization of ZrO<sub>2</sub> films from organometallic compounds," Thin Solid Films, (1977), 41, p.110.

- 26. M.Balog, M.Schieber, M.Michiman, and S.Patai, "Chemical vapor deposition and characterization of HfO<sub>2</sub> films from organo-hafnium compounds," Thin Solid Films, (1977), 41, p.247.

- G.D.Wilk, R.M.Wallace, J.M.Anthony, "High-k gate dielectrics: Current status and materials properties considerations," J. Appl. Phy. (2001), 89, p.5243.

- 28. B.H.Lee, Ph.D Dissertation, "Technology development and process integration of alternative gate dielectric material; Hafnium oxide," ISBM 0-493-13564-2 (2000).

- 29. T.J.Hubbard and D.G.Schlom, "Thermodynamic stability of binary oxides in contact with silicon," J. Mater. Res. 11, p.2757, 1996.

- 30. C.C. Hobbs, L.R. C. Fonseca, A. Knizhnik, V. Dhandapani,S. B. Samavedam, W.J. Taylor, J.M. Grant, L.G. Dip, D.H. Triyoso, R.I. Hegde, D.C. Gilmer, R.Garcia, D.Roan, M.L. Lovejoy, R.S. Rai, E.A. Hebert, H.-Huang. Tseng, S.G. H. Anderson, B.E. White, and P.J. Tobin, "Fermi-Level Pinning at the Polysilicon/Metal Oxide," IEEE Trans. on Electron Dev., VOL. 51 (2004), p. 971.

- 31. J. H. Lee, K. Koh, N. I. Lee, M. H. Cho, Y. K. Kim, J. S. Jeon, K. H.Cho, H. S. Shin, M. H. Kim, K. Fugihara, H. K. Kang, and J. T. Moon, "Effect of polysilicon gate on the flatband voltage shift and mobility degradation for ALD- Al O gate dielectric," Tech. Dig. of IEDM (2000), p. 645.

- 32. M.Frank, V.Paruchuri, V.Narayanan, N.Bojarczuk, B.Linder, S.Zafar, E.Cartier, E.Gusev, P.Jamison, K.L.Lee, M.Steen, M.Copel, S.Cohen, K.Maitra, X.Wang, P.Kozlowski, J.Newbury, D.Medeiros, P.Olidiges, S.Guha, R.Jammy, M.Ieong, G.Shahidi, "Poly-Si/High-k gate stacks with near ideal threshold

- voltage and mobility," Proc. of VLSI-TSA, (2006), p.97.

- 33. H.J. Li, M. Gardner, "Dual high-k gate dielectric with poly gate electrode: HfSiON on nMOS and Al<sub>2</sub>O<sub>3</sub> capping layer on pMOS," IEEE Electron Dev. Lett. (2005), 26, p.441.

- I. De, D. Johri, A. Srivastava, C.M. Osburn, "Impact of gate workfunction on device performance at the 50 nm technology node," Solid-State Electronics, (2002), 44, p.1077.

- 35. A. Kerber, E. Cartier, L. Pantisano, R. Degraeve, T. Kauerauf, Y. Kim, A. Hou, G. Groeseneken, H. E. Maes, and U. Schwalke, "Origin of the threshold voltage instability in SiO<sub>2</sub>/HfO<sub>2</sub> dual layer gate dielectrics," *IEEE Electron. Dev. Lett.*, Vol. 24, No. 2, pp.87-89, 2003.

- 36. A. Kerber, E. Cartier, L. A. Ragnarsson, M. Rosmeulen, L. Pantisano, R. Degraeve, Y. Kim, and G. Groeseneken, "Characterization of the Vt Instability in SiO<sub>2</sub>/HfO<sub>2</sub> Gate Dielectrics," Proc. of Int. Rel. Phys. Symp. (2003), p. 41.

- B.H. Lee, C. Young, R. Choi, J.H. Sim, G. Bersuker and G. Brown, "Transient charging in high-k gate dielectrics and its implications," Jpn. J. of Appl. Phys., Vol. 44, No. 4B, 2415, 2005.

- 38. C.D. Young, Y. Zhao, M. Pendley, B.H. Lee, K. Matthews, J.H. Sim, R. Choi, G.A. Brown, R.W. Murto and G. Bersuker, "Ultra-Short Pulse Current-Voltage Characterization of the Intrinsic Characteristics of High-κ Devices," Jpn. J. of Appl. Phys., Vol. 44, No. 4B, 2437, 2005.

- 39. W. Zhu, J.-P. Han, and T. P. Ma, "Mobility Measurement and Degradation Mechanisms of MOSFETs MadeWith Ultrathin High-k Dielectrics," IEEE Trans. on Elect. Dev. (2004), 51, p.98.

- 40. R. Choi, S. C. Song, C. D. Young, G. Bersuker, and B. H. Lee, "Investigation of charge trapping and detrapping characteristics in hafnium silicate dielectric using inversion pulse measurement technique," Appl. Phys. Lett. (2005), 87, p.122901.

- 41. J.H.Sim, S.C.Song, P.D.Kirsch, C.D.Young, R.Choi, D.L.Kwong, B.H.Lee and G.Bersuker, "Effect of ALD HfO<sub>2</sub> thickness on charge trapping and mobility," Microelectronic Eng., 80, p.218, 2005.

- 42. G. Bersuker, J. Sim, C. S. Park, C. Young, S. Nadkarni, R. Choi, and B. H. Lee, "Intrinsic threshold voltage instability of the HfO<sub>2</sub> NMOS Transistors," to be presented at Int. Reliability Physics Symp., 2006.

- 43. M. A. Quevedo-Lopez, S. A. Krishnan, P. D. Kirsch, H. J. Li, J. H. Sim, C. Huffman, J. Peterson, B.H. Lee, G. Pant, B. E. Gnade, M. J. Kim, R. M. Wallace, D. Guo, H. Bu, and T.P. Ma, "High Mobility HfSiON Gate Dielectric for High Performance Applications

- with Minimal Charge Trapping and Suppressed Crystallization," Tech. Dig. of IEDM (2005), p.437.

- 44. P. D. Kirsch, M. A. Quevedo-Lopez, H. -J. Li, Y. Senzaki, J. J. Peterson, S. C. Song, S. A. Krishnan, N. Moumen, J. Barnett, G. Bersuker, P. Y. Hung, B. H. Lee, T. Lafford, Q. Wang, D. Gay, and J. G. Ekerdt, "Nucleation and growth study of atomic layer deposited HfO<sub>2</sub> gate dielectrics resulting in improved scaling and electron mobility," J. Appl. Phys. (2006), 99, p.023508.

- 45. M.V. Fischetti, D.A. Neumayer, and E.A. Cartier, "Effective electron mobility in Si inversion layers in metal-oxide-semiconductor systems with a high-k insulator: The role of remote phonon scattering," J. Appl. Phys. (2001), 90, p.4587.

- 46. S. Saito, D. Hisamoto, S. Kimura, and M. Hiratani, "Unified mobility model for high-k gate stacks," Tech. Dig. of IEDM, (2003), p.797.

- C.S. Laia, W.C. Wu, J.C. Wang, T.S. Chao, "Characterization of CF4-plasma fluorinated HfO<sub>2</sub> gate dielectrics with TaN metal gate," Appl. Phys. Lett. (2005), 86, 222905.

- 48. H.-H. Tseng, P.J. Tobin, E. A. Hebert, S. Kalpat, M. E. Ramón, L. Fonseca, Z. X. Jiang, J. K. Schaeffer, R. I. Hegde, D. H. Triyoso, D. C. Gilmer, W. J. Taylor, C. C. Capasso, O. Adetutu, D. Sing, J. Conner, E. Luckowski, B. W. Chan, A. Haggag, S. Backer, R. Noble, M. Jahanbani, Y. H. Chiu, B. E. White, "Defect Passivation with Fluorine in a Ta<sub>x</sub>C<sub>y</sub>/High-K Gate Stack for Enhanced Device Threshold Voltage Stability and Performance," Tech. Dig. of IEDM (2005), p.713.

- 49. H.K. Park, M.S. Rahman, M. Chang, B.H. Lee, R. Choi, C.D. Young, and H. Hwang, "Improved Interface Quality and Charge-Trapping Characteristics of MOSFETs With High-k Gate Dielectric," IEEE Electron Dev. Lett., (2005), 26, p.725.

- 50. K. Kita, K. Kyuno, and A. Toriumi, "Permittivity increase of yttrium-doped HfO<sub>2</sub> through structural phase transformation," Appl. Phys. Lett. (2005), 86, p.102906.

- 51. H. J. Osten J.P. Liu, P. Gaworzewski, E.Bugiel, and P.Zaumseil, "High-k Gate Dielectrics with Ultra-low Leakage Current Based on Praseodymium Oxide," Tech. Dig. of IEDM (2000), p. 653.

- 52. S. Ohmi, C. Kobayashi, K. Aizawa, S. Yamamoto, E. Tokumitsu, H. Ishiwara, and H. Iwai, "High Quality ultrathin La<sub>2</sub>O<sub>3</sub> Films for High-k Gate Insulator," Proceeding of the 31st European Solid-State Device Research Conference (2001), p.235.

- 53. X. Lu, Z. Liu, Y.Wang, Y. Yang, X. Wang and H. Zhou, B. Nguyen, "Structure and dielectric properties of amorphous LaAlO<sub>3</sub> and LaAlO<sub>x</sub>N<sub>y</sub> films as alter-

- native gate dielectric materials," J. Appl. Phys. (2003), 94, p.1229.

- 54. W. P. Bai, N. Lu, J. Liu, A. Ramirez, D. L. Kwong, D. Wristers, A. Ritenour, L. Lee, and D. Antoniadis, "Ge MOS characteristics with CVD HfO<sub>2</sub> gate dielectrics and TaN gate electrode," Proc. of Symp. on VLSI Tech. (2003), p. 121.

- 55. J. Chen, N. Bojarczuk, H. Shang, M. Copel, J. Hannon, J. Karasinski, E. Preisler, S. Banerjee, and S. Guha, "Ultrathin Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> Gate Dielectrics on Surface-Nitrided Ge," IEEE Trans. on Electron Dev. (2004), 51,p.1441.

- M.M. Frank, G.D. Wilk, D. Starodub, T. Gustafsson, E. Garfunkel, Y.J. Chabal, J. Grazul and D.A. Muller, "HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics on GaAs grown by atomic layer deposition," Appl. Phys. Lett. (2005), 86, p.152904.

- 57. O. Sharia, A.A.Demkov, G.Bersuker and B.H.Lee, "Internal dielectric interface: SiO<sub>2</sub>/HfO<sub>2</sub>," in press, Bullentin of American Physical Soc. (2006).

- 58. K. Choi, H.N. Alshareef, H.C. Wen, R.Harris, H.Luan, Y. Senzaki, P. Lysaght, P. Majhi and B.H. Lee, "Workfunction Modulation of ALD TaN by capping Layer," submitted to Appl. Phys. Lett. (2006).

- 59. E. Cartier, F. R. McFeely, V. Narayanan, P. Jamison, B. P. Linder, M. Copel, V. K. Paruchuri, V.S. Basker, R. Haight, D. Lim, R. Carruthers, T. Shaw, M. Steen, J. Sleight, J. Rubino, H. Deligianni, S. Guha, R. Jammy, G. Shahidi, "Role of Oxygen Vacancies in V<sub>FB</sub>/V<sub>1</sub> stability of pFET metals on HfO<sub>2</sub>," Proc. of Symp. on VLSI Tech. (2005), p.230.

- 60. K. Choi, H. Alshareef, P. Lysaght, H.-C. Wen, R. Harris, H. Luan, P. Majhi, and B. H. Lee, "Workfunction tuning by thickness variation of metal film and dielectric surface treatment," Proc. of ESSDERC (2005), p.101.

- K. Choi, H.-C. Wen, P. Majhi, and B.H. Lee, "Effect of Underlying Dielectric Film on the ALD-TiN film Properties," 11th Workshop on oxide electronics (2004).

- 62. P. Majhi, H.C. Wen, H. Alshareef, K. Choi, R. Harris, P. Lysaght, H. Luan, Y. Senzaki, S. C. Song, B.H. Lee, and C. Ramiller, "Evaluation and Integration of Metal Gate Electrodes for Future Generation Dual Metal CMOS," Proc. of ICICDT, p.69, 2005.

- 63. G. A. Brown, G. Smith, J. Saulters, K. Matthews, H.-C. Wen, H. AlShareef, P. Majhi and B.H. Lee, "An Improved Methodology for Gate Electrode Workfunction Extraction in SiO<sub>2</sub> and High-k Gate Stack Systems Using Terraced Oxide Structures," Discussed at SISC (2004).

- 64. R.Chau, S.Datta, M.Doczy, B.Doyle, J. Kavalieros, M.Mets, "High-k/metal-gate stack and its MOSFET char-

- acteristics", IEEE Electron. Dev. Lett. (2004) 25, p.408. 65. B.H. Lee, S. C. Song, C.Young, P. Kirsch, R.Choi, P.Lysaght, P.Majhi, G.Bersuker and C.Ramiller, "Chal-

- P.Lysaght, P.Majhi, G.Bersuker and C.Ramiller, "Challenges in the High-k Dielectric Implementation for 45nm Technology Node," Proc. of ICICDT, p.73, 2005.

- 66. B. Tavel, T. Skotnicki, G. Pares, N. Carriere, M. Rivoire, F. Leverd, C.Julien, J. Torres, and R. Pantel, "Totally silicided (CoSi<sub>2</sub>) polysilicon: A novel approach to very low resistive gate without metal CMP or etching," Tech. Dig. of IEDM (2001), p. 825.

- 67. Z. Krivokapic, W. Maszara, K.Achutan, P. King, J. Gray, M.Sidorow, E.Zhao, J.Zhang, J.Chan, A.Marather, and M.R.Lin, "Nickel silicide metal gate FDSOI devices with improved gate oxide leakage," Tech. Dig. of IEDM (2002), p.271.

- 68. J. Kedzierski, D. Boyd, P. Ronsheim, S. Zafar, J. Newbury, J. Ott, C. Cabral Jr., M. Ieong, and W. Haensch, "Threshold voltage control in NiSi-gated MOSFETs through silicidation induced impurity segregation (SIIS)," Tech. Dig. of IEDM (2003), p. 315.

- 69. K. Takahashi, K. Manabe, T. Ikarashi, N. Ikarashi, T. Hase, T. Yoshihara, H. Watanabe, T. Tatsumi, and Y. Mochizuki, "Dual workfunction Ni-Silicide/HfSiON gate stacks by phase-controlled full-silicidation (PC-FUSI) technique for 45 nm-node LSTP and LOP devices," Tech. Dig. of IEDM (2004), p. 91.

- C.Y. Kang, P. Lysaght, R. Choi, B.H.Lee, S.J. Rhee, C.H. Choi, M.S. Akbar, and J.C. Lee, "Nickel-silicide phase effects on flatband voltage shift and equivalent oxide thickness decrease of hafnium silicon oxynitride metal-silicon-oxide capacitors," Appl. Phys. Lett. (2005), 86, p.222906.

- 71. C.S. Park, B.J. Cho, and D.-L. Kwong, "Thermally Stable Fully Silicided Hf-Silicide Metal-Gate," Electrode IEEE Elect. Dev. Lett. (2004), 25, p.372.

- 72. T. Nabatame, M. Kadoshima, K. Iwamoto, N. Mise, S. Migita, M. Ohno, H. Ota, N. Yasuda, A. Ogawa, K. Tominaga, H. Satake, A. Toriumi, "Partial silicides technology for tunable workfunction electrodes on high-k gate dielectrics Fermi level pinning controlled PtSix for HfOxN pMOSFET," Tech. Dig. of IEDM (2004), p.83.

- 73. J. Kedzierski, M. Ieong, T. Kanarsky, Y. Zhang, and H.-S. P. Wong, "Fabrication of Metal Gated FinFETs Through Complete Gate Silicidation with Ni," IEEE Trans. on Electron Dev, (2004), 51, p. 2115.

- J. Kedzierski, D.Boyd, Y.Zbang, M.Steen, F.F.Jamin, J.Benedict, M.Ieong, W.Haensch, "Issues I Nisi-gated FDOI device integration," Tech. Dig. of IEDM (2003), p.441.

- 75. J. A. Kittl, A. Veloso, A. Lauwers, K. G. Anil, C. Demeurisse, S. Kubicek, M. Niwa, M. J. H. van Dal,

O. Richard, M. A. Pawlak, M. Jurczak, C. Vrancken, T. Chiarella, S. Brus, K. Maex, and S. Biesemans, "Scalability of Ni FUSI gate processes: phase and Vt control to 30 nm gate lengths," Proc. of Symp. on VLSI Tech. (2005), p. 72.

76. S. Zafar, Y.H. Kim, V. Narayanan, C. Cabral Jr., V. Paruchuri, B. Doris, J. Stathis, A. Callegari, M. Chudzik, "A Comparative Study of NBTI and PBTI (Charge Trapping) in SiO<sub>2</sub>/HfO<sub>2</sub> Stacks with FUSI, TiN, Re Gates", Proc. of VLSI technology (2006).

#### Byoung Hun Lee

Byoung Hun Lee received a B.S. (1989) and a M.S. (1992) in Physics from Korea Advanced Institute of Science and Technology and Ph.D (2000) in electrical and computer engineering from the University of Texas at Austin. He worked at Samsung semiconductor (1992-1997) and has been with IBM since 2001. He has authored and co-authored more than 220 journal and conference papers in the various semiconductor research areas including gate oxide reliability, SOI device and process, strained silicon devices, and high-k/ metal gate process and devices. He is a senor member of IEEE and a member of the Electrochemical Society. He is currently on the assignment to SEMATECH as a manager of advanced gate stack program, managing high-k dielectric project, metal electrode project, material evaluation test structure project and electrical characterization project.

#### ● Rino Choi

Rino Choi received his Bachelor of Science and Master of Science degree in the Department of Inorganic Materials Engineering of the Seoul National University in 1992 and 1994, respectively. He received the Ph.D. in Materials Science and Engineering Program in 2004 from the University of Texas at Austin. He worked for Daewoo Motors Company from 1994 to 1999, where he worked as a development and test engineer. Since 1999, he studied various high-k dielectrics and published more than 50 journal and conference papers. After his graduation, he has been continuing the research on the electrical characterization and reliability of advanced gate stacks at SEMATECH.

#### Seung-Chul Song

Seung-Chul Song received his B.S (1996) and M.S (1998) degree in Materials Science and Engineering from University of Inchon and University of Texas at Austin, respectively. Since he recieved Ph.D degree in Electrical and Computer Engineering from University of Texas at Austin in 1999, he had worked at Motorola and Samsung during 2000~2002 and 2002~2004 respectively, participating in 0.15, 0.13 and 0.1?m CMOS process integration and device research. Since April/2004, he has been working at SEMATECH. His work at SEMATECH includes integration of dual metal gate and high-k dielectric stack into CMOS process flow, and investigation of CMOSFET device issues associated with integration of advanced gate stack

#### ● Prashant Majhi

Prashant Majhi received the Ph.D. degree in science and engineering of materials program from Arizona State University, Tempe, AZ (2000), and the Bachelors of Technology degree from the Indian Institute of Technology, Madras (1996). He joined the process development group at Philips Semiconductors in the Netherlands in 2000 and had been the project leader in module development for several CMOS and mixed signal process technologies. In Oct 2004, he joined Intel Corp., and is at SEMATECH as an Intel Assignee managing the planar CMOS scaling group. He has authored or co authored more than 100 papers in journals and conferences and holds several IC process development patents.

#### ● Paul D. Kirsch

Paul D. Kirsch received a B.S. (1995) in chemical engineering from the University of Wisconsin-Madison and Ph.D (2001) in chemical engineering from the University of Texas at Austin. He has been with IBM Systems and Technology Group since 2001. His work has focused on gate stack development. He has authored and co-authored more than 25 journal and conference papers in the various semiconductor research areas including high-k dielectric surface and interface chemistry, atomic layer deposition and high-k dielectric/metal gate devices. He holds several process development patents with IBM. He is currently on assignment to SEMATECH as project manager of the advanced gate dielectric project.

#### ● Dr. Husam Alshareef

Dr. Husam Alshareef is a Member of the Technical Staff at Texas Instruments. He obtained a Ph.D. degree in Materials Science and Engineering from North Carolina State University in 1995. He then worked as a postdoctoral researcher at Sandia National Laboratory for two years. Since then, Dr. Alshareef has spent nearly ten years in the semiconductor industry developing critical processes and materials, including ferroelectric materials, high-k dielectrics, and electrodes for memory applications as well as plasma nitrided gate dielectrics and metal gates for logic applications. He has written nearly 100 articles, two book chapters, and over 36 issued patents with nearly 20 more pending. Dr. Alshareef has also given over 40 presentations at international conferences. He is a member of IEEE and the Electrochemical Society. He frequently referees articles for international journals and magazines.

#### Hsing-Huang Tseng

Hsing-Huang Tseng joined the Advanced Products Research and Development Laboratory (APRDL) of Motorola in 1985. He has been responsible for process and integration development for a variety of gate dielectrics for advanced technologies such as high-K/metal gate stack and plasma nitridation oxynitride etc. Dr. Tseng is a Distinguished Member of Technical Staff and a Motorola Master Innovator with 25 issued U.S. patents. He received a Motorola High Impact Technology Award and a Bravo Award for his technical contributions. He has authored or co-authored over 60 papers in journals and conferences in semiconductor area and received a Golden Quills Award from Motorola for his high quality publications. Dr. Tseng was a Program Manager for Advanced Gate Stack with APRDL of Motorola before assuming the Chief Technologist and the CMOS Extension Program Manager of Front End Processes Division at SEMATECH as an assignee in 2005. He received the Ph.D. degree in Materials research from Princeton University and a BS degree in Physics from Fu-Jen Catholic University. Dr. Tseng has been invited to give talks and short courses in prestigious international conferences such as IEDM (2001) and IRPS (1996). He has served as a committee member for international conferences such as IEDM (1998, 1999) and SISC (1993-1995, 2003-2005) and is the Technical Chair of 2006 International Symposium of VLSI-Technology, System, and Applications. Dr. Tseng served on Program Advisory Board for Front End Processes of International SEMATECH and on Technical Advisory Board for Material and Process Sciences Program of Semiconductor Research Corporation (SRC) from 2001 to 2005.

#### ● Dr. Rajarao

Dr. Rajarao "Raj" Jammy joined SEMATECH for a three-year assignment from IBM. He served as a manager of Advanced CMOS Gate Stack and Surface Preparation Technologies at the T.J. Watson Research Center in Yorktown Heights, NY and previously managed the Thermal Processes and Surface Preparation Group in the DRAM development alliance between IBM and Infineon.

He holds a doctorate in electrical engineering from Northwestern University and a master's degree from the University of Rochester in Rochester, NY. He also earned a bachelor's electrical engineering degree from Bangalore University in Bangalore, India. He holds 35 U.S. patents and has co-authored nearly 50 invited/peer-reviewed papers in professional journals.