**JPE 8-2-5**

# A Study of a Simple PDP Driver Architecture using the Transformer Network

Woo-Sup Kim<sup>†</sup>, Jong-Won Shin<sup>\*</sup>, Su-Yong Chae<sup>\*</sup>, Byung-Chul Hyun<sup>\*</sup> and Bo-Hyung Cho<sup>\*</sup>

<sup>†\*</sup>Dept. of Electrical Engineering, Seoul National University, Seoul, Korea

#### **ABSTRACT**

In this paper, a cost-effective PDP driving circuit using the transformer network is proposed. Compared with the previous works, the half-bridge type energy recovery circuit recovers the reactive energy not to the capacitor but to the source. A single sustain board architecture removes the blocking switches which are placed on the discharge path in parallel, thus reducing the number of devices. A simple reset circuit generates the same waveform as the previous approaches. The circuit configuration and modified driving waveforms are compared with the previous works. The validity of the proposed simplified driver is verified through tests using a 6-inch panel

Keywords: Plasma display panel, Energy recovery circuit, Single sustain driver, Half-bridge

#### 1. Introduction

With large screen sizes, wide viewing angles and high contrast ratios, Plasma Display Panels (PDP) lead the Flat Panel Display (FPD) market along with Liquid Crystal Displays (LCD). However, the rapid development of the manufacturing process and the variety of the backlight units has boosted LCD's as the leading display device, and PDP displays are faced with new challenges such as full HD image quality, low voltage driving, high luminous efficacy and cost reduction. For the high speed addressing, the address driving voltage (V<sub>A</sub>) needs to be decreased, while the sustain voltage (V<sub>S</sub>) must be increased. Because 60% of a PDP Display's power is consumed during the sustain period, researches on the sustain circuit have been

actively continued with the aim of increasing energy recovery [1-10]. Efficiency improvement and cost reduction require a study of the overall system architecture.

In this paper, a cost effective PDP driver system which adopts the transformer network as an energy recovery circuit (ERC) is proposed. Using the positive and negative V<sub>S</sub>, the single half-bridge type ERC recovers the reactive panel energy to the source and removes the clamping diodes. The negative blocking switches (S<sub>NB</sub>) as well as the positive blocking switches (S<sub>PB</sub>) are removed, thus reducing the device count. A simple reset circuit generates the same waveform as the previous approaches. Because the proposed PDP driver produces the same relative voltage for the three electrodes, the same discharge characteristic is guaranteed.

# 2. Conventional System Configuration

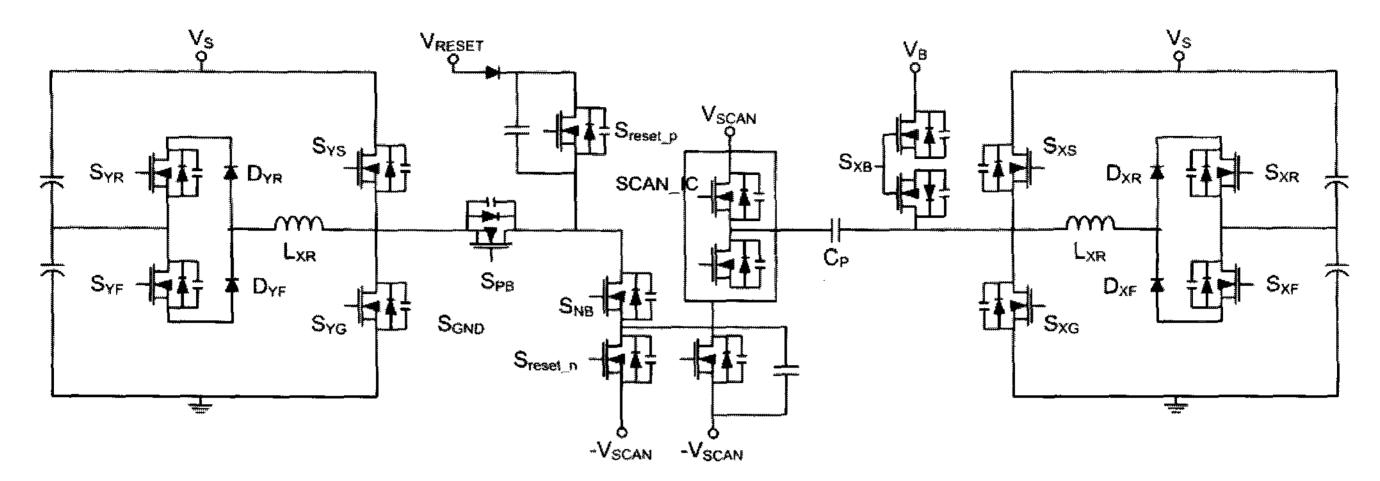

Figure 1 shows the conventional PDP driving system architecture. Three main boards exist to induce the

Manuscript received Jan. 2, 2008; revised Jan. 15, 2008.

<sup>†</sup>Corresponding Author: wskim77@snu.ac.kr

Tel: +82-2-880-1785, Fax: +82-2-878-1452, Seoul National Univ.

<sup>\*</sup>School of Electrical Eng., Seoul National Univ.

Fig. 1 System architecture of the conventional PDP driver

specific driving waveform on each electrode. Normally the address circuit only operates during the address period and therefore the main research issues are related to the X board and the Y board which are used during the scan and sustain periods. Sustain switches (Syr, Syr, Syr, Syg, Syr, Sxr,  $S_{XF}$ ,  $S_{XS}$  and  $S_{XG}$ ) operate to recover the panel energy during the sustain period. The bias voltage switch  $(S_{XB})$ turns on during the negative reset period to erase and set up the wall voltage of the panel well. S<sub>PB</sub> is used for the charge pump operation for the main reset voltage source, and  $S_{NB}$  is used to block the negative source from connection to ground. These are connected directly on the panel discharge path in series. In practice, several switches are connected in parallel to realize  $S_{PB}$  and  $S_{NB}$  because the current stress is as high as the discharge current. Therefore, the actual number of devices is increased, thus resulting in increased complexity and cost.

### 3. Proposed System Architecture

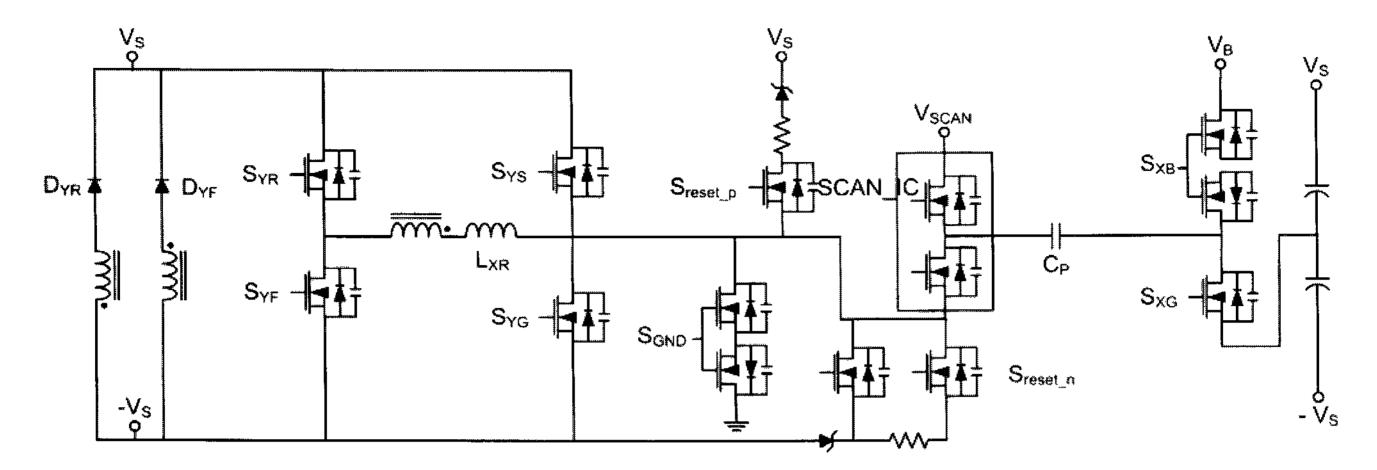

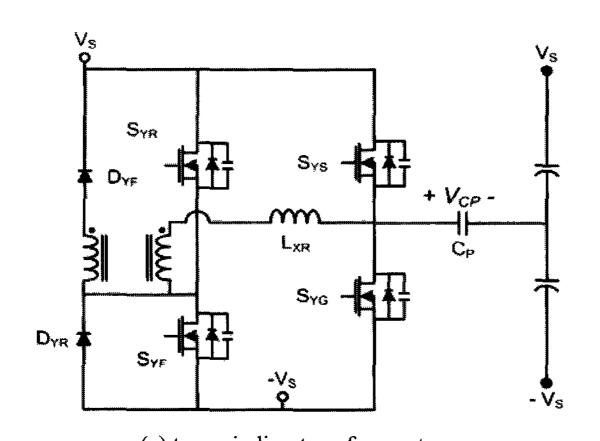

The proposed PDP driver with a reduced device count and circuit complexity is shown in Fig. 2. Compared with the full-bridge type of the sustain circuit, the half-bridge type configuration reduces the number of main and auxiliary switches in half. Using the transformer, the resonant source is replaced from the auxiliary capacitors to the transformer. The clamping diodes are removed and the leakage inductance of the transformer ( $L_{XR}$ ) is utilized as the resonant inductor. With the pairs of opposite sustain sources,  $S_{PB}$  and  $S_{NB}$  are removed and a simple reset

circuit generates the required voltage waveforms. Though the ground switches are introduced, the previously needed high current-rated devices are not required because these switches are not connected on the discharge path in series. All in all, in comparison to the previous works, the board layout is greatly simplified.

### 3.1 Reset circuit

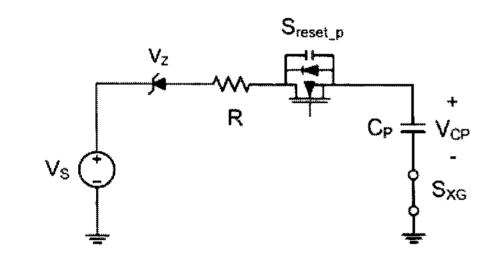

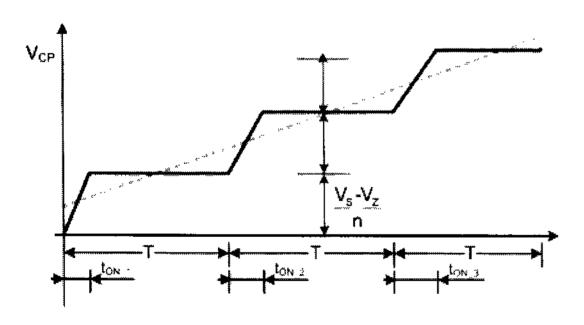

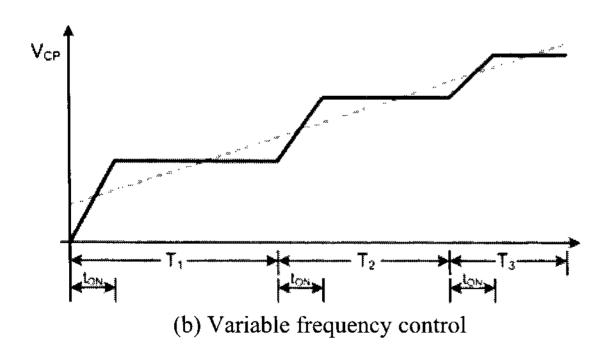

Figure 3 shows the equivalent reset circuit configuration used in the proposed PDP driver. It consists of one switch  $(S_{reset\_P})$ , a resistor (R) and a zener diode. The sustain voltage source and zener diode are used for the reset voltage source. Before the reset period starts, the panel voltage is charged up to the  $V_{SCAN}$ . With a consecutive turn-on of  $S_{reset\_P}$ , the panel voltage is increased to  $(V_S-V_Z)$ . Two control algorithms for the linear-type ramp waveform are described in Fig. 4. In the case of fixed frequency control, if the voltage step resolution is  $V_S/n$ , then the required on time in each period is determined as (1);

$$t_{on_{-}k} = RC_P \times \ln\left(\left(V_S - V_Z\right) \left(\frac{n + (k - 2)}{n}\right)\right) \tag{1}$$

If the duration time of the period is the control variable, then the required period in each voltage is described as (2)

$$T_{k} = T_{1} \left( \left( V_{S} - V_{Z} \right) \left( 1 - e^{\frac{t_{on}}{RC_{P}}} \right)^{k-1} \right)$$

(2)

Fig. 2 The proposed PDP driver

Fig. 3 The equivalent circuit during the reset period

(a) Fixed frequency control

Fig. 4 Two control algorithms for the reset voltage waveform

In both cases, increasing the value of R results in a smooth voltage transition, but the final voltage is also decreased. Using the series gate resistor ( $R_{gate}$ ) is an alternative method to achieve the wide control margin of the ramp voltage waveform. The gate sequence controller (normally an FPGA board) sends the fixed gate sequence to  $S_{reset\_P}$  and the waveform is adjusted by tuning the R and  $R_{gate}$  value. The negative reset waveform is generated using a similar operation as the positive reset waveform.

#### 3.2 Sustain driver

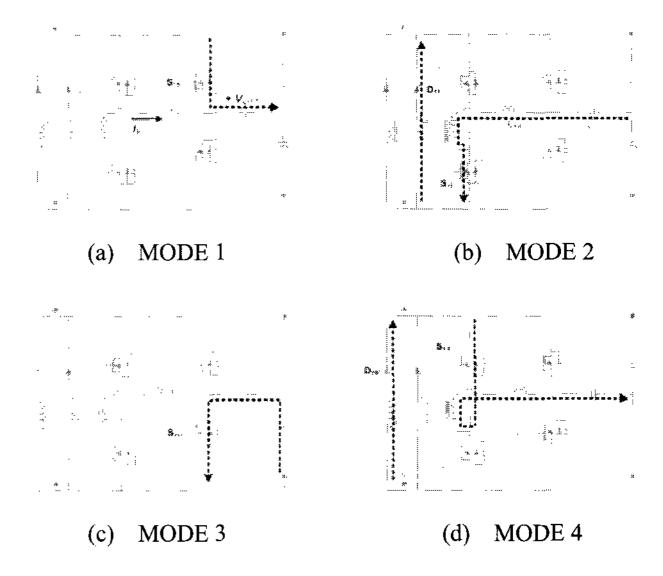

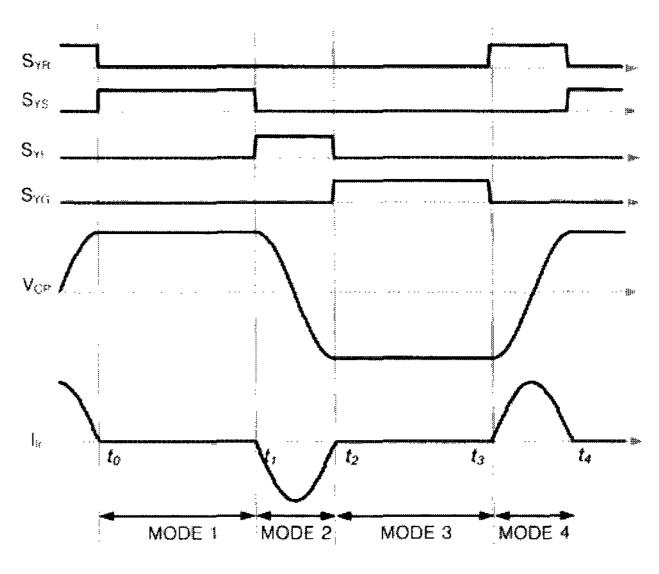

Two main aims of the sustain driver are supplying the discharge energy and recovering the stored reactive energy in the panel. The proposed circuit adopts the half-bridge type ERC, thus achieving a simple board layout. The transformer replaces the auxiliary capacitors and the body diodes of the switches are used for the clamping action. Figures 5 and 6 show the modes of operation and the key waveforms during the sustain period, in which four modes exist in one period. To analyze the circuit simply, all of the devices are assumed to be ideal. During the sustain period,  $S_{XG}$  is in the on state. The turns ratio of transformer is defined as n (the secondary side turns vs. the primary side turns).

MODE 1 [ $t_0 \sim t_1$ ]: Before  $t_0$ , the panel voltage ( $V_{CP}$ ) is charged to  $V_S$ . The inductor current ( $I_{lr}$ ) is zero.  $S_{YS}$  is turned on at  $t_0$  and the panel starts to discharge. After the discharge is finished, the wall charge is rebuilt for the next discharge.

MODE 2 [ $t_1 \sim t_2$ ]: At  $t_1$ ,  $S_{YS}$  is turned off and  $S_{YF}$  on. Negative  $V_S$  is used for the soft transition. When the primary side of the transformer conducts, the current starts to flow through the secondary side of the transformer; hence  $D_{YF}$  is turned on.  $nV_S$  is transferred to the primary side and it is subtracted from the panel's initial voltage  $(V_S)$ . Thus,  $(-2+n)V_S$  is used for the resonance source.  $V_{CP}$  starts to decrease to  $-V_S$ . The panel voltage and inductor current are expressed as (3) and (4), respectively. In (4), R includes the parasitic resistance,  $R_{DS}$  on, etc.

$$v_{CP} = \frac{\left(-V_S - V_{CP}\left(t_1\right) + nV_S\right)}{2\omega L_r C_P} \times \left(\frac{1}{\alpha^2 + \omega^2}\right)$$

$$\times \left(1 - e^{-\alpha(t - t_1)}\omega\cos\omega(t - t_1) + e^{-\alpha(t - t_1)}\alpha\sin\omega(t - t_1)\right)$$

$$+ V_{CP}\left(t_1\right)$$

$$i_{lr} = \frac{\left(-V_S - V_{CP}(t_1) + nV_S\right)}{\omega L_r} \times e^{-\alpha(t - t_1)}\sin\omega(t - t_1)$$

$$\text{where } \omega_o = \frac{1}{\sqrt{L_r C_P}}, \quad \alpha = \frac{R}{2L_r}, \omega = \sqrt{\omega_0^2 - \alpha^2}$$

MODE 3 [ $t_2 \sim t_3$ ]: When  $V_{CP}$  reaches  $-V_S$  at  $t_2$ , the zero voltage switching (ZVS) condition of  $S_{YG}$  is achieved. After  $S_{YG}$  turned on, the panel starts to discharge.  $I_{lr}$  goes to zero and  $S_{YF}$  is turned off under the zero current switching (ZCS) condition.

$$v_{CP} = \left(V_S - V_{CP}(t_2)\right) \left(1 - e^{-\frac{t - t_2}{RC}}\right) - V_{CP}(t_2)$$

(5)

$$i_{lr} = \frac{-V_S + V_{CP}(t_1)}{R} e^{-\frac{t - t_2}{RC_P}}$$

(6)

MODE 4 [ $t_3 \sim t_4$ ]: After the discharge is finished at  $t_3$ ,  $S_{XG}$  is turned off and  $S_{XR}$  is turned on. The resonant current flows through the primary side of the transformer; hence  $D_{XR}$  is turned on and the voltage of  $-nV_S$  is applied to the primary side. Similarly to MODE 2,  $C_P$  resonates with  $L_r$  and  $V_{CP}$  goes to  $V_S$ . The panel voltage and inductor current are expressed as (7) and (8), respectively.

$$v_{CP} = \frac{\left(V_S - V_{CP}(t_3) - nV_S\right)}{2\omega L_r C_P} \times \left(\frac{1}{\alpha^2 + \omega^2}\right)$$

$$\times \left(1 - e^{-\alpha(t - t_3)}\omega\cos\omega(t - t_3) + e^{-\alpha(t - t_3)}\alpha\sin\omega(t - t_3)\right) (7)$$

$$+ V_{CP}(t_3)$$

$$i_{lr} = \frac{\left(V_S - V_{CP}(t_3) - nV_S\right)}{\omega L_r} \times e^{-\alpha(t - t_3)} \sin \omega(t - t_3) \tag{8}$$

Fig. 5 Operating mode transition and equivalent circuit

Fig. 6 Key waveforms

Using the transformer network, the single half bridge-type sustain driver reduces the number of devices. Table 1 shows the comparison of the device count between the previous and proposed works. The blocking switches are removed and the resonant inductor is replaced by the leakage inductance of the transformer. The energy recovery source is substituted from the auxiliary capacitors to a single transformer. The floating ground

condition of the auxiliary switches in the previous topology is removed; hence the switch gate driver is simplified. Using the transformer turns ratio with the current injection method, the design freedom is enhanced for the ZVS and ZCS of the switches.

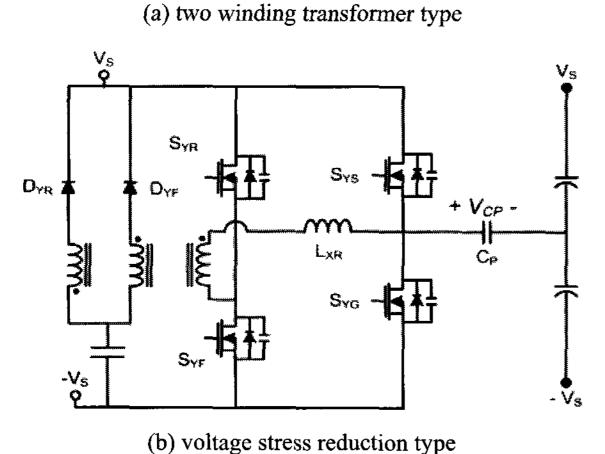

Figure 7 shows the alternative circuits of the proposed sustain driver. A simple two winding transformer reduces the complexity, as shown in Fig. 7(a). Using the auxiliary capacitor, the voltage stress of  $D_{XR}$  and  $D_{XF}$  is reduced by half, but the conduction loss is increased.

Fig. 7 Alternative circuits of the proposed sustain driver

Table 1 Comparison of the number of devices

|          |        |       |          | Recovery    |

|----------|--------|-------|----------|-------------|

|          | Switch | Diode | Inductor | Source      |

| Previous |        |       |          | Capacitor   |

| circuit  | 15     | 8     | 2        | (4)         |

| Proposed |        |       |          | Transformer |

| circuit  | 11*    | 2     | 0**      | (1)         |

<sup>\*</sup> reduce the blocking switches (2  $S_{NB}$  and 2  $S_{PB}$ )

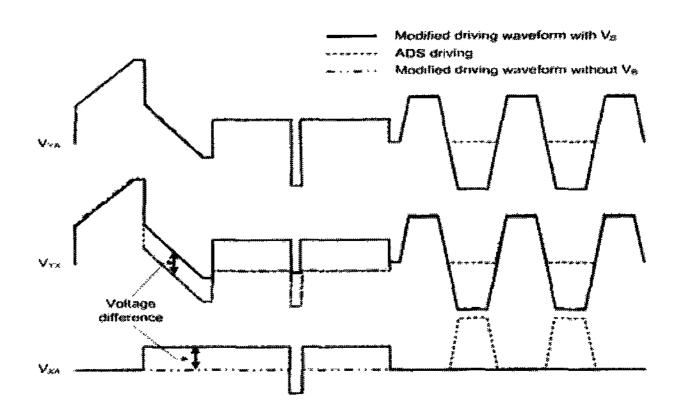

Fig. 8 Comparison of ADS and modified method for the proposed driving system

#### 3.3 Driving waveforms

Before the operation of the proposed driver, the driving voltage waveform on each electrode needs to be studied with the previous works. Figure 8 shows the various waveforms of the conventional address display separated (ADS) method and modified ADS method for the proposed driver. The case of V<sub>B</sub>-free driving is also considered. As previously studied in [11], it is able to match the voltage difference between the Y and A electrodes in all cases. However, without V<sub>B</sub>, the voltage difference between Y and X (and X and A) exists during the negative reset period. It results in the wrong erase and wall charge build-up operation. Using V<sub>B</sub>, there still exists the voltage difference between Y and X, but this exists on the sustain period and does not affect the X-Y sustain discharge. In the case of [11], the address waveform compensation method is proposed. However, this method requires a complex address circuit and more power consumption, which results in a higher cost. The proposed driving system adopts the V<sub>B</sub> circuit on the bridge board to reset the panel properly.

### 4. Experimental Results

To verify the proposed circuit, a 6-inch PDP panel is used. The voltage transition time is fixed to 0.35usec for the conventional circuit and 0.7usec for the proposed circuit. To compare the proposed circuit with the previous work, the number of devices shown in Table 1 are used for the two methods. Table 2 shows the design specification and circuit parameters used in the experiment. The driving

<sup>\*\*</sup> use the leakage inductance of the transformer

sequence explained in Fig. 8 is applied from the FPGA board to the gate drivers. Because the main issues of this paper focus on the reset and sustain discharge with the proposed driver, the address electrodes are uniformly selected all at once during the address period.

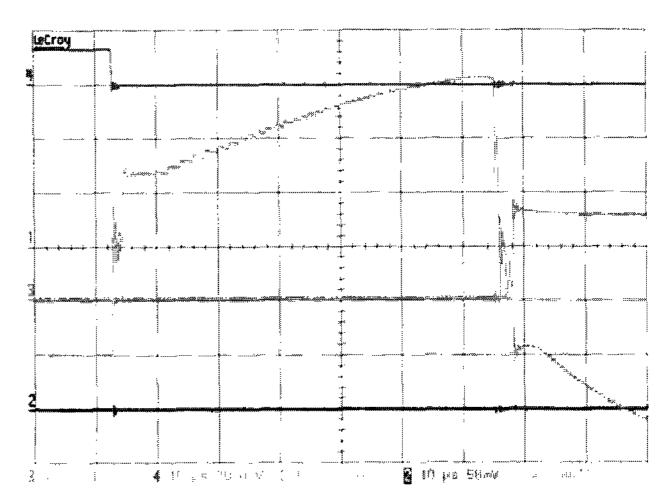

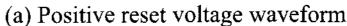

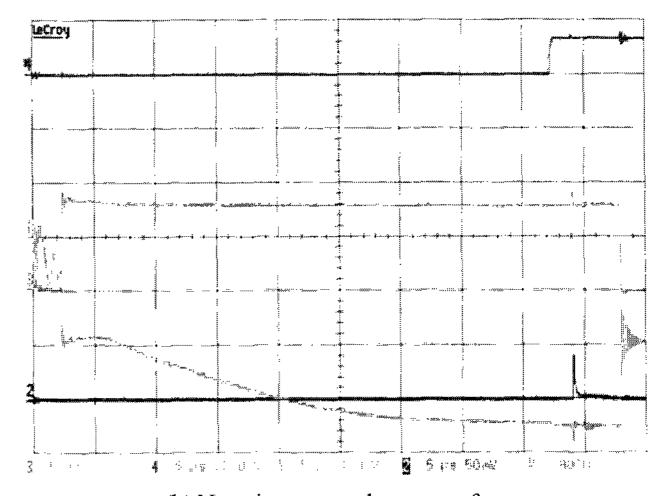

Fig. 9 shows the reset voltage waveform which is generated by the proposed PDP driver. Using the variable frequency control method explained in Fig. 4(b), with an R of  $100\Omega$ , the linear-type reset waveform is achieved. Without  $V_B$  on the X electrode, the negative reset does not decrease to the required voltage level, thus resulting in a weak address discharge and wall voltage setup.

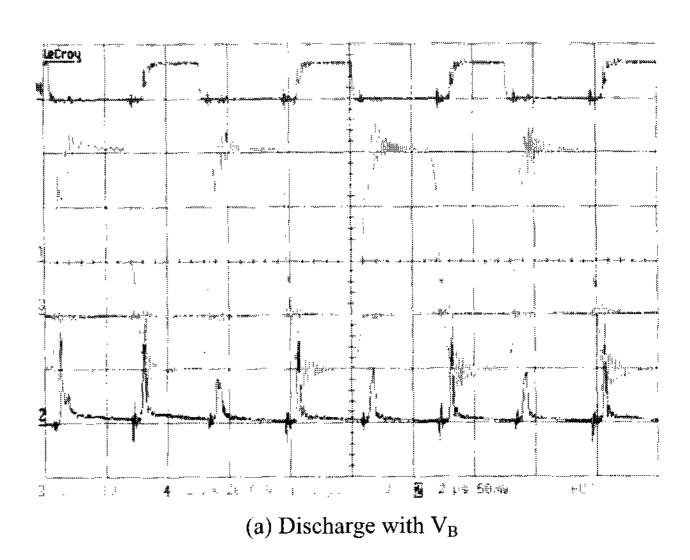

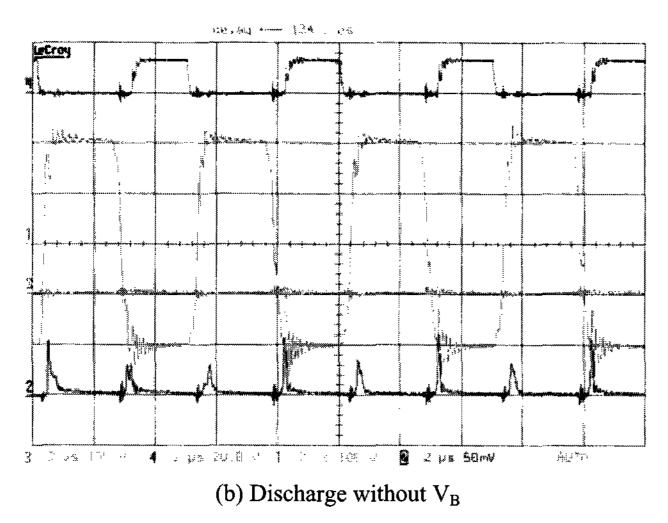

The panel sustain voltage waveforms during the sustain period, with and without  $V_B$ , are shown in Fig. 10. Using  $V_B$  during the negative reset period (shown in Fig. 10(a)) uniform light is radiated. Without  $V_B$ , the X-A waveform did not erase and setup the wall charge well, it results in the insufficient discharge between the X and A electrode during the sustain period in Fig. 10(b).

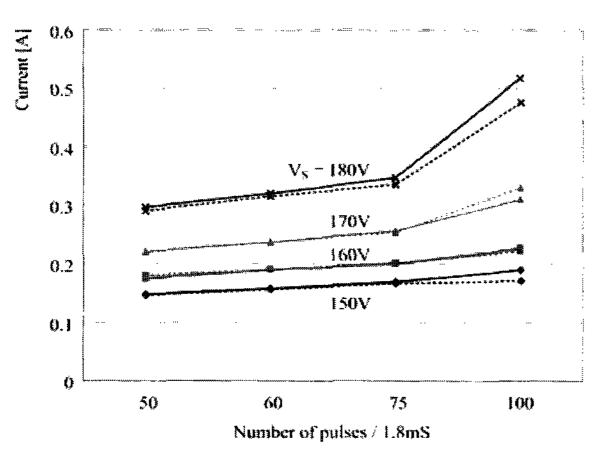

The input current of each driver is compared in Fig. 11. With a voltage variation of 150~180V, the current of the proposed circuit shows similar values as the conventional circuit and little difference is caused by the switching loss of the auxiliary switches.

#### 5. Conclusions

This paper proposes a cost-effective PDP driver using the transformer network. The positive blocking switch  $(S_{PB})$  and negative blocking switch  $(S_{NB})$  are removed by adopting a pair of opposite sustain sources. A simple reset

Table 2 Design specifications and circuit constant

|                 | Proposed circuit                                                     | Previous circuit       |

|-----------------|----------------------------------------------------------------------|------------------------|

| Switch          | FQA50N50                                                             | FQA 55N25              |

| Diode           | STTH3010A                                                            | FML-36S                |

| Resonant source | EI40, n=0.5 (4:8:8),<br>0.24*26 litz wire.<br>$L_r=1uH$ , $L_m=80uH$ | MPE capacitor, 3.3uF*4 |

| Driver IC       | IRS21851SPBF                                                         |                        |

| Panel           | 6 inch PDP cells                                                     |                        |

(b) Negative reset voltage waveform

Fig. 9 Reset voltage waveform made by the proposed PDP driver (CH1 :  $V_{CP}$ , CH2: light wave, CH3:  $V_X$ )

Fig. 10 V<sub>CP</sub> and light waveform during the sustain period (CH1: V<sub>CP</sub>, CH2: light waveform, CH4:V<sub>G SYG</sub>)

Fig. 11 Input current comparison (dotted line: previous work, solid line: proposed work)

circuit and two reset algorithms are suggested. The transformer replaces the resonant capacitor and reduces the clamping diodes. Therefore, the circuit structure is simplified and the number of devices is reduced. The propriety of the proposed PDP driver is verified through the experimental results of the prototype.

## Acknowledgment

This work is supported by Samsung SDI.

### References

[1] L. F. Weber and K. W. Warren, "Power efficient sustain driver and address drivers for plasma panel", U. S. patent 4

- 886, 349, Sept. 1989.

- [2] M. Ohba, and Y. Sano, "Energy Recovery Driver For a Dot Matrix AC Plasma Display Panel with a Parallel Resonant Circuit allowing Power Reduction", U.S. Patent 5,670,974, Sept. 1997.

- [3] H. Yang, J.-K. Kim, C.-K. Yoon, and K.-W. Whang, "A new energy recovery circuit for AC plasma display", in Proc. Society for Information Display, pp. 3842, 1998

- [4] H. B. Hsu, C. L. Chen; S. Y. Lin; and K. M. Lee, "Regenerative Power Electronics Driver for Plasma Display Panel in Sustain-Mode Operation", IEEE Trans. on Industrial Electronics, Vol. 47, No. 5, pp.1118-1125, Oct. 2000.

- [5] C. U. Kim, F. S. Kang, J. H. Cho, and W. S. Yoon, "An efficient ACPDP sustain driver employing boost-up function", in Proc. IEEE/IECON'02, Sevilla, Spain, pp. 135-139, Nov. 2002.

- [6] J.Y. Lee, J.S. Kim, N.S. Jung and B.H. Cho, "The Current Injection Method for AC Plasma Display Panel (PDP) Sustainer", IEEE Tran. Ind. Electron., Vol.51, June 2004.

- [7] S.-K. Han, G.-W. Moon and M.-J. Youn, "A Resonant Energy-Recovery Circuit for Plasma Display Panel Employing Gas-Discharge Current Compensation Method", IEEE Trans. on Power Electronics, Vol. 20, No. 1, Jan. 2005.

- [8] S.H. Kang, K.D. Cho, M.S.Kim, J.H. Ryu and K.S. Hong, "New driving method and circuits for low cost ac plasma display panel," Int. Conf. Consumer Electronics, pp. 201-202, 2005.

- [9] D.Y. Lee, J.H. Yang, and B.H. Cho, "Novel Energy-Recovery Driving Circuit for Plasma Display Panel using Regenerative Transformer", PESC03, Vol.2, pp.656-659, June 2003.

- [10] W.S. Kim, S.Y. Chae, B.C. Hyun, D.Y. Lee and B.H. Cho, "A Cost Effective PDP Sustainer using Two-Winding Transformer with Hybrid Operation", APEC, pp.294-298, Feb. 2007.

- [11] B. G. Cho, H. S. Tae "Study on Discharge Stability of Cost-Effective Driving Method Based on Vt Close Curve Analysis in AC Plasma-Display Panel", IEEE Trans. on Electron Devices, Vol. 53, No. 5, May 2006.

- [12] J. H. Yang, W. J. Chung, J. S. Kim, J. C. Jung and K. W. Whang, "A New RMSP Reset Pulse for Improved Reset Discharge Controllability in AC PDP," IEEE Tran. Plasma Science, Vol. 32, pp.288-296, Feb. 2004.

- [13] T. F. Wu, C.C. Chen, C. C. Chen and W. F. Hsu, "Design and Development of Driving Waveforms for AC Plasma Display Panels," IEEE Trans. Plasma Science, Vol.31, No.2, April 2003.

Woo-Sup Kim received the B.S. degree in electrical engineering from Kwangwoon University, Seoul, Korea, in 2003. Since 2003, he has been with School of Electrical Engineering and Computer Science, Seoul National University, where he is currently

pursuing Ph. D. degrees. His research interests are in the areas of HID ballast, resonant converters, flat panel display driver circuit and high voltage transformer. Mr. Kim is a Student Member of the Korean Institute of Power Electronics.

Jong-Won Shin received the B.S. degree in electrical engineering from Seoul National University, Seoul, Korea in 2006, where he is currently working toward his Ph. D. degree in the School of Electrical Engineering. His research interests are in the

areas of plasma display panel driver, high-efficiency power converter and power factor correction circuit. Mr. Shin is a Student Member of the Korean Institute of Power Electronics.

**Su-Yong Chae** received the B.S. and M.S. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejon, in 1998 and 2000, respectively, and is currently pursuing the Ph.D. degree at Seoul National

University, Seoul, Korea. From 2000 to 2005, he was a Research Engineer with Samsung SDI where he developed plasma display panel video processing circuits. His research interests include digital display power systems and digital control approach of dc-dc converters. Mr. Chae is a Student Member of the Korean Institute of Power Electronics.

Byung-Chul Hyun received the B.S. degree in electrical engineering from KyungPook National University (KNU), Daegu, Korea, in 2004 and the M.S. degree from Seoul National University (SNU), Seoul, Korea, in 2006 where he is currently pursuing the Ph.D.

degree. His interests include resonant converters, multiple output converters, and power factor correction (PFC) circuits. Mr. Hyun is a Student Member of the Korean Institute of Power Electronics.

**Bo-Hyung Cho** received the B.S. and M.S. degrees from the California Institute of Technology, Pasadena, and the Ph. D. degree from the Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, all in electrical engineering. Prior to his

research at Virginia Tech, he worked as a member of technical staff with the Power Conversion Electronics Department, TRW Defense and Space System Group. From 1982 to 1995, he was a Professor with the Department of Electrical Engineering, Virginia Tech. In 1995, he joined School of Electrical Engineering, Seoul National University, Seoul, Korea, where he is currently a Professor. His research interests include power electronics, modeling, analysis and control of spacecraft power processing equipment, and distributed power systems. Prof. Cho received the 1989 Presidential Young Investigator Award from the National Science Foundation. His is a member of Tau Beta Pi.