# Non-Overlapped Single/Double Gate SOI/GOI MOSFET for Enhanced Short Channel Immunity

Sudhansh Sharma\*\*\* and Pawan Kumar\*\*

Abstract— In this paper we analyze the influence of source/drain (S/D) extension region design for minimizing short channel effects (SCEs) in 25 nm gate length single and double gate Silicon-on-Insulator (SOI) and Germanium-on-Insulator (GOI) MOSFETs. A design methodology, by evaluating the ratio of the effective channel length to the natural length for the different devices (single or double gate FETs) and technology (SOI or GOI), is proposed to minimize short channel effects (SCEs). The optimization of non-overlapped gate-source/drain i.e. underlap channel architecture is extremely useful to limit the degradation in SCEs caused by the high permittivity channel materials like Germanium as compared to that exhibited in Silicon based devices. Subthreshold slope and Drain Induced Barrier Lowering results show that steeper S/D gradients along with wider spacer regions are needed to suppress SCEs in GOI single/double gate devices as compared to Silicon based MOSFETs. A design criterion is developed to evaluate the minimum spacer width associated with underlap channel design to limit SCEs in SOI/GOI MOSFETs.

Index Terms—Silicon-on-Insulator (SOI), Germanium-on-Insulator (GOI), single gate MOSFET, double gate MOSFET, gate-underlap design, source/drain (S/D) profile optimization, short channel effects (SCEs), low-voltage applications

Manuscript received Mar. 18, 2009; revised Aug. 21, 2009.

\*Department of Information Technology and Systems Sciences, Vishveshwarya School of Business Management (VSBM), 20km Ghaziabad-Bulandshahar, G.T. Road, Near Dadri, Greater Noida Phase II, Dist.G.B.Nagar-203207(U.P.), India Phone: +91–9818946404, +91-120-2662173, Fax: +91-120-2662166

\*\* Department of Physics, M.M.H. College (Affiliated to C.C.S. University Meerut), Ghaziabad – 201 001, Uttar Pradesh, India E-mail: sudhansh74@rediffmail.com

#### I. Introduction

Over the past few years fully depleted (FD) Siliconon-Insulator (SOI) based single and multiple gate MOSFETs have emerged as possible candidates for device scaling at the end of ITRS roadmap [1]. Amongst the many possible candidates for scaling, double-gate silicon (DG) MOSFETs are considered to possess appropriate features to constitute devices for nanoscale circuit design because of the excellent suppression of short-channel effect (SCEs), lower gate leakage current, higher oncurrent, and better subthreshold slope values [2, 3]. DG MOSFETs can be fabricated with their channel in the plane of the wafer or as vertical structures. DG devices in the standard configuration have exhibited record currents [4] whereas other topologies such as the pillar FET [5] or the FinFET [6-9] are much easier to integrate. As the body thickness is controlled by lithographic and etching processes, it will be increasingly difficult to fabricate vertical devices with ultra thin silicon films. The problem of access resistance is more severe in vertical FETs because they lack the equivalent of deep source/drain region that makes the formation of low resistance silicide contacts possible [10, 11]. The planar fabrication approach does allow fabricating ultra thin body devices, a key requirement for suppressing SCEs. Controlling the width uniformity of a relatively tall fin structure (50-60 nm) and then attaining a smooth fin surface on the roughest plane (110) on the silicon substrate are the crucial challenges. It has also been shown that fins with tapered bottom profile degrades SCEs, produces a non-uniform current flow and current crowding in the vertical direction [12]. In addition, the mobility of an aggressively scaled channel greatly depends on surface roughness-induced scattering.

In addition to changing the transistor architecture, channel engineering has been an attractive option to enhance device performance. One such concept of channel engineering is the use of "non-overlapped" or "underlapped" gate-source/drain structure with lowdoped/intrinsic channel [13] to facilitate MOS scaling to nanoscale gate lengths. In gate-underlap architecture, source/drain (S/D) extension region profiles are designed such that the extension region doping does not approach the gate edge i.e. the channel and extension regions adjacent to the gate will be without any dopant. The concept of underlapped channel design has been experimentally applied in bulk - MOSFETs [14] and vertical FinFETs [15], multi-bridge-channel FETs [16], for digital applications and planar single gate (SG) SOI MOSFETs [17] for ultra-low-voltage analog/rf applications. Published work on underlap MOSFETs has shown great potential for digital [18-29] and analog/rf applications [30-33].

Recently, Germanium (Ge) has re-attracted interest for high-performance devices because of its much higher intrinsic electron and hole mobility compared with silicon [34-36]. The major problem of Ge CMOS device fabrication is the thermal and chemical instability of Ge oxides as gate dielectrics since Ge native oxides give rise to rough surface and high density of interface states [37, 38]. The best dielectrics for use in Ge MOSFETs are Ge oxynitrides, which have better stability than native Ge oxides [39]. The recent development of dielectric films with high dielectric constants to replace SiO2 in Si MOSFETs becomes promising in implementing such dielectrics in Ge MOSFETs. Single gate Ge MOSFETs with various gate dielectrics (Ge oxynitride and high- $\kappa$ ) have been manufactured and measured recently [40-44]. The improved performance of Ge MOSFETs with greater mobility than Si MOSFETs was demonstrated using high- $\kappa$  gate dielectrics [35]. Therefore, it is worthwhile to raise the possible advantages of replacing Si with Ge in future DG MOSFETs. In this paper, Ge based SG or DG devices have been referred as Germanium-on-Insulator (GOI).

In this paper, we use the expression of effective channel length for gate—source/drain underlap devices and natural/characteristic length scale for single and double gate SOI/GOI MOSFETs to evaluate the design criterion to suppress SCEs. Our earlier work [29] highlightted the usefulness of lateral S/D doping gradient

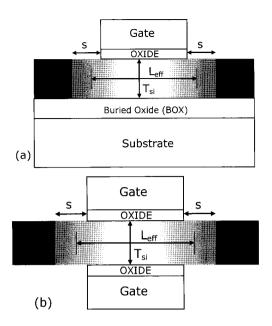

**Fig. 1.** Schematic diagram of (a) single gate (SG) SOI MOSFET and (b) double gate (DG) SOI MOSFET.

along with S/D roll-off width to suppress short channel effects in SOI devices. In this work, we highlight the usefulness of underlap channel profile to suppress short channel effects in GOI based SG/DG MOSFETs. Optimal design guidelines are proposed for 25 nm underlap channel single/double gate SOI/GOI MOSFETs to suppress SCEs based on the ratio of effective channel length to natural/characteristic length. The present work provides valuable design insights in the performance of nanoscale DG SOI/GOI devices with optimal S/D engineering and serves as a tool to optimise important device and technological parameters for low power 45 and 32 nm technology nodes.

### II. RESULTS AND DISCUSSION

# 1. Natural length scale $(\lambda)$ and effective channel length (Leff)

As demonstrated in [2, 45-50] and our earlier paper [29], the natural length governs the influence of lateral field on the channel potential and influences the extent of short channel effects (SCEs) inherent to a structure. The natural length depends on device geometry and boundary conditions. Using the same approach as described in our earlier work [29], the eigenvalue equation

determining the natural length for single gate (SG) SOI MOSFETs is given as

$$\tan(k_{\text{nSG\_SOI}} \, \varepsilon_{\text{si}}) = \frac{\left(C_{\text{fox}} + C_{\text{box}}\right) k_{\text{nSG\_SOI}} \, \varepsilon_{\text{si}}}{k_{\text{nSG\_SOI}}^2 \, \varepsilon_{\text{si}}^2 - C_{\text{fox}} \, C_{\text{box}}} \tag{1}$$

where  $k_{\rm nSG\_SOI}$  are the eigenvalues for single gate SOI devices,  $C_{\rm fox}$  (=  $\varepsilon_{\rm ox}/T_{\rm fox}$ ) is the front oxide capacitance,  $C_{\rm box}$  (=  $\varepsilon_{\rm ox}/T_{\rm box}$ ) is the back/buried oxide capacitance,  $T_{\rm si}$  is the silicon film thickness,  $T_{\rm fox}$  is the front oxide thickness,  $T_{\rm box}$  is the buried oxide thickness and  $\varepsilon_{\rm ox}$  is the permittivity of oxide. The relationship between eigenvalue and natural length is described later. Similarly, for a double gate (DG) SOI MOSFETs, the eigenvalue equation is obtained as

$$\tan(k_{\text{nDG\_SOI}} \, \varepsilon_{\text{si}}) = \frac{\left(2 \, C_{\text{ox}}\right) \, k_{\text{nDG\_SOI}} \, \varepsilon_{\text{si}}}{k_{\text{nDG\_SOI}}^2 \, \varepsilon_{\text{si}}^2 - C_{\text{ox}}^2} \tag{2}$$

where  $k_{nGG\_SOI}$  is the eigenvalue for double gate SOI device. For Germanium–on–Insulator (GOI) based SG and DG devices the eigenvalue equation is obtained as

$$\tan(k_{\text{nSG\_GOI}} \, \varepsilon_{\text{Ge}}) = \frac{\left(C_{\text{fox}} + C_{\text{box}}\right) \, k_{\text{nSG\_GOI}} \, \varepsilon_{\text{Ge}}}{k_{\text{nSG\_GOI}}^2 \, \varepsilon_{\text{Ge}}^2 - C_{\text{fox}} \, C_{\text{box}}}$$

(3)

$$\tan(k_{\text{nDG\_GOI}} \, \varepsilon_{\text{Ge}}) = \frac{\left(2 \, C_{\text{ox}}\right) k_{\text{nDG\_GOI}} \, \varepsilon_{\text{Ge}}}{k_{\text{nDG\_GOI}}^2 \, \varepsilon_{\text{Ge}}^2 - C_{\text{ox}}^2} \tag{4}$$

where  $k_{\rm nSG\_GOI}$  and  $k_{\rm nGG\_GOI}$  are the eigenvalues for single and double gate GOI devices, respectively. The natural length  $(\lambda_{\rm n})$  can be obtained for SG/DG SOI/GOI MOFETs as  $\lambda_{\rm n} = n\pi/k_{\rm n}$  [50] where  $k_{\rm n}$  represents the eigenvalue determined from eqns. (1)–(4) for different types of devices.

To design a device free of short channel effects (SCEs), the minimum channel potential should be as small as possible [2, 29, 48-50]. This minimum channel potential can be decreased by increasing the channel doping or by reducing the natural length ( $\lambda_n$ ) (or increasing the eigenvalue,  $k_n$ ). Reduction of  $\lambda_n$  reduces the minimum channel potential in a much efficient manner as compared to increasing the doping which is mainly done to adjust the threshold voltage. Since  $\lambda_n$  depends on  $T_{si}$  and  $T_{ox}$ , it provides a measure of short channel effects in a given structure and thus can be interpreted as the short channel immunity factor of a given structure [29].

A smaller value of  $\lambda_n$  implies thin silicon film, thin gate oxide, lower permittivity for channel material i.e. improved gate controllability and advanced device architecture (double instead of single). Thus, as device dimensions penetrate into nanoscale regime, a smaller value of  $\lambda_n$  is required to operate the device as in the long channel regime by increasing the  $L_{\rm eff}/\lambda_n$  ratio [2, 29, 48-50]. Since the first root of eigenvalue equations described above is sufficient to describe SCEs in different devices, we will only focus on the lowest eigenvalue ( $\lambda_1 = n\pi/k_1$ ) in our analysis.

In the present work, we have modeled the effective channel length in gate-source/drain underlap devices (SG/DG SOI/GOI FETs) using the expression presented in [24] and is given as

$$L_{\text{eff}} = L_{\text{g}} + 2s \left( 1 - \sqrt{\frac{2/\ln(10)}{s/d}} \sqrt{\ln\left(\frac{N_{\text{SDO}}}{\eta_{\text{SD}}}\right)} \right)$$

(5)

where  $\eta_{\rm SD}$  is the S/D doping level at which  $L_{\rm eff}$  is extracted,  $L_{\rm g}$  is the gate length, s is the S/D roll-off width (also called as the spacer width), d is the S/D doping gradient (expressed in nm/decade) evaluated at the gate edge as  $d = 1/dN_{SD}(x)/dx$ . S/D profile was modeled using the expression  $N_{\rm SD}(x) = N_{\rm SDO} \exp(-x^2/\sigma^2)$  where  $N_{\rm SDO}$  is the peak S/D doping and  $\sigma$ , lateral straggle parameter, governs the S/D profile roll-off  $\left(\sigma = \sqrt{2sd/\ln(10)}\right)$ [24] in the channel direction. Although underlap design can limit SCEs due to longer Leff (as compared to conventional overlap design), an underlap device with a very wide spacer can result in an additional parasitic series resistance. This series resistance will not signifycantly degrade the device performance if operated at lower drive currents and voltages i.e. underlap design is most useful for low voltage/power applications.

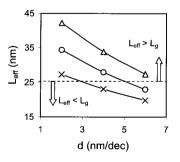

**Fig. 2.** Variation of effective channel length  $(L_{\rm eff})$  with S/D doping gradient (d) for various values of spacer widths. Notations:  $\times - \times : s/L_{\rm g} = 0.25$ ,  $\infty - \infty : s/L_{\rm g} = 0.50$ ,  $\Delta - \Delta : s/L_{\rm g} = 0.75$ .

Fig. 2 shows the variation of effective channel length  $(L_{\rm eff})$  on S/D doping gradients. A variation of S/D roll—off widths (s) along with lateral S/D doping gradient (d) results in the modulation of effective channel length  $(L_{\rm eff})$  in a nanoscale non—classical (gate underlap) single and double gate MOSFET. Wider roll—off widths along with steeper doping gradient (lower d values) result in a longer  $L_{\rm eff}$  whereas a shorter spacer width along with gradual doping gradient (higher d values) yields shorter  $L_{\rm eff}$ . It is important to note that the optimisation of s and d for short channel immunity must be considered along with transistor structural parameters for single and double gate MOSFETs.

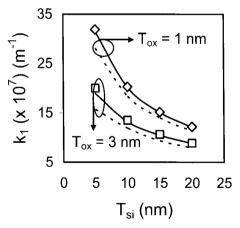

Fig. 3 shows the comparison between the eigenvalues determined by our approach and using the expression in [50]. Our results are in good agreement with those derived by Frank *et al.* [50] by solving the 2D Poisson's equation in the oxide and silicon regions. This shows that for the device parameters considered in the present work, solving the 2D Poisson's equation only in the silicon film itself is sufficient to provide a reasonable estimation of SCEs in DG MOSFETs. We have restricted our analysis to a dielectric with permittivity of 3.9  $\varepsilon_0$  ( $\varepsilon_0$  is the permittivity of free space) as gate dielectric and therefore eqns. (2)–(5) are reasonable to estimate the natural/characteristic length in a given structure.

Fig. 3. Dependence of lowest eigenvalue  $(k_1)$  for DG MOSFET on silicon film thickness  $(T_{\rm si})$  for various values of gate oxide thickness  $(T_{\rm ox})$ . Symbols represent  $k_1$  values calculated for DG SOI MOSFETs by equation in [50] whereas solid lines represent  $k_1$  values for DG SOI MOSFETs evaluated by eq. (3) and dotted lines denote  $k_1$  values for DG GOI MOSFETs calculated by eq. (5) in the present work. Notations:  $\delta T_{\rm ox} = 1$  nm and  $\Box T_{\rm ox} = 3$  nm.  $T_{\rm box} = 25$  nm for SG devices.

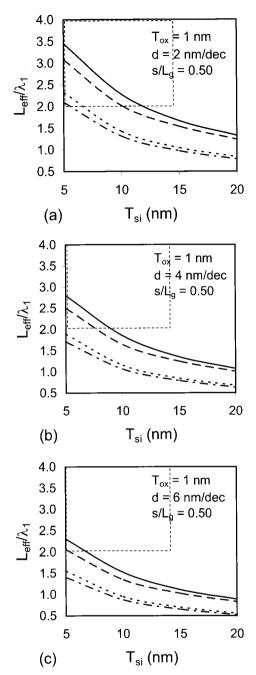

Fig. 4 shows the dependence of  $L_{\rm eff}/\lambda_1$  on silicon film thickness  $(T_{\rm si})$  for various doping gradients and devices. Largest  $L_{\rm eff}/\lambda_1$  ratio is obtained at lower d values because of the greater contribution of spacer regions to the effective channel length. The lower permittivity of Si

yields lower natural length scale  $(\lambda_1)$  value as compared to that achieved with Ge i.e.  $(\lambda_1)_{DG\_SOI}/(\lambda_1)_{DG\_GOI} \cong 0.88$  at  $s/L_g = 0.50$  and is independent of d. Similar values (~0.88) are also observed for SG devices. Since SG/DG devices should be designed such that  $L_{eff}/\lambda_1 > 2$  to avoid short channel effects, S/D design with d = 6 nm/dec (S/D dopant spill into the channel as spacer is not wide enough) will not be useful in nanoscale devices.

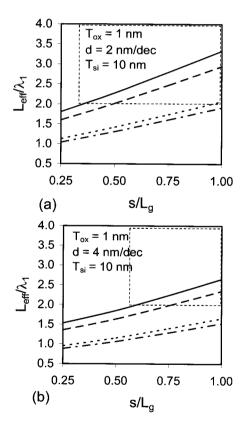

Fig. 5 shows the dependence of  $L_{\rm eff}/\lambda_1$  on  $s/L_{\rm g}$  values for two different doping gradients and various devices (SG/DG and SOI/GOI). Wider spacers or larger  $s/L_{\rm g}$  values result in longer effective channel length values and lead to higher  $L_{\rm eff}/\lambda_1$  values for all devices. SG underlap devices designed with gradual S/D profiles i.e. higher d values will exhibit significant SCEs as  $L_{\rm eff}/\lambda_1$  is lower than 2 even for  $s/L_{\rm g} \sim 1$ . DG SOI devices should be designed with  $s/L_{\rm g} > 0.4$  in order to achieve  $L_{\rm eff}/\lambda_1 = 2$  at d=2 nm/dec whereas to attain the same degree

Fig. 5. Dependence of  $L_{\rm eff}/\lambda_1$  ratios for SG/DG SOI/GOI MOSFET on spacer to gate length ratio ( $s/L_{\rm g}$ ) for (a) d=2 nm/dec and (b) d=4 nm/dec. Notations: —— DG SOI FET, — — DG GOI FET, …… SG SOI FET and —— SG GOI MOSFET.  $T_{\rm box}=25$  nm for SG devices.

of suppressed SCEs in DG GOI devices ( $L_{\rm eff}/\lambda_1 = 2$ ),  $s/L_{\rm g}$  should be maintained around 0.5. Therefore, GOI devices will require wider spacers in comparison to SOI MOSFETs for attaining the same degree of short channel immunity. At higher S/D gradients, DG SOI devices should be designed such that  $s/L_{\rm g} > 0.6$  whereas GOI based DG devices should have a minimum spacer width of  $0.7L_{\rm g}$ .

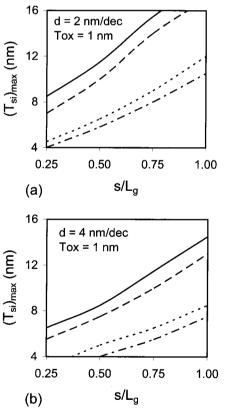

Fig. 6 shows the requirement for selecting silicon film thickness for various  $s/L_{\rm g}$  and d values such that  $L_{\rm eff}/\lambda_{\rm l}=2$  i.e. devices are designed to be immune from SCEs. As shown in the figure, DG SOI MOSFETs show greater flexibility in the choice of  $T_{\rm si}$  as compared to SG devices. For a typical S/D profile with d=2 nm/dec and  $s/L_{\rm g}=0.5$ , DG SOI devices require maximum  $T_{\rm si}$  of  $\sim 13$  nm whereas DG GOI devices should be designed with  $(T_{\rm si})_{\rm max}$  of 10 nm to achieve similar levels of short channel immunity. In case of SG devices, the range of  $T_{\rm si}$  values is limited to 6 and 5 nm in SOI and GOI devices, respectively. The maximum allowable  $T_{\rm si}$  value reduces

**Fig. 6.** Maximum allowable film thickness  $(T_{\rm si})_{\rm max}$  as a function of spacer to gate length ratio  $(s/L_{\rm g})$  for (a) d=2 nm/dec and (b) d=4 nm/dec. Notations: — DG SOI FET, — — DG GOI FET, …… SG SOI FET and — SG GOI MOSFET.  $T_{\rm box}=10$  nm for SG devices.

if a gradual S/D profile (~ 4 nm/dec) is used instead of a steeper S/D profile. It is evident from these results that in order to improve the scalability and short channel immunity in SG devices, silicon film thickness must be reduced and/or spacer width be increased (at a constant d). Reducing film thickness involves the problem of producing a thin, defect free and uniform mono-crystalline silicon layer (<10 nm), which is a technological issue. The use of underlap design is beneficial as it allows the use silicon films > 8 nm in SOI/GOI DG devices without compromising the electrostatic integrity of the device.

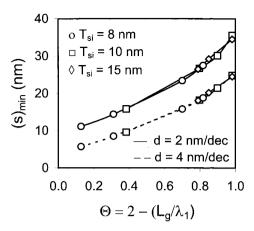

In order to design devices with suppressed SCEs,  $L_{\rm eff}/\lambda_1$  should be greater or equal to 2 [29]. The first step in selecting the device and S/D profile parameters is the evaluation of  $L_{\rm g}/\lambda_1$ . If this ratio is 2, the device will be immune from SCEs and underlap channel design should be avoided as it will add extra series resistance (due to the contribution of non-overlapped gate-S/D regions) which will degrade the performance for above threshold operation. If the term  $L_{\rm g}/\lambda_1$  is less than 2, the additional contribution of S/D regions to achieve  $L_{\rm eff}/\lambda_1 = 2$  should be computed as  $\Theta = 2 - (L_{\rm g}/\lambda_1)$ . The minimum spacer width,  $(s)_{\rm min}$  associated with the underlap profile to achieve immunity from SCEs can be computed as

$$(s)_{\min} = \frac{\lambda_1 \Theta}{2} + \sqrt{(s)_{\min}} \left( \sqrt{\ln \left( \frac{N_{SDO}}{\eta_{SD}} \right)} \sqrt{\frac{2d}{\ln(10)}} \right)$$

(6)

$\lambda_1$  in the above equation depends on device geometry and will be different for SG/DG SOI/GOI devices. This equation allows for an efficient estimation of the S/D profile requirements to limit SCEs for a given topology. As shown in Fig. 7, lower  $(s)_{min}$  values are required for thin silicon films and lower S/D doping gradients. Selecting a device geometry (SG or DG) or even a technology (SOI or GOI) will only change the value of  $\Theta$  but the variation of  $(s)_{\min}$  with  $\Theta$  will remain the same i.e.  $(s)_{min}$  data points lie on the same curve (for a given d value). For example designing DG devices with  $T_{ox} = 1$ nm and  $T_{\rm si} = 10$  nm results in  $\lambda_1$  of 15.5 nm and 20.8 nm for SOI and GOI technology, respectively. These values translate into  $\Theta$  values of 0.384 and 0.798 which correspond to (s)<sub>min</sub> of 9.6 nm (SOI) and 18.2 nm (GOI) respectively for d = 2 nm/dec. It is advisable to compute

**Fig. 7.** Minimum spacer width to achieve immunity form short channel effects as a function of d and  $T_{si}$ .

**Fig. 8.** Dependence of Subthreshold slope (S-slope) on doping gradient for DG SOI and DG GOI devices for (a)  $s/L_g = 0.25$  and  $s/L_g = 0.75$  and (b)  $s/L_g = 0.50$  and  $s/L_g = 1.0$ . Parameters:  $T_{\rm ox} = 1.3$  nm,  $N_{\rm a} = 10^{15}$  cm<sup>-3</sup>,  $T_{\rm si} = 10$  nm and  $V_{\rm ds} = 50$  mV. The reference S-slope values for DG SOI devices are taken from [24].

s in a given underlap design instead of d as it is dependent on the process and quite difficult to change. Equation (6) provides a simple and effective method of estimating the minimum spacer width for a given device/technology and yielding a device design with

immunity from short channel effects.

By adopting the similar procedure as described in [24, 46-47], the expression of minimum channel potential  $(\Psi_m)$  can be derived i.e. eq. (A3) of [24]. The carrier density  $(n_m)$  at the position of minimum channel potential  $(x_{\min})$  is given as  $n_m = (n_i^2/N_a) \exp(q \Psi_m/kT)$  where  $n_i$  is the intrinsic carrier concentration,  $N_a$  is the film doping, q is the electron charge, k is the Boltzmann constant and T is the temperature. Assuming that the Subthreshold slope (S-slope) is related to carrier concentration at  $x_{\min}$  (and hence to the  $\Psi_m$ ) [46-47, 51-53], S-slope can be obtained as  $\partial V_{gs}/\partial \log I_{ds} \approx \ln(10)$   $\partial V_{gs}/\partial \ln(n_m) \approx \ln(10) (kT/q) (\partial \Psi_m/\partial V_{gs})^{-1}$ . This expression for evaluating S-slope has been widely used in several prior published papers [24, 46-47, 51-55].

The threshold voltage ( $V_{\rm TH}$ ) can be defined as the gate voltage at which the minimum sheet density of inversion carriers reaches a value  $Q_{\rm TH}$  [56] adequate for identifying the turn-on condition, which can be approximated as

$$Q_{TH} = \int_{0}^{T_{si}} n_{i} \exp(q\Psi_{m}/kT) dy$$

At the position of minimum channel potential,  $Q_{\rm TH}$  can be approximated [56] as  $\Psi_{\rm m} = \left(\frac{kT}{q}\right) \left(\ln\left(\frac{Q_{\rm TH}}{n_i T_{\rm si}}\right)\right)$ , with

$Q_{\rm TH}=5.5\times 10^{10}$  cm<sup>-2</sup> [55]. In terms of the classical method of determining the threshold voltage i.e. by equating the minimum channel potential,  $\Psi_{\rm m}$  to  $\kappa \varphi_{\rm f}$  (where  $\kappa$  is a fitting parameter,  $\varphi_{\rm f}$  is the Fermi potential),  $Q_{\rm TH}$  value reported above corresponds to  $\kappa=1.35$ . The parameter  $Q_{\rm TH}$  (or  $\kappa$ ) relates to the current level used in experimental characterization of threshold voltage. It should be noted that  $\kappa$  is lower than the classical value of 2 for bulk MOS devices. The use of minimum channel potential, obtained via the analytical solution of the Poisson's equation, to evaluate threshold voltage is a well defined technique and has been reported in several published papers [24, 51-57].

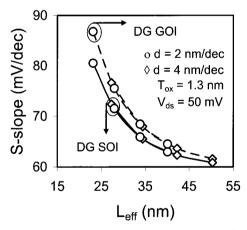

The natural length analysis is extended to evaluate the Subthreshold slope (S-slope) and Drain Induced Barrier Lowering (DIBL) for DG devices using the expressions proposed by Kranti et al., [24]. For a fair comparison between DG SOI and DG GOI MOSFETs, all device

parameters are kept the same for both types of devices, except for the Ge intrinsic doping concentration of  $n_{iGe}$  =  $2 \times 10^{13}$  cm<sup>-3</sup> affecting the built-in potential across the source/drain-channel junctions and the dielectric constant  $\varepsilon_{Ge} = 16\varepsilon_0$  ( $\varepsilon_0$  is the permittivity of free space) affecting the natural channel length  $k_{nDG GOI}$ . As shown in Fig. 8, S/D doping gradient must be maintained below 3 nm/dec for GOI devices whereas higher d value of 4 nm/dec is required to achieve S-slope lower than 80 mV/dec for  $s/L_g = 0.25$ . An increase in  $s/L_g$  to 0.50 relaxes the constraint on d from 3 to 5 for GOI and from 4 to 5 for SOI devices to achieve S-slope of 80 mV/dec. Wider spacers ( $s/L_g > 0.5$ ) can achieve lower S-slope values independent of d. Targeting an S/D process with d= 3 nm/dec,  $s/L_g$  = 0.25 can achieve S-slope = 80 mV/dec whereas larger spacers  $\sim 0.35L_{\rm g}$  would be more appropriate for GOI devices for the same S-slope values.

Fig. 9 shows the dependence of S-slope on effective channel length ( $L_{\rm eff}$ ) for SOI and GOI devices. Underlap design with gradual d values at narrow spacers achieves higher S-slope values due to a lower  $L_{\rm eff}$  because of dopant spill into the channel. S/D design with d=2 nm/dec and  $s/L_{\rm g}=0.25$  yields  $L_{\rm eff}=24$  nm resulting in S-slope values of 87 mV/dec and 81 mV/dec for GOI and SOI DG MOSFETs i.e. 6 mV/dec higher S-slope for GOI devices. For longer channel lengths ( $\sim$  40 nm), the difference between S-slope values for GOI and SOI

**Fig. 9.** Dependence of Subthreshold slope (S-slope) on effective channel length ( $L_{\rm eff}$ ) for DG SOI and GOI devices. The maximum S-slope value corresponding to a particular d value corresponds to  $s/L_{\rm g}=0.25$  whereas the minimum S-slope value signifies  $s/L_{\rm g}=1.0$ . The reference S-slope values for DG SOI devices are taken from [24]. Parameters are same as in Fig. 8.

**Fig. 10.** Dependence of Drain Induced Barrier Lowering (DIBL) on doping gradient for DG SOI and DG GOI devices for (a)  $s/L_g = 0.25$  and  $s/L_g = 0.75$  and (b)  $s/L_g = 0.50$  and  $s/L_g = 1.0$ . Parameters are same as in fig. 8. The reference DIBL values for DG SOI devices are taken from [24].  $DIBL = |(V_{th1}-V_{th2})/(V_{ds1}-V_{ds2})|$  where  $V_{th1}$  and  $V_{th2}$  are threshold voltages extracted at drain bias of  $(V_{ds1})$  50 mV and  $(V_{ds2})$ 1.0 V.

devices reduces to 2 mV/dec with both exhibiting ideal values of 60 mV/dec for  $L_{\text{eff}} > 50$  nm.

Fig. 10 shows the dependence of DIBL on S/D doping gradient (d) for SOI and GOI devices. A target DIBL = 100 mV/V for nanoscale devices can be achieved for very steep S/D gradient ( $d \le 2 \text{ nm/dec}$ ) in GOI devices whereas a slightly higher value of d = 3 nm/dec can still achieve the same DIBL for SOI DG MOSFETs. A wider spacer of  $0.5L_g$  relaxes the constraint on S/D doping gradient for SOI and GOI devices. DG SOI devices should be designed with d < 4 nm/dec and 5 nm/dec for GOI and SOI devices respectively with  $s/L_g = 0.5$  to achieve DIBL of 100 mV/V. Underlap S/D design can be utilized to limit short channel effects in SOI/GOI devices and achieve reasonable values of S-slope and DIBL.

## III. CONCLUSIONS

A comprehensive analysis to limit short channel effects in single and double gate SOI/GOI MOSFETs, based on the ratio of effective channel length to natural length, has been presented. Results suggest that GOI based devices exhibit higher degree of short channel effects as compared to SOI based MOSFETs. Underlap channel design defined by spacer width, S/D doping gradient and lateral straggle offer additional degree of freedom apart from transistor structural parameters to design devices with immunity to short channel effects. Underlap channel design is particularly useful in suppressing short channel effects in GOI based devices with silicon films > 8 nm. DG SOI MOSFETs offer maximum flexibility in selecting silicon film thickness and lowest spacer width at a given S/D doping gradient when compared to single gate SOI MOSFETs and GOI based single/double gate MOSFETs. Reasonable values of S-slope and DIBL can be achieved in underlap channel GOI DG devices. Results presented in this work will be useful in design and optimization of nanoscale single and double gate SOI/GOI MOSFETs for low voltage applications.

## REFERENCES

- [1] International technology roadmap for semiconductor 2006 edition. Available from: (http://public.itrs.net).

- [2] F. Balestra, S. Cristoloveanu, M. Benachir, J. Birni and T. Elewa, "Double gate silicon-on-insulator transistor with volume inversion: a new device with greatly enhanced performance", *IEEE Electron Device Letters*, vol. 8, no. 10, pp. 410–412, 1987.

- [3] R. H. Yan, A. Ourmazd and K. F. Lee, "Scaling the Si MOSFET: from bulk to SOI to bulk", *IEEE Trans Electron Devices*, vol. 39, no. 7, pp. 1704–1710, 1992.

- [4] M. Ieong, E. Jones, T. Kanarsky, Z. Ren, O. Dokumaci, R. Roy, L. Shi, T. Furukawa, Y. Taur, R. Miller, and H.-S.P. Wong, "Experimental evaluation of carrier transport and device design for planar symmetric/asymmetric double-gate/ground-plane CMOSFETs," *IEDM Tech. Dig.*, pp. 441-444, 2001.

- [5] J.M. Hergenrother, D. Monroe, F.P. Klemens, A.

- Komblit, G.R. Weber, W.M. Mansfield, R. Baker, F.H. Baumann, K.J. Bolan, J.E. Bower, N.A. Ciampa, R.A. Cirelli, J.I. Colonell, D.J. Eaglesham, J. Frackoviak, H.J. Gossmann, M.L. Green, S.J. Hillenius, C.A. King, R.N. Kleiman, W.Y.C. Lai, J.T. Lee, C.R.C. Liu, H.L. Maynard, M.D. Morris, S. Oh, H.C. Pai, S.C.S. Rafferty, J.M. Rosamilia, T.W. Sorsch, and H.H. Vuong, "The Vertical Replacement Gate (VRG) MOSFET: A 50-nm vertical MOSFET with lithography independent gate length," *IEDM Tech. Dig.*, pp. 75-78, 1999.

- [6] B. Yu, H. Wang, A. Joshi, Q Xiang, E. Ibok, and M-R. Lin, "15nm gate length planar CMOS transistor," *IEDM Tech. Dig.*, pp. 937-940, 2001.

- [7] J. Kedzierski, P. Xuan, E.H. Anderson, J. Bokor, T.-J. King, and C. Hu, "Complementary silicide source/drain thin body MOSFETs for the 20 nm gate length regime," *IEDM Tech. Dig.*, pp. 57-60, 2000.

- [8] D. Hisamoto, T. Kaga, Y. Kawamoto, and E. Takeda, "A fully depleted lean-channel transistor (DELTA)—A novel vertical ultra thin SOI MOSFET," *IEDM Tech. Dig.*, pp. 833-836, 1989.

- [9] J. Kedzierski, D.M. Fried, E.J. Nowak, T. Kanarsky, J.H. Rankin, H. Hanafi, W. Natzle, D. Boyd, Y. Zhang, R.A. Roy, J. Newbury, C. Yu, Q. Yang, P. Saunders, C.P. Willets, A. Johnson, S.P. Cole, H.E. Young, N. Carpenter, D. Rakowski, B.A. Rainey, P.E. Cottrell, M. Ieong, and H.-S.P. Wong, "High-performance symmetric-gate and CMOS-compatible Vt asymmetric- gate FinFET devices," *IEDM Tech. Dig.*, pp. 437-440, 2001.

- [10] J. Kedzierski, M. Ieong, E. Nowak, T.S. Kanarski, Y. Zhang, R. Roy, D. Boyd, D. Fried and H.S.P. Wong, "Extension and source/drain design for high performance FinFET devices", *IEEE Trans. Electron Devices*, vol. 50, no. 4, pp. 952-958, 2003.

- [11] A. Dixit, A. Kottantharayil, N. Collaert, M. Goodwin, M. Jurczak and K De Meyer, "Analysis of the parasitic S/D resistance in multiple-gate FETs", *IEEE Trans. Electron Devices*, vol. 52, no. 2, pp. 1132-1140, 2005.

- [12] X. Wu, P. C. H. Chan and M. Chan, "Impacts of nonrectangular fin cross section on the electrical characteristics of FinFET", *IEEE Tran. Elec. Dev.*, vol. 52, no. 1, pp. 63-68, Jan. 2005

- [13] J.G. Fossum, M.M. Chowdhury, V.P. Trivedi, T.-J. King, Y.-K. Choi, J. An and B. Yu, "Physical insights on design and modeling of nanoscale

- FinFETs", IEDM Tech. Dig., pp. 679-682, 2003.

- [14] F. Boeuf, T. Skotnicki, S. Monfray, C. Julien, D. Dutartre, J. Martins, P. Mazoyer, R. Palla, B. Tavel, P. Ribot, E. Sondergard and A. Sanquer, "16 nm planar NMOSFET manufacturable within state-of-the-art CMOS process thanks to specific design and optimization", *IEDM Tech. Dig.*, pp. 637-640, 2001.

- [15] B. Yu, L. Chang, S. Ahmed, H. Wang, S. Bell, C.-Y. Yang, C. Tabery, C. Ho, Q. Xiang, T.-J. King, J. Bokor, C. Hu, M.-R. Lin and D. Kyser, "FinFET scaling to 10 nm gate length", *IEDM Tech. Dig.*, pp. 251-254, 2002.

- [16] E. Bernard, T. Ernst, B. Guillaumot, N. Vulliet, T.C. Lim, O. Rozeau, F. Danneville, P. Coronel, T. Skotnicki, S. Deleonibus and O. Faynot, "First internal spacers' introduction in record high I<sub>on</sub>/I<sub>off</sub> TiN/HfO<sub>2</sub> gate multichannel MOSFET satisfying both high-performance and low standby power requirements", *IEEE Electron Device Letters*, vol. 30, no. 2, pp. 148-151, 2009.

- [17] N. Miura, Y. Domae, T. Sakata, M. Watanabe, T. Okamura, T. Chiba, K. Fukuda and J. Ida, "Undoped thin film FD-SOI CMOS with source/drain-to-gate non-overlapped structure for ultra low leak applications", *IEEE SOI Conference*, pp. 176-177, 2005.

- [18] R. J. Luyken, T. Schultz, J. Hartwich, L. Dreeskornfeld, M. Stadele and L. Risch, "Design considerations for fully depleted SOI transistors in the 25–50 nm gate length regime", *Solid–State Electronics*, vol. 47, no, 7, pp. 1199–1203, 2003.

- [19] A. Kawamoto, S. Sato and Y. Omura, "Engineering S/D diffusion for sub-100-nm channel SOI MOSFETs", *IEEE Trans Electron Devices*, vol. 51, no. 6, pp. 907–913, 2004.

- [20] R. S. Shenoy and K. C. Saraswat, "Optimisation of extrinsic source/drain resistance in ultrathin body double-gate FETs", *IEEE Trans Nanotechnology*, vol. 2, no. 4, pp. 265–270, 2003.

- [21] T. C. Lim and G. A. Armstrong, "Parameter sensitivity for optimal design of 65 nm node double gate SOI transistors", *Solid–State Electronics*, vol. 49, no. 6, pp. 1034–1043, 2005.

- [22] A. Kranti and G. A. Armstrong, "Performance assessment of nanoscale double and triple gate FinFETs", Semiconductor Science and Technology, vol. 21, no. 4, pp. 409–421, 2006.

- [23] Rashmi, A. Kranti and G.A. Armstrong, "6-T SRAM cell design with nanoscale double gate SOI MOSFETs: impact of source/drain engineering and circuit topology", Semiconductor Science and Technology, vol. 23, no. 7, article 075049, 2008.

- [24] A. Kranti and G. A. Armstrong, "Engineering source/drain extension regions in nanoscale double gate (DG) SOI MOSFETs: Analytical model and design considerations", *Solid–State Electronics*, vol. 50, no. 3, pp. 437–447, 2006.

- [25] A. Kranti, Y. Hao and G.A. Armstrong, "Performance projections and design optimization of planar double gate SOI MOSFETs for logic technology applications", Semiconductor Science and Technology, vol. 23, no. 4, article 045001, 2008.

- [26] C.-W. Lee, D. Lederer, A. Afzalian, R. Yan, N. Dehdashti, W. Xiong and J.-P. Colinge, "Comparison of contact resistance between accumulation-mode and inversion-mode multigate FETs", *Solid-State Electronics*, vol. 52, no. 11, pp. 1815-1820, 2008.

- [27] A.B. Sachid, C.R. Manoj, D.K. Sharma, and V.R. Rao, "Gate fringe-induced barrier lowering in underlap FinFET structures and its optimization", *IEEE Electron Device Letters*, vol. 29, no. 1, pp. 128-130, 2008.

- [28] C.R. Manoj and V.R. Rao, "Impact of High-k Gate Dielectrics on the Device and Circuit Performance of Nanoscale FinFETs", *IEEE Electron Device Letters*, vol. 28, no. 4, pp. 295-287, 2007.

- [29] S. Sharma and P. Kumar, "Optimizing effective channel length to minimize short channel effects in sub-50 nm single/double gate SOI MOSFETs", *Journal of Semiconductor Technology and Science*, vol. 8, no. 2, pp. 170-177, 2008.

- [30] T.C. Lim and G.A. Armstrong, "Scaling issues for analogue circuits using double gate SOI transistors", *Solid–State Electronics*, vol. 51, no. 2, pp. 320-327, 2007.

- [31] A. Kranti and G.A. Armstrong, "High tolerance to gate misalignment in low voltage gate—underlap double gate MOSFETs", *IEEE Electron Device Letters*, vol. 29, no. 5, pp. 503-505, 2008.

- [32] A. Kranti and G.A. Armstrong, "Design and optimization of FinFETs for ultra-low-voltage analog applications", *IEEE Trans. Electron Devices*, vol. 54, no.12, pp. 3308-3316, 2007.

- [33] A. Kranti and G.A. Armstrong, "Source/Drain extension region engineering in FinFETs for low-

- voltage analog applications", *IEEE Electron Device Letters*, vol. 28, no. 2, pp. 139–141, 2007.

- [34] H. Shang, K.-L. Lee, P. Kozlowski, C. D'Emic, I. Babich, E. Siroski, M. Ieong, H.-S.P. Wong, and K. Guarini, "Self-aligned n-channel germanium MOSFETs with a thin Ge oxynitride gate dielectric and tungsten gate," *IEEE Electron Device Letters*, vol. 25, no. 3, pp. 135–137, 2004.

- [35] K. C. Saranswat, C. O. Chui, T. Krishnamohan, A. Nayfeh, and P. McIntyre, "Ge based high performance nanoscale MOSFETs," *Microelectronic Engineering*, vol. 80, no. 1, pp. 15–21, Jun. 2005.

- [36] H. Shang, M. M. Frank, E. P. Gusev, J. O. Chu, S. W. Bedell, K. W. Guarini, and M. Ieong, "Germanium channel MOSFETs: opportunities and challenges," IBMJ, Res. Develop., vol. 50, no. 4-5, pp. 377–386, 2006.

- [37] R. S. Johnson, H. Niimi, and G. Lucovsky, "New approach for the fabrication of device-quality Ge/GeO<sub>2</sub>/SiO<sub>2</sub> interfaces using low temperature remoted plasma processing," *J. Vac. Sci. Technol.*, vol. 18, no. 4, pp. 1230–1233, 2000.

- [38] N. Lu, W. Bai, A. Ramirez, C. Mouli, A. Ritenour, M. L. Lee, D. Antoniadis, and D. L. Kwong, "Ge diffusion in Ge metal oxide semiconductor with chemical vapor deposition HfO<sub>2</sub> dielectric," *Applied Physics Letters*, vol. 87, no. 5, pp. 51922–51924, 2005.

- [39] D. J. Hymes and J. J. Rosenberg, "Grow and materials characterization of native oxynitride thin films on germanium," *Journal of Electrochemical Society*, vol. 135, no. 4, pp. 961–965, 1988.

- [40] H. Shang, H. Okorn-Schimdt, J. Ott, P. Kozlowski, S. Steen, E. C. Jones, and H.-S. P. Wong, "Electrical characterization of germanium p-channel MOSFETs," *IEEE Electron Device Letters*, vol. 24, no. 4, pp. 242–244, 2003.

- [41] S. K. Mandal, S. Chakraborty, and C. K. Maiti, "Ge-channel p-MOSFETs with ZrO<sub>2</sub> gate dielectrics," *Microelectronic Engineering*, vol. 81, no. 2–4, pp. 206–211, 2005.

- [42] W. Bai, N. Lu, A. P. Ritenour, M. L. Lee, D. A. Antoniadis, and D.-L. Kwong, "The electrical properties of HfO<sub>2</sub> dielectric on germanium and the substrate doping effect," *IEEE Trans. Electron Devices*, vol. 53, no. 10, pp. 2551–2558, 2006.

- [43] C. O. Chui, H. Kim, D. Chi, B. Triplett, P. C. McIntyre, and K. C. Saraswat, "A sub-400 °C germanium MOSFET technology with high-k dielectric and metal gate," *IEDM Tech. Dig.*, pp. 437–440, 2002.

- [44] H. Shang, H. Okorn-Schmidt, K. K. Chan, M. Copel, J. A. Ott, P. M. Kozlowski, S. E. Steen, S. A. Cordes, H.-S. P. Wong, E. C. Jones, and W. E. Haensch, "High mobility p-channel germanium MOSFETs with a thin Ge oxynitride gate dielectric," *IEDM Tech. Dig.*, pp. 441–444, 2002.

- [45] K. K. Young, "Short channel effects in fully depleted SOI MOSFETs", *IEEE Trans. Electron Devices*, vol. 36, no. 2, pp. 399–401, 1989.

- [46] K. Suzuki, T. Tanaka, Y. Tosaka, H. Horie and Y. Arimoto, "Scaling theory for double-gate SOI MOSFETs", *IEEE Trans Electron Devices*, vol. 40, no. 12, pp. 2326–2329, 1993.

- [47] Y. Tosaka, K. Suzuki and T. Sugii, "Scaling Parameter Dependent Model for Subthreshold Swing (S) in Double-Gate SO1 MOSFET's", *IEEE Electron Device Letters*, vol. 15, no. 11, pp. 466–468, 1994.

- [48] X. Liang and Y. Taur, "A 2-D Analytical Solution for SCEs in DG MOSFETs", *IEEE Trans Electron Devices*, vol. 51, no. 8, pp. 1385–1391, 2004.

- [49] J.–S. Park, S.–Y. Lee, H. Shin and R. W. Dutton, "Analytical analysis of short-channel effects in MOSFETs for sub-100 nm technology", *Electronics Letters*, vol. 38, no. 20, 1222-1223, 2002.

- [50] D. J. Frank, Y. Taur and H. S. P. Wong, "Generalized scale length for two dimensional effects in MOSFETs", *IEEE Electron Device Letters*, vol. 19, no. 9, vol. 385–387, 1998.

- [51] K. Suzuki and T. Sugii, "Analytical Models for n<sup>+</sup>-p<sup>+</sup> double-gate SO1 MOSFET's", *IEEE Trans Electron Devices*, vol. 42, no. 11, pp. 1940-1948, 1385–1391, 1995.

- [52] K. Suzuki, Y. Tosaka and T. Sugii, "Analytical threshold voltage model for short channel n+-p+ double gate SOI MOSFET's", *IEEE Trans Electron Devices*, vol. 43, no. 5, pp. 732-738, 1996.

- [53] K. Suzuki, Y. Tosaka and T. Sugii, "Analytical threshold voltage model for short channel double gate SOI MOSFET's", *IEEE Trans Electron Devices*, vol. 43, no. 7, pp. 1166-1168, 1996.

- [54] Q. Chen, B. Agrawal and J.D. Meindl, "A comprehensive analytical subthreshold swing (S) Model for double-gate MOSFETs", *IEEE Trans Electron Devices*, vol. 49, no. 6, pp. 1086-1090, 2002.

- [55] A. Kranti and G. A. Armstrong, "Optimization of the source/drain extension region profile for suppression of short channel effects in sub-50 nm

- DG MOSFETs with high- $\kappa$  gate dielectrics", Semiconductor Science and Technology, vol. 21, no. 12, pp. 1563-1572., 2006.

- [56] Q. Chen, E. M. Harrell, II and J. D. Meindl, "A Physical Short-Channel Threshold Voltage Model for Undoped Symmetric Double-Gate MOSFETs", *IEEE Trans Electron Devices*, vol. 50, no. 7, pp. 1631-1637, 2003.

- [57] D. Munteanu, J. L. Autran and S. Harrison, "Quantum short-channel compact model for the threshold voltage in double-gate MOSFETs with high-permittivity gate dielectrics", *Journal of Non-Crystalline Solids*, vol. 351, no. 21-23, pp.1911– 1918, 2005.

Sudhansh Sharma, born in Delhi in 1974, received the Bachelors of Science (Honours) and Master of Science degrees in Physics in 1995 and 1998, respectively from University of Delhi, Delhi and Master of Technology in Computer Science in

2003 from The Institute of Electronics Telecommunication Engineers, Delhi, India. From 1998 to 2005 he worked as Senior Analyst at Shri Ram Institute for Industrial Research, Delhi, India, where he developed calibration and testing facilities for various electrical and electronic components. From 2005 to 2006, he worked as Lecturer in the Computer Science Department of Shyam Lal College, University of Delhi, India. From 2006 to 2008 he served as Lecturer in the School of Computers and Information Sciences (SOCIS), Indira Gandhi National Open University (IGNOU), Delhi where he developed and coordinated computer science programs for distance education. From April 2008 to January 2009, he served as an Assistant Professor in the Department of Information Technology of Institute of Management Studies-Noida, India, and contributed to the academic and research oriented works performed there. Currently he is serving the Vishvesh-warya School of Business Management, as an Assistant Professor in the Department of Information Technology and Systems Sciences. He is also working towards Ph.D. degree from Chaudhary Charan Singh (CCS) University, Meerut, India. His research interests include MOS device physics, quantum effects in MOSFETs and simulation of nanoscale MOS device architectures for logic and analog applications.

Pawan Kumar received the Bachelors of Science (B.Sc.) and Master of Science (M.Sc.) degrees in Physics from University of Delhi and Ph.D. in Physics from Indian Institute of Technology, Delhi, India.

Dr. Kumar served in academics at various positions for about 40 years in the Physics Department, M.M.H. College, Ghaziabad, Uttar Pradesh, India. Currently, Dr. Kumar is a resource person to the Department of Science and Technology (D.S.T.), Government of India, New Delhi. His research interests include semiconductor device physics, quantum electronics, micro/nano electronics and bio-mechanics. In these topics, Dr. Kumar has authored/coauthored about 50 research papers in various journals/conferences.