논문 2011-48SD-6-4

# 적응형 사구간제어기법을 이용한 DC-DC 벅 변환기

# (DC-DC Buck converter Using an Adjustable Dead-time Control Method)

임 동 균\*. 유 태 경\*. 이 건\*. 윤 광 섭\*\*

(Dong-Kuyn Lim, Tai-Kyung Yoo, Gun Lee, and Kwang-Sub Yoon)

요 의

본 논문에서는 휴대기기를 위한 고효율 전류구동방식의 DC-DC 벅 변환기를 제안한다. 제안된 전류구동방식의 DC-DC 컨 버터는 파워스위치의 전도손실을 최소화하는 적응형 사구간 제어기법을 적용하여 부하전류에 따라 효율을 2~5%이상 향상시킨다. 설계된 DC-DC 벅 변환기는  $0.35\mu$ m CMOS공정을 이용하여 칩으로 제작 되었으며, 전체 칩의 크기는 0.97mm²이다. 제작된칩의 입력전압범위는  $2.5V\sim3.3V$ 이고, 출력전압은 1.8V이며 리플전압은 10mV이하로 나타내고 있다. 최대 500mA의 부하 전류에서 구동할 수 있도록 설계 하였고, 200mA에서 최대 93%의 전력효율을 나타내고 있다.)

#### Abstract

This paper proposes high efficiency current-mode DC-DC buck converter that are suitable for portable devices. The current-mode DC-DC buck converter using adjustable Dead-time control method improves the power efficiency  $2\sim5\%$ . The buck converter has been implemented with a standard 0.35um CMOS process. The size of this chip is 0.97mm2. The input range of the fabricated DC-DC buck converter is  $2.5V\sim3.3V$ , and the output is 1.8V. The maximum loading current of the converter is 500mA and the peak efficiency is 93% at 200mA loads.

Keywords: Buck, Dead-time, DC-DC converter, soft start, power management

#### I. 서 론

최근 휴대전화, PDA, 노트북등과 같은 휴대용 멀티미디어 기기 시장의 발달로 인해 파워 매니지먼트 시스템의 중요성이 증가하고 있다. 이러한 휴대용 멀티미디어 기기들은 배터리 전원으로부터 다양한 내부 시스템의 전원 전압을 공급 받아야 한다. 그러므로 배터리 전압을 내부 시스템 전원 전압으로 전력 변환을 하는 회로에 있어서 전력 변환 효율은 휴대장치의 사용시간을 보장을 위하여 매우 중요한 성능으로 부각되고 있다.

따라서 이를 구현하기 위한 다양한 파워 매니지먼트 회로의 개발이 급속하게 증가학고 있다. 파워 매니지먼트 회로는 일반적으로 전하 펌프 회로, 리니어 레귤레이터 (Linear Regulator) 회로, 스위칭 DC-DC 변환기 등으로 구현할 수 있다<sup>[1]</sup>. 스위칭 DC-DC 변환기는 전력효율이 높으며, 인덕터를 사용함으로 입력전압보다 높은 전압과 낮은 전압을 모두 구현할 수 있다. 또한 대용량부하전류를 구동할 수 있기 때문에 휴대장치에서 파워매니지먼트회로에 널리 이용되고 있다. 스위칭 DC-DC 변환기의 손실원인으로는 크게 전도손실, 스위칭손실, 구동회로손실과 같이 3가지로 나눌 수 있다. 이 3가지손실중에서 전도손실이 가장 큰 손실원인으로 나타난다. 전도손실에는 파워스위치에 생성되는 도통저항에의한 손실과 게이트-구동손실(gate drive loss), 타이밍손실(timing loss) 및 L-C 필터의 기생손실로 나타나게

접수일자: 2010년1월11일, 수정완료일: 2011년5월30일

<sup>\*</sup> 학생회원, \*\* 평생회원, 인하대학교 전자공학과

<sup>(</sup>Dept. of Electronic Engineering, Inha University) ※ "본 연구는 지식경제부 및 정보통신산업진흥원의 대학 IT연구센터 지원사업의 연구결과로 수행되었 음"(NIPA-2011-C1090-1111-0007)

된다<sup>[2]</sup>. 본 논문에서는 파워스위치의 손실의 문제점<sup>[3~4]</sup>을 해결하기 위해서 적응형 사구간 제어기법(Adaptive Dead-Time Control)을 제안하였다. 본 논문의 구성은 Ⅱ 장에서 제안된 DC-DC 벅 변환기의 구조 및 동작원리와 적응형 사구간 제어기법 및 구성회로에 대해서 설명하였고, Ⅲ장에서 제작된 칩의 측정결과에 대해서 논하며, Ⅳ장에서는 결론을 맺는다.

### Ⅱ. 제안한 고효율 전류방식 DC-DC 벅 변환기

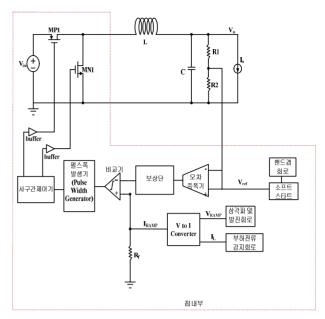

본 논문에서 제안한 전류 구동방식의 DC-DC 벅 변 환기의 구조는 그림 1과 같다. 전류구동방식의 벅 변환 기의 기능은 인덕터 전류파형을 이용하여 입력 전압보 다 낮은 출력 전압으로 변환하는 것이다. DC-DC 변환 기는 전원부와 내부 피드백 제어회로 및 외장 LC필터 로 구성되어 있다. Vin은 입력 DC 전압을 공급하는 배 터리 전원이고, Vo는 입력 DC 전압을 변환시킨 출력 DC 전압이다. L, C는 모두 큰 용량 값을 가지고 있기 때문에 외부소자로 구성된다. 저항 R1과 R2는 출력 전 압을 감지하여서 오차증폭기의 출력전압 크기를 결정한 다. 부하전류 Io는 임의의 디지털 또는 아날로그 시스템 에서 필요한 전류를 나타낸다. 전류감지회로에서 나타 난 신호는 삼각파 신호 발생기와 합쳐져서 발진현상을 막을 수 있다. 이때의 신호와 오차증폭기 출력에서 결 정된 출력값을 비교하여 펄스를 생성한다. 또한 펄스 폭 발생기(Pulse Width Generator or Modulator)를 통 하여 파워스위치 MP1에 적합한 듀티비율과 타이밍을 결정하게 된다. 파워스위치 MP1이 켜지면 출력 전압이 상승하게 되고 저항 R1과 R2를 사용하여 감지된 출력 전압이 기준전압(Vref)과 같지 않으면 오차증폭기에 의 하여 제어신호가 변하게 되고 이로 인해 듀티비율이 변 하게 된다. 따라서 피드백 제어회로를 통하여 발생하는 PWM(Pulse Width Modulation)신호에 의하여 파워스 위치 MP1. MN1의 동작이 제어되어 원하는 출력전압을 생성하게 된다<sup>[5]</sup>.

제안한 DC-DC 벅 변환기는 시스템의 안정도를 위하여 입력전압이 들어오면 소프트 스타트회로가 동작하여 과도 전류에 의한 충격으로부터 변환기를 보호하게 된다.

스위칭 DC-DC 변환기는 인덕터와 스위칭작용에 의해 동작하는 비선형 회로이다. 이러한 회로의 피드백루프의 안정성을 분석하기 위해서는 선형화된 소신호

그림 1. 제안한 고효율 DC-DC 벅 변환기의 블록도

Fig. 1. Block diagram of the proposed DC-DC buck converter with high efficiency.

모델이 필요하다. 일반적인 전압 방식의 DC-DC 벅 변환기는 두 개의 극점을 가지며 일반적으로 다음과 같이 2차식으로 모델링 할 수 있다<sup>[6~7]</sup>.

$$G_{vd}(s) = \frac{V}{D} \cdot \frac{1}{(1 + (\frac{L}{R}) \cdot s + LC \cdot s^2)}$$

(1)

식 (1)은 입력대 출력을 s의 관한 전달함수 Gvd를 나 타낸다. 여기서 D는 PWM 파형의 듀티비율을 의미한 다. 전압 방식 DC-DC 벅 변환기는 극점이 두 개 존재 하기 때문에 이득과 위상여유에 대한 확보가 어렵다. 전압 방식 DC-DC 벅 변환기는 보상하기 위해서 비교 구조가 복잡한 PID(Proportional Derivative) 보상기를 사용한다. 전류구동방식 DC-DC 벅 변환기도 전압구동방식과 마찬가지로 두 개의 극점 을 갖는다. 그러나 전류구동방식 벅 변환기의 두 번째 극점은 전압방식의 벅 변환기와는 다르게 첫 번째 극점 에서 멀리 떨어진 스위칭 주파수 근처에 위치하므로 전 체 변환기의 안정성에 영향을 주지 않는다. 그러므로 하나의 극점을 갖는 1차 모델로 정확한 모델을 근사하 여 사용할 수 있다. 변환기의 안정성을 위해서 보상 계 수 값을 결정할 경우 컴퓨터를 이용하여 정확한 모델을 분석하게 된다. 그러나 이론적인 분석을 위해서는 복잡 한 모델보다는 단순화된 모델을 사용한다. 식 (2)는 1차 모델의 전달함수 Gvc를 보여준다.

$$G_{vc} = \frac{V_{out}(s)}{I_{c}(s)} = \frac{1}{(1+s \cdot RC)}$$

(2)

식 (2)에서와 같이 전류구동방식 변환기의 경우 소신호 전달함수  $G_{vc}(S)$ 에서 극점의 수가 전압구동방식에 비하여 하나 적기 때문에 위상에 대한 보상이 없어도 적절한 위상여유확보가 가능하다. 그러므로 전류구동방식 DC-DC 변환기에서는 구조가 비교적 간단한 PI(Proportional plus Integral) 보상기가 사용 될 수 있다<sup>[2]</sup>.

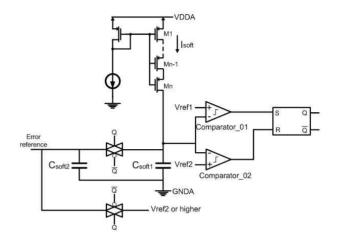

소프트 스타트 회로(soft start circuit)는 스텝다운 DC-DC 변환기 시동시의 급격한 귀환 전압상승으로 인한 과전류 발생 및 인덕터가 포화되는 현상을 방지한다. 소프트 스타트 회로는 변환기에 입력전압이 들어올 때보상단의 기준전압을 완만하게 상승하도록 한다<sup>[8]</sup>. 따라서 완만히 상승하는 기준전압을 따라 출력전압도 완만한 상승을 하게 된다. 소프트 스타트 전압은 기준전압까지 완만하게 증가할수록 안전한 시동을 보장한다. 완만한 증가를 위하여 삼각파 충전에 필요한 커패시터 용량을 증가시키거나 바이어스 전류 값을 감소시킨다.

설계된 소프트 스타트 회로도는 그림 2와 같다. 완만한 지연시간 경과 후, 출력전압이 정상화되면 오차보상회로로 입력되는 삼각파 전압 대신 기준전압으로 전환한다. 전환 순간의 전하 유입이나 외란으로부터의 안정성 확보를 위하여, 스위치 전후에 커패시터 Csoft1,2를배치하였다. 본 논문에서는 1pF의 커패시터로 긴 충전시간을 갖기 위해서, 10nA의 전류원(Isoft)을 구현하였다. 선형동작 영역으로 바이어스된 PMOS를 직렬 구성하여<sup>(9)</sup>, 높은 저항 값을 구현하고 낮은 출력 전류를 구현하였다. 소프트 스타트 지연시간(Tsoft)은 식 (3)과같이 표현할 수 있다<sup>(10)</sup>.

$$T_{soft} = V_{ref2} \frac{C_{soft1}}{I_{soft}} \tag{3}$$

여기서 Vref2는 기준전압을 의미한다.

본 논문은 고효율을 달성하기 위한 사구간 제어기법을 제안한다. DC-DC 변환기의 손실의 종류는 크게 3가지로 나눌 수 있다. 첫째 전도손실(conduction loss), 둘째 스위칭손실(switching loss), 구동회로의 전력 손실(control circuit loss)이 그것이다. 그 중 전도손실은 DC-DC 변환기에서 가장 큰 손실요인으로 작용한다. 실제 DC-DC 변환기를 구현하기 위해서는 이상적인 소

그림 2. 온-칩 소프트 스타트 회로도 Fig. 2. On-chip soft start circuit.

자가 아닌 비이상적인 소자를 사용하게 된다. 그 결과 전류의 흐름은 스위치역할을 하는 파워트랜지스터와 에 너지를 저장하고 전달하는 L-C 필터를 통하여 부하로 흐르게 된다. 따라서 각각의 소자에 전력 손실이 있게 된다. 이와 같이 여러 소자에서 생기는 기생저항 및 트 랜지스터의 온 저항 값에 따라서 손실요인은 게이트-구 동손실(gate Drive loss), 타이밍 손실(Timing loss) 및 L-C 필터의 기생손실 3가지로 다시 분류된다. 이 중 게 이트 구동손실과 타이밍손실은 사구간 제어기법을 통하 여 제어가 가능하다. DC-DC 벅 변환기의 두 개 파워스 위치(NMOS와 PMOS)는 상보적으로 동작하는데, PMOS 파워스위치가 켜지면 NMOS 파워스위치가 꺼 지고. NMOS 스위치가 켜지면 PMOS 스위치가 켜지는 형태를 갖는다. 그러나 파워스위치는 작은 내부저항을 (Rds.on)을 갖기 위해 채널폭의 크기가 수만µm가 된다. 따라서 파워스위치에 기생적으로 생성되는 커패시턴스 가 커지므로 스위치가 각각 On/OFF되는 시간이 지연 되는 단점을 갖게 된다. 반면에 두 개의 파워스위치는 순간적으로 동시에 단락이 되면서 매우 큰 전력손실을 가져올 뿐 아니라 파워트랜지스터의 피로누적 영향을

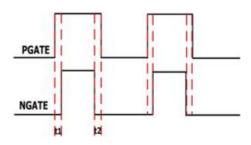

그림 3. DC-DC 변환기에 필요한 사구간 Fig. 3. The dead-time for the DC-DC converter.

끼치게 된다. 따라서 그림 3과 같은 사구간(dead-time), t1과 t2시간이 필요하게 된다. t1과 t2는 각각 상승지연시간과 하강지연시간을 나타낸다.

그러나 사구간이 너무 길면, 인덕터에 흐르는 전류가 NMOS 파워스위치의 바디다이오드로 흐르게 되며, 바디 다이오드에 순방향 전류가 흐르면 전력손실이 발생된다. 따라서 적절한 사구간제어가 필요하게 된다.

사구간 비율(t1/t2)은 파워스위치의 사이즈, 입력전압, 부하전류 및 기생커패시터와의 상관관계인 식 (4), (5) 에 의해서 결정된다.

$$\frac{t1}{t2} = \frac{(\Delta I)/2 + I_o}{(\Delta I)/2 - I_o} \tag{4}$$

$$C_x = \frac{t1(\Delta I/2 - I_o)}{V_{in}} \tag{5}$$

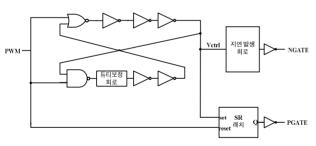

식(4), (5)에서 알 수 있듯이 사구간은 부하전류(Io)에 따라 가변되어야 하므로 기존에 사용되던 고정시간을 갖는 사구간제어기는 효율향상에 많은 도움이 되지 못한다. 또한 t1과 t2구간을 동일하게 제어가 되지 않아효율에 영향을 미치는 문제점을 가지고 있었다<sup>[3, 11]</sup>. 제안한 적응형 사구간제어기는 그림 4와 같다. 제안회로

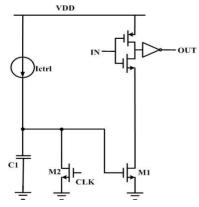

그림 4. 적응형 사구간제어기

Fig. 4. Adjustable dead-time controller.

그림 5. 듀티보정회로도

Fig. 5. Circuit schematic of Duty Correction Circuit.

는 논리회로를 이용한 비중첩 클럭신호 발생기와 듀티 보정회로, 지연발생회로, SR 래치회로로 구성된다. 입력 으로 들어오는 PWM신호는 듀티보정회로에서 하강지 연시간이 제어된 후 지연발생회로에서 상승지연시간을 발생시켜 NMOS의 입력신호를 만들게 된다. 지연발생 회로와 SR 래치회로는 파워스위치 신호의 지연시간조 정을 위해서 사용되었다. 그림 4 회로내 듀티보정회로 도와 지연발생회로도는 각각 그림 5와 그림 6과 같다.

그림 5와 그림 6에 사용되는 전류원  $I_{ctrl}$ 은 전류감지회로에서 감지된 신호를 이용하여 부하전류 변화에 따라 사구간이 바뀔 수 있도록 하였다<sup>[12]</sup>. 듀티 보정회로에서 전류원  $I_{ctrl}$ 이 커패시터 C1을 충전한다. C1에 충전된 전압이 트랜지스터 M1의 문턱전압  $v_{tnl}$ 과 같은 전압이 되도록 충전을 한다. 트랜지스터 M1이 도통되면 입력신호는 Vdd에서 Gnd로 천이 된다. M2는 커패시터 C1에 저장된 전하를 방전시키기 위하여 사용된다. 이때 사용되는 CLK는 그림 1에서 나타나 있는 삼각과 및 발진회로에서 발생되는 신호를 이용하여 DC-DC 벅 변환기의 동작주파수에 동기를 맞출 수 있다. 하강지연시간 t2는 식 (6)과 같다.

$$t2 = \frac{C1 \cdot V_{th1}}{I_{otrl}} \tag{6}$$

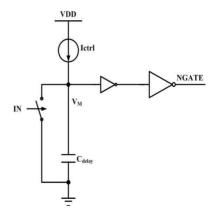

그림 6의 지연발생회로는 커페시터  $C_{delay}$ 가 인버터의 논리 문턱전압(Logic Threshold Voltage), $V_M$ 까지 충전되는 시간만큼 상승구간을 지연시킨다. 이때 상승지연시간 t1은 4 (7)로 구할 수 있다.

$$t1 = \frac{C_{delay} \cdot V_M}{I_{ctrl}} \tag{7}$$

그림 6. 지연 발생회로도

Fig. 6. Delay Generator Circuit.

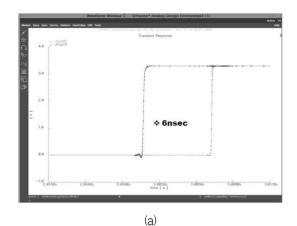

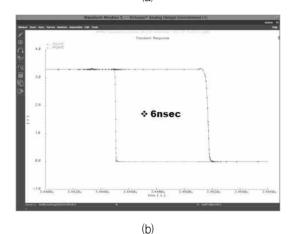

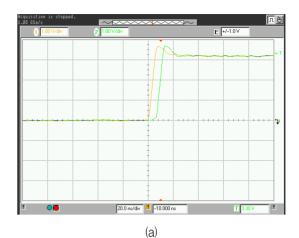

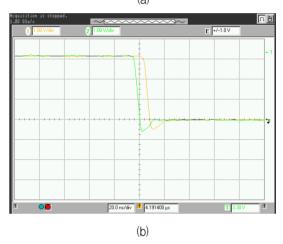

그림 7 사구간제어기의 (a) 상승지연시간(t1)과 (b) 하강 지연시간((t2)의 모의실험 결과

Fig. 7. Simulation results on (a) rising delay time and (b) falling delay time of the Adjustable dead-time controller.

$$t1=t2, \ C1 \bullet \ V_{th1}=C_{delay} \bullet \ V_{M} \eqno(8)$$

식 (6)과 식(7)은 동일하지 않다. 따라서 상승지연시간 t1과 하강지연시간 t2를 동일해야하므로 식 (6)과 식(7)을 이용하여 t1과 t2의 시간을 같도록 식 (8)을 나타낼 수 있다. 식 (8)은 전류원 I<sub>ctrl</sub>에 독립적인 값을 가지므로 전류원이 변하더라도 지연시간에는 영향을 주지않는다. 사구간제어기의 모의실험 결과를 그림 7에서나타내고 있다. 상승지연구간과 하강지연구간이 동일한 6ns으로 제어 되는 것을 볼 수 있다.

#### Ⅲ. 실험 및 고찰

본 논문의 적응형 사구간 제어기법을 이용한 고효율 DC-DC 벅 변환기는 0.35µm CMOS공정을 이용하여 설 계 및 제작되었다. 입력 범위는 2.5V~3.3V이며, 출력은

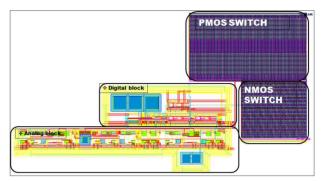

그림 8. 제안된 DC-DC 벅 변환기의 레이아웃

Fig. 8. Layout of the proposed DC-DC Buck converter.

표 1. 회로 설계 사양 요약

Table 1. Summary of design specification.

| 파라미터           | 사양          |  |  |

|----------------|-------------|--|--|

| 입력전압           | 2.5V~3.3V   |  |  |

| 출력전압           | 1.8V        |  |  |

| 스위칭 주파수        | 500[kHz]    |  |  |

| 부하전류           | 100mA~500mA |  |  |

| 최대효율           | 93%         |  |  |

| 인덕터(L)/커패시터(C) | 10uH/10uF   |  |  |

1.8V로 고정된다. 설계된 DC-DC 변환기의 레이아웃 사진은 그림 8과 같으며,, 코어사이즈는 1.15\*0.85mm<sup>2</sup>이 다. PMOS, NMOS 스위치는 250mΩ의 Ron저항을 가 지도록 설계하였다. 각각의 회로 설계 사양 및 외부소 자 값들은 표 1을 통하여 요약하였다.

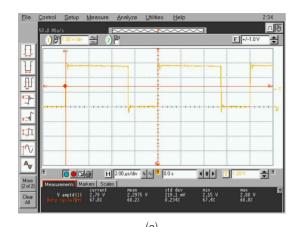

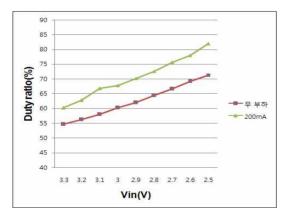

제안한 DC-DC 벅 변환기가의 입력전압을 가변시켜서 듀티비율을 측정하였다. 부하전류가 200mA일 경우입력전압을 3.3V와 2.5V로 인가했을 때 듀티 비율을 비교해보면 듀티 비율은 입력이 3.3V일 때 67.8%와 2.5V일 경우 86.1%로 각각 그림 9의 (a)와 (b)와 같이 측정되었다.

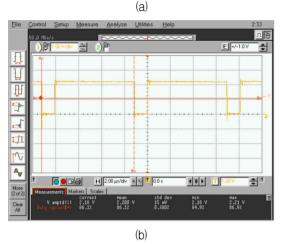

부하가 20mA인 경우와 무부하일 때 변환기의 듀티비율을 측정하였으며, 측정결과는 그림 10과 같다. 즉, 부하 200mA인 경우의 듀티 비율이 무부하인 경우보다 5%에서 10% 증가하는 것으로 측정되었다.

사구간제어기의 상승지연시간과 하강지연시간은 그림 11의 (a), (b)와 같이 각각 8ns와 10ns로 측정되어서, 사구간제어기의 기능 유효성을 확인할 수 있었다.

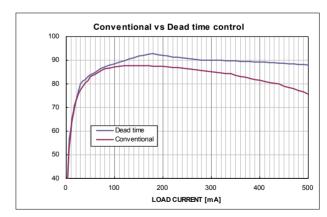

제안된 벅 변환기 동작 구간의 효율을 측정하여서 기존 벅 변환기의 효율과의 차이를 그림 12에서 나타내었다. 제안된 벅 변환기의 최대효율은 200mA에서 93%로나타나고 있고, 동작전압 범위에 따라서 최대 2~5%이

그림 9. 부하전류 200mA이며 입력전압이 (a) 3.3V (b) 2.5V 인 경우 파워스위치의 측정된 출력파형

Fig. 9. Power switch output when load current is 200mA.

그림 10. 200mA와 무 부하 시의 듀티 비율 비교 Fig. 10. Comparison of duty ratio between 200mA load current and no load current.

상의 효율향상을 나타내고 있다. 기존논문에서 발표된 회로 성능과의 비교는 표 2에 나타내었다. 기존 논문에 서 발표된 전력효율과 비교하면 다소 높거나 유사한 것 으로 나타났다. 또한 제안된 변환기의 스위칭주파수는

그림 11. 사구간제어기의 (a)상승지연시간과 (b)하강지연 시간 측정 파형

Fig. 11. The measured waveform of (a) the rising delay time and (b) the falling delay time of the dead time control circuit.

그림 12. 사구간제어기법을 이용한 DC-DC 벅 변환기 효율

Fig. 12. Efficiency of the DC-DC Buck converter using dead-time control method.

기존 변환기에 비해 유사하거나 낮으며, 인덕터 용량은 유사하거나 다소 큰 값을 사용했으며, 이로 인하여 리

- 표 2. 제안한 DC-DC 벅 변환기와 국제 학술 논문과 의 비교

- Table 2. Comparison of performance between the proposed DC-DC Buck converter and international science paper DC-DC converter.

| No.  | 입력전압 | 출력전압 | 스위칭       | 효율     | L/C    | 리플전압         |

|------|------|------|-----------|--------|--------|--------------|

| [3]  | [V]  | [V]  | 주파수       | 89.5 % | L/C    | 디글신입<br>20mV |

|      | 3.6  | 1    | 300KHz    |        | 4.7uH/ |              |

| [0]  | 5.0  | 1    | 5001112   | 94%    | 10uF   | 3mV          |

| [8]  | 6    | 3    | 1.1MHz    |        | 4.7uH/ |              |

| [O]  | U    | J    | 1.1101112 | 92 %   | 10uF   | 12mV         |

| [9]  | 4    | 1.5  | 500KHz    |        | 6uH/   |              |

| [10] | 1.8  | 3.3  | 500KHz    | 90 %   | 10uF   | 20mV         |

|      |      |      |           |        | 1uH/   |              |

| [10] | 1.0  | 0.0  | 5001112   |        | 3uF    | 20mV         |

| [12] | 5    | 1    | 600kHz    |        | 10uH/  |              |

| [14] |      |      | 000K11Z   |        | 10uF   |              |

| this |      |      | 500KH     |        | 10uH/  |              |

| work | 3.3  | 1.8  | z         | 93 %   | 10uF   | 10m V        |

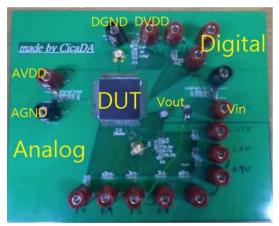

그림 13. 벅변환기 성능 측정용 보드 사진

Fig. 13. The picture of the evaluation board for the proposed buck converter.

플전압을 다소 감소한 것을 확인 할 수 있다. 그림 13은 측정용 보드사진을 나타낸다. 제안된 벅변환기가 탑재된 칩(DUT)와 주변 회로와 테스트를 위한 단자들을 볼수 있다.

#### Ⅳ. 결 론

본 논문에서는 휴대장치 시스템의 전력구동과 효율 향상을 위한 적응형 사구간제어기법을 이용한 고효율 DC-DC 벅 변환기를 제안하였다. 제안된 회로는 부하 전류에 따른 사구간을 제어함으로서 효율을 향상시켰 다. 또한 안정적인 동작을 위하여 소프트 스타트회로를 탑재하여 DC-DC 벅 변환기의 안정성을 향상시켰다. 제작된 전류방식의 DC-DC 벅 변환기는 0.35 µm CMOS 공정으로 제작되었으며, 전체 칩 면적은 1.15\*0.85 mm²이다. 입력전압 범위는 2.5 V에서 3.3 V이며, 출력전압은 1.8 V이다. 최대효율은 200 mA에서 93%이고, 최대부하전류는 500 mA 까지 동작할 수 있다.

## 감사의 글

반도체설계교육센터(IDEC)의 CAD Tool 지원에 감사드립니다. 본 논문은 인하대학교의 지원에 의하여 연구되었습니다.

#### 참 고 문 헌

- [1] C. Y. Leung, P. K. T. Mok, K. N. Leung, and M. Chan, "An integrated CMOS current-sensing circuit for low-voltage current-mode buck regulator", IEEE Trans. Circuits Syst. II, vol. 52, no. 7, pp. 394394, jul. 2005.

- [2] 허동훈, 노정진, "휴대용 멀티미디어 기기를 위한 400mA 전류방식 DC-DC 컨버터," 전자공학회 논 문지, 제45권 SD편, 제8호, 790-797쪽, 2008년 8월.

- [3] A. Sstratakos, S. Sanders, and R. Brodersen, "A Low voltage CMOS DC-DC converter for a portable Battery-Operated System", *IEEE power Electronics Special Conference.*, pp. 619-626, 1994

- [4] C. F. Lee and P. K. T. Mok, "A Monolithic current-Mode CMOS DC-DC Converter With On-Chip Current-Sensing Technique," *IEEE Journal of Solid-State Circuits*, vol. 39. No. 1, pp. 3 14, Jan. 2004.

- [5] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, second edition, Kluwer Academic Publishers, 2001

- [6] A. I. Pressman, Switching Power Supply Design, second edition, McGraw-Hill Companies, Inc., 1998

- [7] M. Brown, *Pratical Switching Power Supply Design.* San Diego, CA: Academic, 1990.

- [8] W. R. Liou, M. L. Yen and Y. L. Kuo "A High Efficiency Dual-Mode Buck Converter IC For portable Applications," *IEEE Transactions on* power electronics, vol. 22, pp. 1836–1846, Sep. 2007.

- [9] J. Xiao, A. V. Peterchev, I. Zhang and S. R. Sanders, "A 4- $\mu$ A Quiescent-Current Dual-Mode

- Digitally Controlled Buck Converter IC for Cellular Phone Applications," *IEEE Journal of Solid-State Circuits*, vol. 39, No. 12, pp. 288 289, Dec. 2004.

- [10] 박승찬, 임동균, 윤광섭 "온칩 시동회로를 갖는 CMOS DC-DC 벅 변환기 설계," 한국통신학회 논 문지, 제 34권, 제7호, 568-573쪽, 2009년 7월.

- [11] A. J. stratakos and R. W. Brodersen, High Efficiency Low-Voltage DC-DC Conversion for Portable Application, University of california, Berkeley.

- [12] C. Y. Leung and P. K. T. Mok, "An Integrated CMOS Current-Sensing Circuit for Low-Voltage Current-Mode Buck Regulator," *IEEE Transactions on circuit and systems*, 2005, Vol.52, pp 394 -397, Jul, 2005.

- [13] P. E. Allen and D. R. Holberg, *CMOS Analog Circuit Design* second edition, Oxford University Press, 2002.

- [14] P. E. Allen and D. R. Holberg, *CMOS Analog Circuit Design* second edition, Oxford University Press, 2002.

- [15] C. F. Lee and P. K. T. Mok, "A Monolithic current-Mode CMOS DC-DC Converter With On-Chip Current-Sensing Technique," *IEEE Journal of Solid-State Circuits*, vol. 39. No. 1, pp. 3 14, Jan. 2004.

- [16] F. F. Ma, W. Z. Chen, and J. C. Wu, "A monolithic current Mode buck converter with advanced control and protection circuit," *IEEE Transactions on power electronics*, vol. 22, pp. 1836–1846, Sep. 2007.

#### - 저 자 소 개

임 동 균(학생회원)

2008년 인하대학교 전자공학과 학사 졸업

2010년 인하대학교 전자공학과 석사 졸업

2010년~현재 실리콘 웍스

<주관심분야 : 아날로그 VLSI설계, DC-DC converter 설계>

유 태 경(학생회원)

2008년 단국대학교 전자공학과

학사 졸업

2010년~현재 인하대학교

전자공학과 석사과정

<주관심분야: 아날로그 VLSI설계, DC-DC converter 설계>

이 건(학생회원)

2011년 인하대학교 전자공학학사 졸업.

2011년~인하대학교 전자공학 석사과정

<주관심분야: 아날로그 VLSI설 계, DC-DC converter 설계>

윤 광 섭(평생회원) 1982년 인하대학교 전자공학과 학사 졸업

1983년 Georgia Institute Inc, Technology 전자공학과 석사 졸업

1989년 Georgia Institute Inc. Technology 전자공학과 박사 졸업

1984년 3월~1989년 2월 Georgia Institute of Technology Research Assistant

1989년 3월~1992년 2월 Silicon Systems Inc, Tustin Calif. U.S.A Senior Design Engineer

1992년 3월~현재 인하대학교 전자공학과 교수 <주관심분야: 혼성신호처리 집적회로 설계, 설계 자동화 및 소자/회로/시스템 모델링 등>