논문 2012-49SD-2-3

# 공핍 모드 InGaZnO 박막 트랜지스터를 이용한 저소비전력 스캔 구동 회로

(Low Power Consumption Scan Driver Using Depletion-Mode InGaZnO Thin-Film Transistors)

이 진 우\*, 권 오 경\*\*

(Jin-woo Lee and Oh-kyong Kwon)

요 약

본 논문에서 공핍 모드 n-채널 InGaZnO 박막트랜지스터를 이용하여 소비전력이 낮은 스캔 구동 회로를 제안한다. 제안된스캔 구동 회로는 단 2개의 클록 신호만을 사용하고 추가적인 마스킹 신호나 회로가 필요 없이 이웃하는 스캔 출력 간에 겹쳐짐이 없는 스캔 출력 신호를 만들어 낸다. 클록 신호를 줄임과 동시에 단락 전류를 줄임으로써 소비전력을 줄일 수 있었다. 모의 실험 결과 트랜지스터 문턱전압의 편차 범위가 -3.0 ~ 1.0V일 때에도 스캔 출력 신호가 정상적으로 출력됨을 확인하였다. XGA의 해상도를 갖는 디스플레이를 대상으로 양과 음의 전원 전압이 각각 15V, -5V이고 동작 주파수가 46KHz일 때, 스캔구동 회로의 소비전력이 4.89mW이다.

#### **Abstract**

A low power consumption scan driver using depletion-mode n-type InGaZnO thin-film transistors is proposed. The proposed circuit uses 2 clock signals and generates the non-overlap output signals without the additional masking signals and circuits. The power consumption of the proposed circuit is decreased by reducing the number of the clock signals and short circuit current. The simulation results show that the proposed circuit operates successfully when the threshold voltage of TFT is varied from -3.0V to 1.0V. The proposed scan driver consumes 4.89mW when the positive and negative supply voltage is 15V and -5V, respectively, and the operating frequency is 46KHz on the XGA resolution panel.

Keywords: shift register, depletion mode, InGaZnO, scan driver, low power

## I. 서 론

산화물 반도체는 비교적 낮은 온도에서 공정이 가능하여 플라스틱 기판을 활용한 플렉시블 디스플레이에 이용 가능하며<sup>[1]</sup>, 가시광선 영역에서 투명하여 투명 디

스플레이 분야에도 응용이 가능하다<sup>[2~3]</sup>. 이러한 장점을 바탕으로 최근 디스플레이 분야에서 산화물 박막 트랜지스터를 이용하려는 노력이 시도되고 있다<sup>[4~5]</sup>. 더욱이디스플레이가 발전함에 따라 대면적, 고해상도 디스플레이 및 3차원(3D) LCD TV가 요구하고 있는데, 산화물 박막 트랜지스터는 기존의 비정질실리콘 박막 트랜지스터(amorphous silicon thin-film transistor)보다 전계효과 이동도 특성이 우수하고<sup>[6~7]</sup> 공정 호환이 가능하기 때문에 차세대 트랜지스터로 채택될 가능성이 높아지고 있다.

ZnO 나 InGaZnO 와 같은 산화물을 이용한 반도체 소자가 개발되면서 산화물 반도체를 패널에 내장시켜

(Department of Electronics and Computer Engineering, Hanyang University)

접수일자: 2011년8월31일, 수정완료일: 2012년2월15일

<sup>\*</sup> 정회원, 한양대학교 전자통신컴퓨터공학부 (현 삼성전자)

<sup>(</sup>Department of Electronics and Computer Engineering, Hanyang University)

<sup>\*\*</sup> 평생회원, 한양대학교 전자통신컴퓨터공학부

스캔 구동 회로로 이용하고자 하는 연구가 진행되고 있다<sup>[5,8]</sup>. 하지만 산화물 반도체는 침입형 (intersititial) 금속 물질과 산소 공공(vacancy)의 결함들이 많이 존재하고 있으며, 산소의 공공(vacancy)과 침입형 금속물질은 전자를 제공하는 도너(doner)역할을 하기 때문에 n형이면서 공핍 모드 동작 특성을 띠게 된다<sup>[9~10]</sup>. 더욱이, 빛 또는 전압에 의한 스트레스로 인해 n-채널 소자의 문턱전압이 음의 전압으로 이동된다<sup>[11~12]</sup>. 따라서산화물 반도체를 이용한 스캔 구동 회로는 공핍 모드 (depletion mode) n-채널 박막트랜지스터를 이용하여설계해야 한다.

지금까지 공핍 모드 InGaZnO를 이용한 스캔 구동 회로에 대한 여러 가지 논문이 발표되어 왔다<sup>[13~17]</sup>. 특 히, 제조 단가와 소비 전력을 줄이기 위해 외부 핀으로 부터 클록 및 마스킹을 위한 신호의 개수를 줄이려는 노력이 이어져 왔다. 클록 신호 3개를 이용한 스캔 구 동 회로가 발표 되었고[14~15], 2개를 이용한 스캔 구동 회로에 관한 논문도 발표 되었다<sup>[13]</sup>. 하지만 연속되는 스캔 출력 신호가 겹쳐져 있기 때문에 실제 디스플레이 에 적용하려면 추가적인 마스킹 신호 및 회로가 필요하 다. 겹쳐지지 않는 스캔 출력 신호를 만들어 내는 스캔 구동 회로에 관한 논문이 발표 되었으나, 스캔 구동 회 로 내부에서 클록 신호를 이용하여 마스킹 신호를 만들 어 사용하였기에 6개의 클록 신호를 필요로 하였다<sup>116~</sup> 17]. 그러나 클록 신호가 많게 되면 클록 신호에 연결되 어 있는 부하를 충,방전하기 하기 위한 전력 소모가 증 가하게 된다. 또한, 클록 신호의 신호 지연을 감소시키 기 위해 배선 폭을 증가해야 하므로 회로의 면적도 증 가하게 된다. 따라서 클록 신호를 줄임으로써 소비 전 력과 회로 면적을 줄일 수 있는 스캔 구동회로를 설계 해야 한다.

본 논문에서는 추가적인 마스킹 신호없이 2개의 클록 신호만으로 겹쳐지지 않는 스캔 출력 신호를 만들어내어 소비 전력 및 제조 단가를 줄일 수 있는 스캔 구동 회로를 제안하여 시뮬레이션으로 검증하였다.

## Ⅱ. 본 론

## 1. InGaZnO 박막 트랜지스터의 전기적 특성과 시뮬레이션 모델링

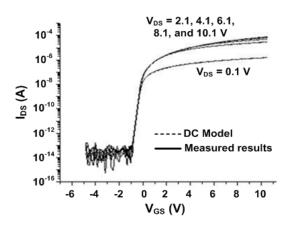

그림 1은 채널의 폭과 길이가 각각 40µm, 20µm 인 InGaZnO 단위 소자의 측정을 통해 구한 전달 특성 곡

그림 1. InGaZnO TFT 의 측정된 전달 특성 곡선과 모 델링 한 전달 특성 곡선

Fig. 1. Measured transfer characteristic curves vs. modeling transfer characteristic curves of the InGaZnO TFT.

표 1. lnGaZnO 소자들의 DC 특성 (a) 측정된 소자 특성 (b) 모델링한 소자 특성

Table 1. DC characteristics of InGaZnO TFTs

- (a) Measured characteristics

- (b) Modeling characteristics.

(a)

| 샘플 수                      | 64           |  |

|---------------------------|--------------|--|

| 채널 폭 / 길이 (μm)            | 40 / 20      |  |

| 문턱 전압 (V)                 | -1.04 ~ 0.12 |  |

| 전계효과 이동도(cm²/V·s)         | 9.5 ~ 10.9   |  |

| Sub-threshold 기울기(mV/dec) | 80.4 ~ 152.7 |  |

(b)

| 채널 폭 / 길이 (µm)            | 40 / 20 |

|---------------------------|---------|

| 문턱 전압 (V)                 | -0.42   |

| 전계효과 이동도(cm²/V·s)         | 10.5    |

| Sub-threshold 기울기(mV/dec) | 110     |

선(I<sub>DS</sub>-V<sub>GS</sub> curve)과 이를 통해 모델링한 전달 특성 곡선이다. 64개 샘플 중 평균 곡선을 통해 모델링을 하였다. 샘플들의 전기적 특성을 표 1 (a)에 나타내었다. 문턱전압, 전계효과 이동도의 표준 편차는 각각 0.3V, 0.6cm²/V·s 이다. 모델링하여 구한 소자의 DC 특성을 표 1 (b)에 나타내었다. 모델링한 문턱전압, 전계효과이동도는 각각 -0.42V, 10.52cm²/V·s 이다. 또한 소자의 InGaZnO, gate oxide 물질의 특성 및 소자의 두께, 폭을 고려하여 게이트와 소스 간, 게이트와 드레인 간의

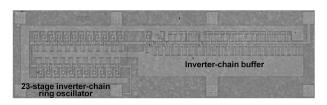

그림 2. 링오실레이터 광학현미경사진

Fig. 2. Micrograph of ring oscillator.

표 2. InGaZnO 소자 모델 파라미터의 AC 특성 검증 Table 2. AC characteristics verification of the model parameter InGaZnO TFTs.

|                        | 측정 결과 | 모델링 결과 |

|------------------------|-------|--------|

| 링오실레이터 동작<br>주파수 (KHz) | 62.1  | 62.4   |

| 파형 진폭 (V)              | 2.3   | 2.2    |

오버랩 캐패시턴스를 적용하여 AC 특성을 모델링하였다. InGaZnO 소자의 AC 특성을 보기 위해 23단의 슈도 인버터(pseudo inverter)를 이용하여 링 오실레이터 (ring oscillator)를 구성했다. 그림 2는 주파수 특성을 살펴보기 위해 InGaZnO 소자로 구성한 링오실레이터의 광학현미경사진이다. 표 2는 전원 전압이 5V 일 때, 측정된 링오실레이터의 주파수 특성과 파형 진폭에 대하여 측정 결과와 모의 실험 결과를 보여 주고 있다.

표 2에서 나타난 것처럼, 모의 실험 결과와 측정 결과가 잘 맞는 것을 알 수 있다. 이는 제작된 소자에 대한 DC 및 AC 모델링이 잘 맞는 것으로, 본 논문에서 제안한 스캔 구동 회로를 시뮬레이션만으로 검증할 수 있도록 하였다.

## 2. 제안한 시프트 레지스터

#### 가. 회로 설명

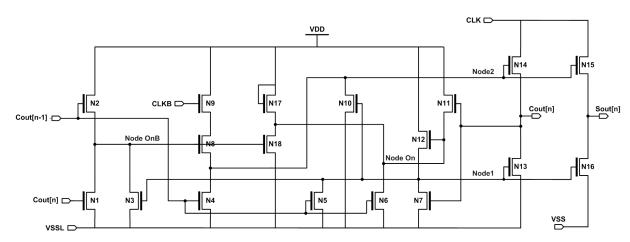

그림 3은 제안된 시프트 레지스터의 회로도이다. 상호 반대 위상을 갖는 두 개의 클록 신호를 사용하였다. 소 비 전력을 줄이기 위해 클록 수를 최소화 하였다. CLK 신호의 하이레벨 동안 출력 스캔 신호를 만들고, 로우레 벨 동안은 출력 스캔 신호 사이를 마스킹 함으로써 마스 킹 신호를 클록 신호에 내장시켰다. 풀다운 노드(Node 1)가 하이 레벨이 될 때 트랜지스터 N10을 통해 풀업 노 드(Node 2)가 VSSL이 되어 단락 전류를 없앴다. 또한 풀다운 노드(Node 1)와 풀업 노드(Node 2)를 제어하는 부분의 VSSL 전원을 VSS보다 -5V 낮은 전압으로 사 용함으로써 공핍 모드 트랜지스터에서도 안정적으로 동 작할 수 있도록 하였다. Node On이 하이레벨이 될 때, 트랜지스터 N7, N11, N12는 인버터로 동작한다.

n-채널 트랜지스터만으로 회로를 구성함에 있어서 출력을 VDD까지 풀업하는 것은 문턱전압의 편차가 심하여 어려움이 있다. 이를 해결하기 위해서 구동 트랜지스터의 게이트 (Node 2)의 전압을 VDD 이상으로 부스트업 하여 출력을 구동하는 방식을 사용하였다. 이를 위하여, 트랜지스터 N14, N15의 드레인 노드를 CLK 신호로 입력하여 N14, N15의 게이트-드레인간의 기생캐패시터를 이용하여 부스트업 효과를 볼 수 있게 하였다 [13~14, 16]. 이러한 부스트업 효과를 갖도록 클록을 사용하는 회로 구조는 비정질 실리콘 박막트랜지스터를 이용한 스캔 드라이버에서 많이 사용되고 있는 구조이다 [13~14, 16]

그림 3. 제안한 n-채널 시프트 레지스터의 단위 블록 회로도

Fig. 3. The schematic diagram of unit block of the proposed n-channel shift register.

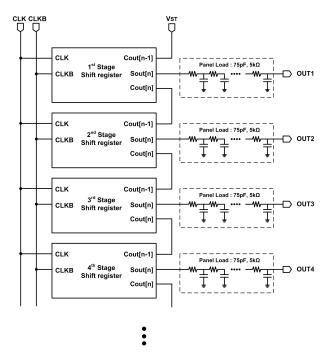

그림 4. 제안한 스캔 구동 회로의 블록 회로도 Fig. 4. The block diagram of the proposed scan driver.

스캔 드라이버의 시작 신호(VST) 와 클록은 타이밍 콘트롤러에서 패널의 로드를 고려하여 생성하여 공급하 며, 클록의 전압 레벨도 스캔드라이버에서 사용하는 고 전압 레벨로 제공한다. 스캔 드라이버의 클럭 주파수가 수십 kHz 정도로 낮기 때문에 타이밍 콘트롤러에 내제 되어 있는 클록 생성기와 클록 드라이버를 사용하면 일 반적인 clock skew 의 문제는 발생하지 않는다.

CMOS 소자를 이용하여 스캔 구동 회로를 구현하는 경우 시프터 레지스터, 레벨 시프터 그리고 버퍼 블록으로 스캔 구동 회로를 구성하지만 산화물 반도체를 이용하여 패널에 내장된 스캔 구동 회로를 구현하면서 회로 면적 증가 및 전력 효율 문제로 인해 출력 신호로 바로 이용 가능한 레벨의 신호를 타이밍 콘트롤러에서 공급하고 시프트 레지스터만을 패널에 내장 시킴으로써 스캔 구동 회로를 구현하는 것이 일반적인 방법이다[13~17].

그림 4는 패널 로드가 포함된 스캔 구동 회로의 블록 회로도이다. 그림 3으로 이루어진 시프트 레지스터 단위 블록이 하나의 단을 구성한다. 단위 시프터 레지스터 탈록은 VSSL~VDD(-10V~15V) 레벨로 타이밍 콘트롤러로부터 들어오는 CLK, CLKB 신호를 입력받아스캔 신호를 출력하고 전,후 시프터 레지스터 블록들과 캐리 신호들(Cout[n-1], Cout[n])로 연결됨으로써 스캔 출력 신호를 순차적으로 만들어낸다.

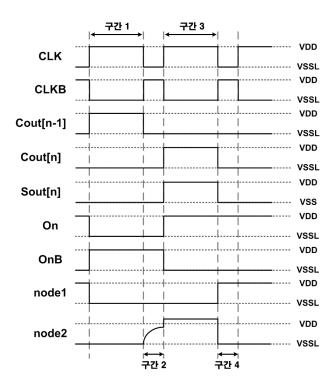

그림 5. 제안한 n-채널 시프트 레지스터의 타이밍도

Fig. 5. The timing diagram of the proposed n-channel shift register.

표 3. 시뮬레이션 조건들

Table 3. Simulation conditions.

| Resolution format |             | XGA (1,024 × 768 ) |  |  |

|-------------------|-------------|--------------------|--|--|

| Frame rate        |             | 60 Hz              |  |  |

| Line time         |             | 21.7 µs            |  |  |

| Gate line load    | Resistance  | 5 kΩ               |  |  |

|                   | Capacitance | 75 pF              |  |  |

| VDD               |             | 15V                |  |  |

| VSS               |             | -5V                |  |  |

| VSSL              |             | -10V               |  |  |

## 나. 동작 설명

그림 5에서는 제안된 시프트 레지스터의 동작 타이 밍 다이어그램을 나타내었다. 그림 5에 나타내었듯이스캔 출력 신호를 만드는 과정은 4 구간으로 이루어진다. 구간 1, 구간 3 동안에는 스캔 출력을 내보내고 구간 2, 구간 4 동안에는 스캔 출력 신호가 겹치지 않도록스캔 출력을 마스킹한다. 구간 1에서는 전 단의 캐리신호인 Cout[n-1]이 하이레벨이 된다. 트랜지스터 N4, N5, N6에 의해 Node 2, Node 1, Node On의 전압이 모

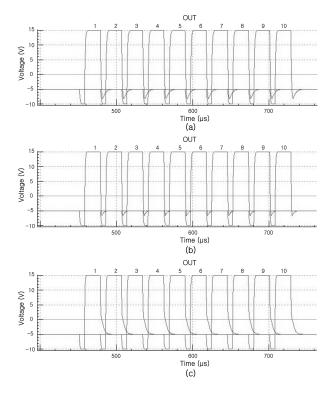

그림 6. 제안한 n-채널 시프트 레지스터의 시뮬레이션 출력 파형 (a) Vth=1V, (b) Vth=0V, and (c) Vth=-2V

Fig. 6. The simulated waveforms of the proposed n-channel shift register at (a) Vth=1V, (b) Vth=0V, and (c) Vth=-2V

두 VSSL이 된다. 그러면 인버터에 전류가 흐르지 않아 Cout과 Sout은 각각 VSSL과 VSS가 된다. 구간 1에서 하이레벨이 된 Node OnB 전압은 구간 2에서도 하이레 벨이 유지가 된다. 또한 CLKB 신호가 하이레벨이 되어 트랜지스터 N8, N9 가 동시에 켜지게 되어 Node 2 전 압이 VDD 근처까지 상승한다. 그러면 트랜지스터 N14 도 켜지게 되지만 Cout, Sout은 CLK 레벨에 따라 VSSL을 유지한다. Node On 전압은 VSSL을 유지하고 인버터는 여전히 전류가 흐르지 않아 Node 1은 VSSL 을 유지한다. 구간 3에서는 Node OnB와 CLKB 가 VSSL이 된다. 이때 Node 2 전압은 CLK 신호가 하이 레벨이 되면서 부스트업 효과에 의해 VDD 이상으로 증가한다. 트랜지스터 N14에 의해 Cout[n]은 VDD가 되고 인버터를 통해 Node 1은 VSSL이 된다. Node 1과 Node 2에 의해 Cout[n]은 단락전류 없이 하이레벨을 유지할 수 있다. 구간 4에서는 Cout[n]이 CLK 신호에 따라 VSSL이 되고 인버터를 통해 출력에 연결된 Node 1은 하이레벨로 상승한다. 이와 동시에 트랜지스터 N10 이 켜지면서 Node 2는 VSSL로 떨어진다. 따라서 구간 4에서도 단락전류 없이 Cout[n]은 로우레벨로 유지될 수 있다.

## Ⅲ. 모의 실험 결과

## 1. 출력 파형

시뮬레이션은 10단의 채널을 갖는 스캔 구동 회로로 진행하였다. 시뮬레이션에 대한 조건을 표 3에 나타내었다. XGA  $(1,024 \times 768)$ 의 해상도를 갖는 패널을 대상으로 하여 패널 로드는 75 pF에  $5k\Omega$ 의 저항으로 구성하였다<sup>[15]</sup>.

제안한 시프트 레지스터로 시뮬레이션한 결과를 그림 6에 나타내었다. 그림 6은 문턱전압이 각각 (a) 1V, (b) 0V, 그리고 (c) -2V 일 때 게이트 드라이버의 출력 파형이다. 제안된 시프트 레지스터는 문턱전압이 -3V 까지 동작한다. 또한 XGA의 해상도를 갖는 패널을 구동하는데 필요한 46KHz의 주파수에서 10단의 시프트레지스터 출력이 겹치지 않게 정상적으로 만들어 짐을확인하였다.

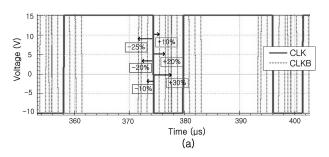

제안된 시프트 레지스터에서 CLK 신호와 CLKB 신

그림 7. 제안한 n-채널 시프트 레지스터의 클록 왜곡 허용오차 시뮬레이션 결과 (a) CLK에 대한 CLKB 왜곡 조건, (b) 왜곡 조건에 따른 출력 파 형

Fig. 7. The clock skew tolerance simulation results of the proposed n-channel shift register (a) CLK vs CLKB skew conditions, (b) Output waveforms.

| <u>₩</u> | 4. | 다른 스 | ∟캔 구동 | 회로들과 | 성능 | 비교 |  |

|----------|----|------|-------|------|----|----|--|

|          |    |      |       |      |    |    |  |

Table 4. Performance comparison of other scan drivers.

| 참조 논문      | [15]         | [16]        | [17]         | 제안한 스캔 구동<br>회로 |

|------------|--------------|-------------|--------------|-----------------|

| 출력 신호      | overlap      | non-overlap | non-overlap  | non-overlap     |

| 마스킹 신호     | 필요 없음        | 클록 신호 이용    | 클록 신호 이용     | 필요 없음           |

| 클록 신호수     | 3            | 6           | 6            | 2               |

| 공급 전원      | VDD,VSS,VSSL | VDD,VSS     | VDD,VSS,VSSL | VDD,VSS,VSSL    |

| 패널 로드      | 75pF, 5kΩ    | 50pF, 5kΩ   | 100pF, 25kΩ  | 75pF, 5kΩ       |

| 패널 해상도, 크기 | XGA, 5인치     | _           | VGA, 7인치     | XGA, 5인치        |

| 출력단 수      | 10           | 480         | 480          | 768             |

| 소모 전력(mW)  | 0.085        | 39.12       | 10.1         | 4.89            |

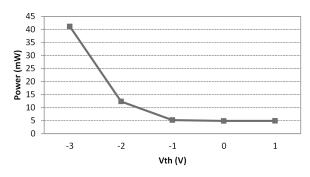

그림 8. 제안한 XGA용 스캔드라이버의 문턱전압에 따른 소비 전력

Fig. 8. Power consumption of the proposed XGA resolution scan driver as a function of the threshold voltage.

호간 clock skew 시뮬레이션을 그림 7에 나타내었다. CLK 신호에 대해서 CLKB 신호를 한 주기의 - 25%에서 30%까지 왜곡을 주어 시뮬레이션을 진행한 결과 출력 파형이 정상적으로 동작함을 확인하였다.

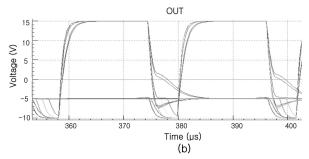

## 2. 소비 전력 및 주파수 특성

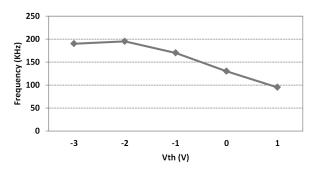

표 3에 나타낸 XGA 패널 조건에서 제안한 스캔 구동 회로의 소비 전력은 46KHz에서 4.89mW이다. 문턱전압에 따른 소비 전력을 그림 8에 나타내었다. 그림 8에서 볼 수 있듯이 문턱전압이 증가하면서 스캔 드라이버의 소비 전력은 줄어든다. 또한, 문턱전압에 따른 최대 동작 주파수는 그림 9에 나타내었다. 주파수 시뮬레이션 결과 InGaZnO 박막 트랜지스터로 스캔 구동 회로를 구성하여 XGA 이상의 해상도를 갖는 패널을 스캔동작시킬 수 있음을 확인하였다.

## 3. 제안한 스캔 구동 회로 성능

제안한 스캔 구동 회로의 성능을 표 4에 요약하였다.

그림 9. 제안한 XGA용 스캔드라이버의 문턱 전압에 따 른 동작 주파수

Fig. 9. Operation frequence of the proposed XGA resolution scan driver as a function of the threshold voltage.

소비 전력면에서 장점을 갖고 있다. 소비 전력을 줄일 수 있었던 이유는 첫째, 마스킹 신호가 내장된 클록 신호를 이용함으로써 마스킹 신호를 만들기 위한 여러개의 클록 신호가 필요하지 않아 클록 신호를 줄였기 때문이다. 클록 신호는 토글링 할 때마다 전하를 충,방전하기 때문에 전력이 많이 소비된다. 따라서 클록 신호가 줄어들면 소비 전력이 줄어든다. 둘째, 출력 신호가하이레벨에서 로우레벨로 떨어지고 난 후 클록 신호가 한이레벨에서 로우레벨로 떨어지고 난 후 클록 신호가토글 할 때 Node 2가 커플링 영향을 받지 않도록 Node 1이 트랜지스터 N10을 통해 Node 2를 안정적으로 로우레벨로 잡아주어 단락 전류를 없앰으로써 소비 전력을 줄일 수 있었다.

## Ⅳ. 결 론

본 논문에서는 2개의 클록 신호를 가지고 겹쳐지지 않는 출력 신호를 내는 스캔 구동 회로를 제안하였다. 제안한 회로는 클록 수를 줄이고 단락 전류를 줄여 저 소비전력 동작이 가능하게 하였다. 또한, 겹쳐지지 않는 출력 스캔 파형을 만들어 내기 때문에 외부 마스킹 신호 및 회로가 필요하지 않아 타이밍 콘트롤러의 기능을 단순화 할 수 있다. 제안된 스캔 구동 회로는 5인치 XGA의 해상도를 갖는 패널을 대상으로 46KHz 주파수에서 4.89mW의 소비 전력을 갖는다. Vth=-3.0V 까지스캔 출력 신호가 정상적으로 출력됨을 시뮬레이션을 통해 검증하였다.

## 참 고 문 헌

- [1] S.-H. Ko Park, C.-S. Hwang, J.-I. Lee, S.-M. Chung, Y.-S. Yang, L.-M. Do and H.-Y. Chu, "Transparent ZnO thin film transistor array for the application of transparent AM-OLED display," in *Dig. Soc. Inf. Display*, 2006, pp. 25–28.

- [2] S. Masuda, K. Kitamura, Y. Okumura and S. Miyatake, H. tabata and T. Kawai, "Transparent thin film transistors using ZnO as an active channel layer and their electrical properties," *J. Appl. Phys.*, Vol. 93, No. 3, pp. 1624–1630, Feb. 2003.

- [3] 신한재, 이근영, 한동철, 손선영, 김영태, 서승한, 이도경, "플랙시블 IGZO기반의 투명 박막트랜지스터," 대한전자공학회 하계 학술대회 논문집, 470-471쪽, 2009년 7월

- [4] J. Y. Kwon, K S. Son, J. S. Jung, T. S. Kim, M. K. Ryu, K. B. Park, B. W. Yoo, J. W. Kim, Y. G. Lee, K. C. Park, S. Y. Lee, and J. M. Kim, "Bottom-gate gallium indium zinc oxide thin-film transistor array for high-resolution AMOLED display," *IEEE Electron Device Lett.*, vol. 29, no. 12, pp.1309–1311, Dec. 2008.

- [5] T. Osada, K. Akimoto, T. Sato, M. Ikeda, M. Tsubuku, J. Sakata, J. Koyama, T. Serikawa, and S. Yamazaki, "Development of driver integrated panel using amorphous In-Ga-Zn-Oxide TFT," in *Proc. Soc. Inf. Display*, 2009, pp. 184-187.

- [6] J.-K. Jeong, J.-H. Jeong, J.-H. Choi, J.-S. Im, S.-H. Kim, H.-W. Yang, K.-N. Kang, K.-S. Kim, T.-K. Ahn, H.-J. C, M.-K. Kim, B.-S. G, J.-S. Park, Y.-G. Mo, H.-D. Kim and H.-K. Chung, "12.1-inch WXGA AMOLED display driven by Indium-Gallium-Zinc Oxide TFTs array," in *Dig. Soc. Inf. Display*, 2008, pp. 1-4.

- [7] M. Stewart, R. S. Howell, L. Pires and M. K. Hatalis, "Polysilicon TFT technology for active

- matrix OLED displays," *IEEE Trans. Electron Devices*, 48, pp. 845–851 (2001).

- [8] C.-K. Kang, Y.-S. Park, S.-I. Park, Y.-G. Mo, B.-H. Kim, and S.-S. Kim, "Integrated Scan Driver with Oxide TFTs Using Floating Gate Method," in *Proc. Soc. Inf. Display*, 2011, pp. 25–27.

- [9] D. C. Look, G. C. Farlow, P. Reunchan, S. Limpijumnong, S. B. Zhang, and K. Nordlund, "Evidence for Native-Defect Donors in n-Type ZnO," *Phys. Rev. Lett.* 95, 225502\_1-225502\_4, 2005.

- [10] 이상렬, 송용원, 장성필, "디스플레이 Backplane TFT 응용을 위한 차세대 산화물 반도체 응용기술," 대한전자공학회 전자공학회지, 제35권 제8호, 60-70쪽, 2008년 8월

- [11] J.-H. Shin, J.-S. Lee, .C.-S. Hwang, S.-H. Ko Park, W.-S. Cheong, M. Ryu, C.-W. Byun, J.-I. Lee, and H. Y. Chu, "Light effects on the bias stability of transparent ZnO thin film transistors," *ETRI J.*, vol. 31, no. 1, pp. 62-64, Feb. 2009.

- [12] 박상희, 황치선, 조경익, 유민기, 윤성민, 변춘원, 양신혁, "산화물 트랜지스터를 이용한 투명디스플 레이," 대한전자공학회 하계 학술대회 논문집, 제 33권 1호, 1996-1999쪽, 2010년 6월

- [13] B. Kim, C.-I. Ryoo, S.-J. Kim, J.-U. Bae, H.-S. Seo, C.-D. Kim, and M.-K. Han, "New Depletion-Mode IGZO TFT Shft Register," *IEEE Electron Device Lett.* 2010.

- [14] Y.-S. Park, B.-Y. Chung, C.-K. Kang, S.-I. Park, K.-J. Im, J. H. Jeong, B.-H. Kim, and S. S. Kim, "Oxide TFT Scan Driver with Dynamic Threshold Voltage Control," in *Proc. Soc. Inf. Display*, 2011, pp. 718–721.

- [15] S.-J. Yoo, J.-S. Kang and O.-K. Kwon, "Low Power Consumption shift Register using Depletion Mode Amorphous In-Ga-Zn-O TFTs," to be published in *IMID DIGEST* 2011.

- [16] J.E. Pi, M.W. Oh, B.H. Kim, R. Tao, H.K. Leem, J.S. Kim, H.S. Oh, and K.C. Park, "A Scan Driver Compatible with Oxide TFTs Operating in Depletion-Mode," *IMID DIGEST*, 2010, pp. 118–119.

- [17] T.-H. Hwang, S.-I. Hong, W.-K. Hong, W.-H. Cui, I.-S. Yang, O.-K. Kwon, C.-W. Byun, S.-H. Ko Park, C.-S. Hwang, and K. I. Cho, "A scan driver circuit using transparent thin film transistors," in *Proc. Soc. Inf. Display*, 2009, pp. 1136–1139.

## --- 저 자 소 개 --

이 진 우(정회원)

2005년 한양대학교 전기전자컴퓨터공학부 학사 졸업.

2008년 한양대학교 전자통신컴퓨터공학과 석사 졸업.

2008년~현재 삼성전자 시스템 LSI 선임연구원.

<주관심분야: 아날로그 회로 및 저전력 회로 설계, Display Driver IC 설계>

권 오 경(평생회원)

1978년 한양대학교 공과대학 전자 공학과 학사 졸업.

1986년 스탠포드 대학교 전기공학 석사 졸업.

1988년 스탠포드 대학교 전기공학 박사 졸업.

1987년~1992년 Texas Instruments,

Semiconductor Process and Design Center, 책임연구원.

1992년~현재 한양대학교 조교수, 부교수, 교수. 2011년~현재 한양대학교 부총장.

2010년~2011년 한국정보디스플레이학회 회장.

2011년~현재 한국공학한림원 부회장.

<주관심분야: 평판 디스플레이 구동 방법 및 구동 회로, 혼성 신호 회로, 지능형 전력관리 직접회로, 의료용 전자기기, 고속 집적 회로의 Interconnection 및 전기적 노이즈 모델링>