논문 2012-49SD-5-5

# 아날로그-디지털 변환기의 정적 파라미터 테스트를 위한 내장 자체 테스트 방법

(A Built-in Self-Test of Static Parameters for Analog-to-Digital Converters)

김 인 철\*, 장 재 원\*, 강 성 호\*\*

(Incheol Kim, Jaewon Jang, and Sungho Kang)

O 0 !

본 논문은 천이 검출기를 이용하여 아날로그-디지털 변환기(ADC)의 정적 파라미터를 테스트 하는 내장 자체 테스트 방법 을 제안한다. 제안하는 방법은 ADC의 정적 테스트에서 가장 널리 사용되는 히스토그램 방법을 대체할 수 있다. 입력되는 테 스트 신호는 상향 램프 신호를 사용하며 오프셋, 게인, INL(Integral Non-Linearity), DNL(Differential Non-Linearity)과 같은 정적 파라미터를 테스트 할 수 있다. 제안하는 방법은 실제 테스트 환경에서 랜덤 노이즈에 의해 발생할 수 있는 천이 구간 문제를 해결할 수 있으며, 테스트 스펙으로 주어지는 오차 허용 범위의 다양한 경우에 대해서 효율적으로 테스트를 수행할 수 있다. 실험 결과는 제안하는 방법이 정적 테스트를 올바르게 수행하는 것과, 기존 방법에 비해 하드웨어 오버헤드가 줄어드는 것을 보여준다.

#### Abstract

A new BIST(Built-In Self-Test) scheme to test ADC(Analog-to-Digital Converter) with a transition detector is proposed. The proposed BIST is able to replaces histogram method, the most popular approach in static testing of ADC. With a ramp signal as an input test stimulus, the proposed BIST calculates ADC's static parameters such as offset, gain, INL(Integral Non-Linearity) and DNL(Differential Non-Linearity). The three detectors in the proposed BIST can deal with a transient zone problem, a phenomenon due to random noise in real test environments and are cost efficient at various acceptable ranges determined as a test spec. The simulation results validate that our method performs accurate static test and show the reduction of the hardware overhead.

Keywords: 아날로그-디지털 변환기(ADC), 내장 자체 테스트, 정적 파라미터, 천이, 오차 허용 범위

#### I. 서 론

변환기(ADC)와 디지털-아날로그 변환기(DAC)와 같은

SoC(System-on-Chip) 환경에서 아날로그-디지털

\* 학생회원, \*\* 평생회원, 연세대학교 전기전자공학과 (Department of Electrical and Electronic Engineering, Yonsei University)

※ 본 논문은 IDEC(IC Design Education Center)의 CAD Tool 지원을 받은 것임. 본 연구는 지식경제 부 및 한양대학교 IDEC 플랫폼 센터의 지원으로 수행하였음.

접수일자: 2011년12월2일, 수정완료일: 2012년5월3일

데이터 변환기들은 칩 내의 아날로그 영역과 디지털 영 역을 연결시켜 주는 필수 요소 중 하나이다<sup>[1]</sup>. 이들 변 환기의 성능은 전체 혼성 신호 회로의 성능에 큰 영향 을 끼치게 되므로 이에 대한 테스트와 검증은 전체 회 로의 신뢰도를 향상시킨다. 그러나 칩 내에 깊숙이 내 장되어 있는 IP들은 그에 대한 접근성이 용이하지 않기 때문에 테스트를 수행하는 데에 어려움이 따르게 된다. 이와 같이 내장된 IP들을 테스트하기 위한 방법으로 내 장 자체 테스트(BIST, Built-in Self-Test)가 소개되었 는데<sup>[2]</sup>, 이는 회로를 테스트 하는 데 있어 약간의 하드 웨어를 추가함으로써 외부 장비의 필요 없이 테스트를

수행할 수 있도록 한 설계 방법이다.

한편, ADC의 테스트는 정적 테스트와 동적 테스트로 분류할 수 있다. 동적 테스트를 수행하기 위해서는 마 이크로프로세서와 같은 연산 모듈이 반드시 필요하기 때문에 내장 자체 테스트로 구현할 경우에는 정적 테스 트 방법이 보다 선호된다. 본 논문에서는 ADC의 정적 테스트 방법에 초점을 둘 것이다.

ADC의 정적 테스트에서는 히스토그램 방법이 대표적이며, 기존 논문에서 히스토그램 방법을 내장 자체테스트에 적용시키고 보다 효율적인 테스트를 수행하기위한 방법들이 제안되었다<sup>[3~5]</sup>. 그러나 히스토그램 방법은 각 코드들의 출현 빈도를 저장하기 위해 하드웨어오버헤드가 커진다는 단점을 가진다.

한편, 히스토그램을 사용하지 않고 천이 검출을 통해 정적 테스트를 수행하는 방법이 제안되었는데<sup>[6~8]</sup>. 이 방법들은 각 코드들의 출현 빈도를 저장하지 않아 테스 트 비용을 줄일 수 있다. Y. Wen은 n-비트의 ADC에 대하여 (n+m)-비트의 카운터를 사용하여 정적 테스트 를 수행하는 방법을 제안하였다<sup>[6]</sup>. 그러나 이 방법은 천 이 구간 문제를 해결하지 못하는 문제점이 있다. 또한 (n+m)-비트의 카운터 대신에 (2+m)-비트의 카운터로 테스트를 수행할 수 있는 방법이 제안되었으나<sup>[7]</sup>. 두 논 문<sup>[6,7]</sup> 모두 DNL 검출기를 구성하기 위해 오차 허용 범 위를 벗어나는 모든 경우를 계산하여야 한다는 단점을 가진다. 이는 오차 허용 범위가 ±1/2 LSB(Least Significant Bit)로 주어지지 않을 경우에 회로의 복잡도 를 증가시킬 수 있다. 기존 논문<sup>[8]</sup>에서는 이러한 DNL 검출기를 개선하였으나. 이 방법은 기존 논문<sup>[7]</sup>과 더불 어 ADC의 상위 비트들에 대한 검증이 필요하다.

본 논문에서는 기존의 방법보다 효율적인 구조로 동일한 테스트를 수행할 수 있는 방법을 제안하며, 정적파라미터 외에 ADC의 상위 비트들에 대한 검증도 수행함을 보여준다. 제안하는 내장된 자체 테스트 구조에 포함되어 있는 각 검출기들의 구조를 Ⅱ장에서, 그 실험 결과와 결론을 Ⅲ장과 Ⅳ장에서 설명하도록 하겠다.

### Ⅱ. 제안하는 내장 자체 테스트 방법

정적 테스트에서는 일반적으로 오프셋, 게인, INL, DNL을 테스트한다. 테스트 입력 신호가 램프 신호이고 오차 허용 범위가  $\pm 1/2$  LSB일 경우 n-비트 ADC에 대한 정적 파라미터들의 계산은 다음과 같이 이루어진다.

INL:

$$-1/2$$

LSB < INL(k) <  $+1/2$  LSB (3)

DNL:

$$-1/2 \text{ LSB} < \text{DNL}(k) < +1/2 \text{ LSB}$$

(4)

이 때 k는 천이가 발생한 횟수를 나타내며, INL(k)는 (k번째 천이까지의 시간 -k LSB)를, DNL(k)는 (k번째 천이까지의 시간 -(k-1)번째 천이까지의 시간 -1 LSB)를 의미한다. k=0은 첫 코드가 출현하는 순간을 의미하며 게인은 마지막 INL 값으로 얻어질 수 있다.

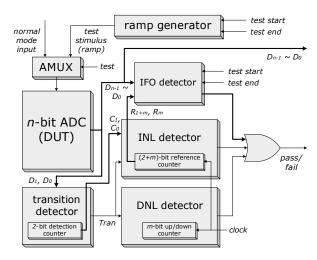

그림 1은 제안하는 내장 자체 테스트 방법의 블록 다이어그램을 나타낸다. 테스트 입력을 제공하기 위해 램프 신호 생성기가 사용되고, 4개의 검출기가 ADC의 정적 테스트를 수행하게 된다. 테스트가 시작되면 초기 값과 오프셋이 계산되며, 이후 천이가 발생할 때마다 Tran 신호가 활성화되어 INL과 DNL이 동시에 테스트된다. 테스트가 종료될 때 최종 값이 테스트되며, 정적 파라미터들 중 오차 허용 범위를 넘는 것이 있을 경우내장 자체 테스트가 고장 신호를 출력한다. 만약 그림 1의 OR 게이트를 제거하여 각 검출기의 출력을 관찰한다면 고장의 종류에 대해서도 확인이 가능하다.

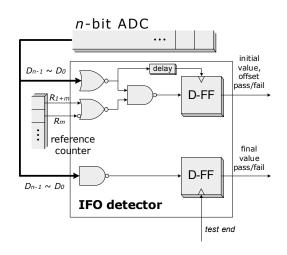

그림 1의 IFO detector는 ADC의 초기 값, 오프셋과 최종 값을 테스트하며, 그 구조는 그림 2와 같다. 테스 트의 시작과 끝에 n-입력 NOR 게이트와 NAND 게이 트가 ADC의 출력이 '000...00'로 시작하여 '111...11'로 끝

그림 1. 제안하는 내장 자체 테스트의 구조 Fig. 1. The structure of the proposed BIST.

그림 2. IFO detector의 구조

Fig. 2. The structure of the IFO detector.

남을 확인하게 된다. 이를 통해서 ADC의 상위 비트들에서 고착 고장 등의 오동작을 검출해 낼 수 있으며 오프셋 고장의 검출은 뒷부분에서 설명하도록 하겠다.

초기 값의 테스트가 끝난 후에, 천이 검출기 (transition detector)는 ADC의 하위 2-비트 값을 관찰 하면서 *Tran* 신호를 활성화시킨다. Y. Wen의 논문<sup>[6]</sup>에 서는 ADC의 최하위 1-비트만을 관찰하였는데, 이로 인 해 천이 구간 문제에 취약점을 가진다. 실제 ADC의 값 이 변화하는 구간에서는 랜덤 노이즈에 의한 불확실성 이 존재하여 출력 값이 상승과 천이를 반복하는 현상이 발생할 수 있다<sup>[9]</sup>. 따라서 ADC의 최하위 1-비트만을 관찰할 경우 천이 구간 내에서 Tran 신호를 여러 번 활 성화시키기 때문에 정적 파라미터를 올바르게 테스트 할 수 없게 된다. 본 논문에서는 천이 구간 문제를 해결 하기 위해 기존에 제안하였던 천이 검출기<sup>[7~8]</sup>와 동일 한 구조를 사용한다. 천이 검출기 내의 2-비트 검출 카 운터는 초기에 '01'로 세팅되어 ADC에서 천이가 발생 될 때마다 카운터 값을 증가시키면서 Tran 신호를 활 성화시킨다. 이 Tran 신호는 INL 검출기와 DNL 검출 기에서 테스트를 위해 사용된다.

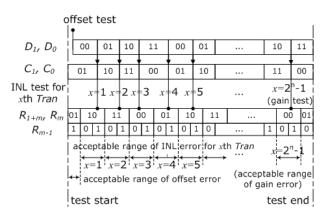

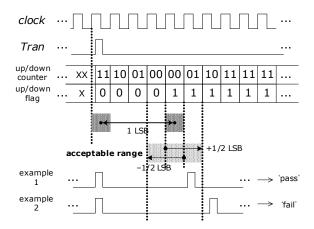

앞서 설명한 것과 같이, 오프셋은 첫 코드의 출현 시점, 게인은 마지막 천이의 시점, INL은 각 천이의 시점을 이용하여 계산된다. 오차 허용 범위를  $\pm 1/2$  LSB로 가정할 때, 오프셋, 게인, INL의 타이밍 다이어그램은 그림 3과 같다. 이 때 m 값은 기존 논문 $^{[7\sim 8]}$ 에서와 동일하게 결정되어 이 경우 m=1이 된다.

그림 3에서와 같이, INL 검출기 내에 있는 (2+m)-비 트 참조 카운터 $(R_{1+m} \sim R_{m-1})$ 는 초기에 '011'로 세팅되며,

그림 3. 오프셋, 게인, INL 테스트의 타이밍 다이어그램 Fig. 3. The timing diagram of the offset, gain and INL test

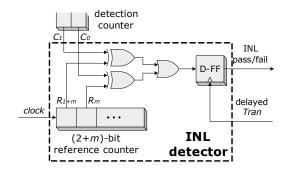

그림 4. INL 검출기의 구조 Fig. 4. The structure of the INL detector.

상위 2-비트가 1 LSB마다 1씩 증가한다. (1)에서 정리된 것과 같이 오프셋 테스트의 오차 허용 범위가 테스트 시작으로부터 1/2 LSB 이므로 상위 2-비트만이 오프셋 테스트에 사용된다. 그림 2의 2-입력 NOR 게이트는 ADC의 초기 값이 참조 카운터의 상위 2-비트가 '01'일 때 발생하는 지를 테스트한다.

한편, INL 테스트는 Tran 신호를 이용하여 각 천이시마다 해당 천이가 오차 허용 범위 내에 발생했는지를 테스트한다. 그림 3에서 볼 수 있듯이, ADC의 첫 번째 천이의 오차 허용 범위는 참조 카운터의 값이 '100'~ '101'인 동안이다. 즉, 참조 카운터의 상위 2-비트가 '10'일 때가 첫 번째 천이의 오차 허용 범위이며, 이후의 천이에 대해서도 참조 카운터의 상위 2-비트만을 이용하여 오차 허용 범위를 표현할 수 있다. 이를 회로로 구현하여 만들어진 INL 검출기의 구조는 그림 4와 같다.

기존 논문 $^{[7,8]}$ 에서 천이 구간이 존재하는 ADC의 출력 값을 받아 이를 제거하는 2-비트 카운터(stabilizer)를 사용한 것과 달리, 본 구조에서는 천이 검출기의 2-비 트 카운터의 값 $(C_1, C_0)$ 을 사용한다. 이 천이 검출 카운 터의 2-비트 값은 현재 ADC의 하위 2-비트 값 $(D_1, D_0)$ 보다 1만큼 크게 되므로 비교를 위해 쓰이는 참조 카운터의 초기 값도 이에 맞게 조절되어 기존 논문의 방법  $^{[7,8]}$ 보다 1 LSB 빠르게 설정된다. 만약 참조 카운터의 1사이클 후에 천이가 발생하여 INL 검출기에서 고장을 검출하지 못하는 경우가 발생한다면, 다음에 설명할 DNL 검출기에서 고장을 검출하게 된다.

DNL 테스트에서는 각 천이 간의 시간 간격을 계산한다. 무고장의 ADC의 경우 각 천이 사이의 시간 간격은 1 LSB 이므로, 실제 각 천이 사이의 시간 간격에서 1 LSB를 뺀 결과가 오차 허용 범위 내에 있는지를 테스트하게 된다. 기존 논문<sup>[6~7]</sup>에서는 이전 천이가 발생했을 때의 참조 카운터의 값과 다음 천이가 발생했을때의 참조 카운터의 값을 비교하여 DNL 테스트를 수행하였으나, 이러한 방법은 이전/다음 천이들에 대한모든 경우의 수를 계산하여 오차 허용 범위와 함께 이를 회로로 표현하여야 한다. 만약 오차 허용 범위가 ±1/2 LSB로 주어지지 않을 경우, DNL 테스트 회로는 매우 복잡해져 하드웨어 크기를 증가시키게 된다.

제안하는 내장 자체 테스트에서는 기존 논문<sup>[8]</sup>에서와 같이 m-비트의 업/다운 카운터를 사용하여 각 천이 간의 시간 간격을 계산한다. Tran 신호가 활성화 될 때 DNL 검출기 내의 업/다운 카운터는 모두 '1'로 초기화되며 클록 신호에 따라 하강 카운트를 시작한다. 하강카운트 중 카운터의 모든 값이 '0'이 되면 상승 카운트를 하게 되어, 업/다운 카운터의 값은 초기화 시점에서부터 대칭의 값을 가지게 된다. 이 때 이전 천이 시점으로부터 1 LSB가 지난 시점의 카운터 값이 '000...00'이되도록 한다면 오차 허용 범위를 간단한 회로로 구현할

그림 5. DNL 테스트의 타이밍 다이어그램 Fig. 5. The timing diagram of the DNL test.

수 있다. 그러나 기존 논문<sup>[8]</sup>에서 업/다운 카운터가 상 승/하강 카운트를 반복하는 것과 달리 제안하는 방법에서는 *Tran* 신호 간격마다 하강-상승 카운트를 1회만수행한다. 즉 업/다운 카운터의 값이 '111…11'에서 '000…00'까지 하강 카운트를 수행한 후 다시 '111…11'까지 상승 카운트를 진행한 다음, 기존 논문<sup>[8]</sup>에서는 다시하강 카운트를 진행하지만 제안하는 DNL 검출기에서는 '111…11'의 값을 유지한다. 이로 인해 기존 논문<sup>[8]</sup>과 달리 천이 간의 간격이 3, 5, 7, … LSB인 경우의 DNL 고장도 검출해 낼 수 있다. 그림 5는 DNL 테스트의 타이밍 다이어그램을 보여준다.

그림 5에서 *Tran* 신호가 활성화 될 때 업/다운 카운터가 초기화되고 하강 카운트를 시작하며, 카운터의 값이 모두 '0'이고 플래그 값이 '1'일 때 1 LSB가 된다. 이때 오차 허용 범위에 해당하는 카운터와 플래그 값은 '00/0', '00/1', '01/1'의 세 가지이므로 적은 수의 논리 게이트를 사용하여 간단히 구현이 가능하다. 또한 모든천이에 대하여 동일하게 동작하므로 기존 논문<sup>[6,7]</sup>에서와 같이 모든 경우의 수를 고려할 필요가 없다.

한편, 그림 5에서 천이 발생 시점과 1 LSB 후를 구간으로 표현하여 오차 허용 범위가 중복되는 현상이 발생하는데, 이는 기존 논문<sup>[6~8]</sup>에서도 동일하게 발생하는현상으로, 각 천이가 시스템 클록과 비동기적으로 발생하기 때문에일어나는현상이다. 이는 m 값을 증가시켜 1 LSB를 더욱 많은 클록 수로 분할하면 개선될 수 있으며, m 값을 증가시키는 방법은 기존 논문<sup>[6~7]</sup>에서는하드웨어 크기를 크게 증가시켜 적용하기 힘들지만 제안하는방법에서는 카운터의 크기를 늘리는 것으로 비교적 쉽게 적용이 가능하다.

## Ⅲ. 실 험

제안하는 내장 자체 테스트 구조의 동작을 검증하기 위하여, ADC에 고장과 천이 구간을 삽입하여 시뮬레이션을 수행하였다. 실험에 사용된 ADC는 8-비트 플래시타입과 12-비트 파이프라인 타입이었다. 또한 본 논문에서는 비교적 정확도가 높은 램프 신호를 필요로 하기때문에 기존 논문에서 제안된 정확도가 높은 램프 신호생성기<sup>[10]</sup>를 사용하였다.

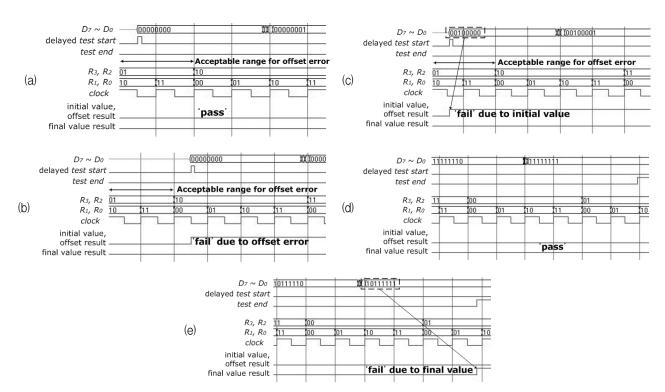

그림 6은 ADC의 상위 비트들에 대한 고장과 오프셋 고장에 대한 시뮬레이션 결과이다. 8-비트 파이프라인 ADC가 사용되었으며, 이 때 오프셋의 오차 허용 범위 는 +1/2 LSB로 가정하였다. 그림 6의 (a), (d)는 고장이 없는 경우, (b), (e)는 ADC의 상위 비트 중 하나에 고장이 존재하여 잘못된 초기 값/최종 값이 출력되는 경우이며, (c)는 오프셋 고장이 존재하는 경우이다.

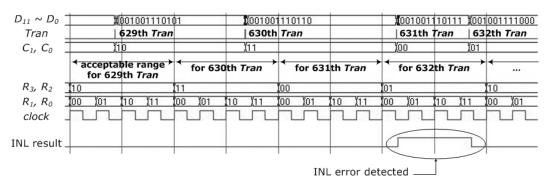

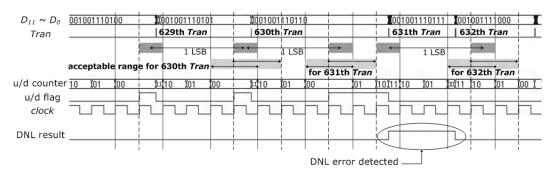

초기 값과 오프셋의 테스트 후에, 천이 검출기는 ADC의 하위 2-비트를 이용하여 *Tran* 신호를 활성화시킨다. 이 때 천이 구간 문제의 해결을 검증하기 위하여 ADC의 출력에 천이 구간을 삽입하였다. 삽입된 천이구간의 길이는 각 코드 길이의 1% 미만이며 랜덤 함수를 이용하여 천이 구간 내에서의 천이 여부가 결정되었다. 제안하는 천이 검출기에서 생성된 *Tran* 신호를 이

용하여, INL 검출기와 DNL 검출기에서 INL 테스트와 DNL 테스트가 동시에 진행된다. INL 테스트와 DNL 테스트의 검증을 위하여 12-비트 ADC를 사용하여 시뮬레이션이 진행되었으며 오차 허용 범위는  $\pm 1/2$  LSB로 가정, m 값은 2로 설정하였다.

그림 7과 8은 각각 INL, DNL 테스트의 결과 파형을 보여준다. 그림 7과 8에서, 631번째 천이가 너무 늦게 발생하여 INL/DNL 테스트의 오차 허용 범위를 모두 벗어났고, 이에 따라 각 검출기의 출력에서 고장 검출 신호가 발생한 것을 확인할 수 있다. 이와 같은 방법으로 Tran 신호를 이용하여 INL 검출기와 DNL 검출기에

그림 6. 초기 값/최종 값과 오프셋 테스트의 결과 파형

Fig. 6. The waveform of the initial, final values and offset test.

그림 7. INL 테스트의 결과 파형

Fig. 7. The waveform of the INL test.

그림 8. DNL 테스트의 결과 파형 Fig. 8. The waveform of the DNL test.

서 각 천이마다 그 테스트 결과를 출력하게 된다.

기존 논문의 방법<sup>16~8]</sup>과 제안하는 구조의 하드웨어 오버헤드와 기타 비교사항들을 표 1에 나타내었다. 하드웨어 오버헤드는 2-입력 NAND 게이트를 기준으로 한 게이트 카운트를 계산하였다. 표 1에서 @, ⑥, ⓒ는 오차 허용 범위를 각각 ±1/2 LSB, ±3/8 LSB, ±7/16 LSB로 설정했을 경우를 의미하며, 이 때 m 값은 각각 2, 4, 5로 설정하였다. 또한 ⑩는 ADC의 상위 비트들에 존재하는 고장의 검출 가능 여부, ⓒ는 천이 구간 문제의 해결 여부를 의미한다.

표 1에서 볼 수 있듯이, 제안하는 방법은 기존 논문[6] 보다 항상 작은 크기의 하드웨어를 가진다. 이는 제안 하는 방법에서 천이 검출기의 크기가 커지고 새로 추가 된 검출기가 있음에도 불구하고 INL, DNL 검출기의 크기가 크게 줄어들었음을 의미한다. 또한 m 값의 크기 가 작을 때, 새로운 DNL 검출기로 인해 기존 방법<sup>[8]</sup>과 제안하는 방법의 하드웨어 크기가 기존 방법<sup>[7]</sup>보다 약 간 더 크지만, m 값이 증가하여도 하드웨어 크기의 증 가 폭이 더 작음을 확인할 수 있다. 따라서 제안하는 방 법은 테스트 하려는 ADC의 크기가 커지거나. 테스트의 정확도를 위해 1 LSB를 보다 많은 클록 수로 나누어 m 값이 증가하더라도 내장 자체 테스트의 하드웨어 크 기가 크게 증가하지 않는다. 또한 새로 추가된 검출기 로 인해 기존 방법<sup>[8]</sup>보다 하드웨어의 크기가 약간 증가 하였지만 INL/DNL 검출기의 개선을 통해 그 증가폭을 최소화하였다. 8-비트와 12-비트의 ADC에 대한 제안 하는 IFO 검출기의 크기는 전체 내장 자체 테스트의 12%, 14%를 차지한다. 하지만 기존 방법<sup>[8]</sup>에 비해 INL, DNL 검출기의 크기를 각각 20%, 4% 줄임으로써 하드 웨어의 증가를 방지하였다. 뿐만 아니라 ADC의 상위 비트들에 대한 고장을 테스트 할 수 있다는 장점을 가

표 1. 기존 방법<sup>[6~8]</sup>과 제안하는 방법의 비교

Table 1. Comparison of the proposed method with the previous ones  $^{[6\sim8]}$ .

|                    |          | 기존 방법 <sup>[6]</sup> | 기존 방법 <sup>[7]</sup> | 기존 방법 <sup>[8]</sup> | 제안하는<br>방법 |

|--------------------|----------|----------------------|----------------------|----------------------|------------|

| 8-비트<br>플래시        | (a)      | 211                  | 147 (-30%)           | 157 (-26%)           | 162 (-23%) |

|                    | <b>b</b> | 331                  | 265 (-20%)           | 247 (-25%)           | 246 (-26%) |

|                    | c        | 394                  | 326 (-17%)           | 279 (-29%)           | 283 (-28%) |

|                    | 평균       | 312                  | 246 (-21%)           | 228 (-27%)           | 230 (-26%) |

| 12-비트<br>파이프<br>라인 | a        | 283                  | 147 (-48%)           | 157 (-45%)           | 167 (-41%) |

|                    | в        | 400                  | 265 (-34%)           | 247 (-38%)           | 251 (-37%) |

|                    | c        | 463                  | 326 (-30%)           | 279 (-40%)           | 288 (-38%) |

|                    | 평균       | 382                  | 246 (-36%)           | 228 (-40%)           | 235 (-38%) |

| <u>(d)</u>         |          | 가능                   | 불가능                  | 불가능                  | 가능         |

| e                  |          | 불가능                  | 가능                   | 가능                   | 가능         |

지며 천이 구간 문제 또한 해결 가능하다.

제안하는 방법은 ADC의 출력만을 관찰하여 정적 파라미터를 계산, 고장 유무를 판별하므로 ADC의 타입에 관계없이 디지털 신호로 테스트가 가능하다. 입력으로 사용되는 램프 신호 생성기는 기존의 성능이 검증된 것을 사용하여 신뢰도를 높였고 정적 테스트를 위한 4개의 검출기는 모두 디지털 회로로 구성되어 내장 자체테스트에서 발생할 수 있는 오차를 최소화하였다. 향후제안하는 방법을 기반으로 한 자체 내장 교정(BISC, Built-in Self-Calibration) 연구에서 실제 칩을 이용한실험을 진행할 예정이다.

#### Ⅳ. 결 론

본 논문에서는 ADC의 정적 테스트를 효율적인 하드웨어로 수행할 수 있는 내장 자체 테스트 방법에 대하여 제안하였다. 제안하는 방법은 정적 테스트에서 흔히쓰이는 히스토그램 방식 대신에 ADC의 천이를 검출하

여 테스트를 수행한다. 이 때 반드시 고려되어야 하는 천이 구간 문제를 기존 논문<sup>[7~8]</sup>에서와 같이 해결하였으며, 또한 상위 비트들에 대한 검증을 수행할 수 있다. 이로 인해 검출기의 수가 증가하였지만 INL/DNL 검출기를 개선함으로써 전체적인 하드웨어 오버헤드의 증가를 방지할 수 있었다. III장의 시뮬레이션 결과는 제안하는 방법이 효율적인 구조를 통해 ADC의 정적 테스트를 수행할 수 있음을 확인시켜 준다.

## 참 고 문 헌

- [1] H. Jiang et al., "Testing High Resolution ADCs with Resolution/Accuracy Deterministic Dynamic Element Matched DACs," Proc. of ITC., pp. 1379–1388, Oct. 2004.

- [2] 김기철 외, "내장된 자체 테스트를 위한 저전력 테스트 패턴 생성기 구조," 전자공학회 논문지, 제 47권 SD편, 제 8호, 29-35쪽, 2010년 8월.

- [3] M. Renovell et al., "Hardware Resource Minimization for a Histogram-based BIST", Proc. of VTS, pp. 247–252, May 2000.

- [4] Y. Wang et al., "Optimal Schemes for ADC BIST Based on Histogram", Proc. of ATS, pp. 52–57, Dec. 2005.

- [5] H. Xing et al., "A Fully Digital-Compatible BIST Strategy for ADC Linearity Testing", Proc. of ITC, pp. 1–10, Oct. 2007.

- [6] Y. Wen, "A BIST Scheme for Testing Analog-to-Digital Converters with Digital Response Analyses," Proc. of VTS, pp. 383-388, May 2005.

- [7] I. Kim et al., "A New Analog-to-Digital Converter BIST Considering a Transient Zone", *IEICE Trans. on Electron.*, vol. E90-C, no. 11, pp. 2161-2163, Nov. 2007.

- [8] I. Kim et al, "Built-in Self-test for A/D Converters in the Presence of Transient Zones", Proc. of ISOCC, pp. 141-144, Oct., 2007.

- [9] M. Burns et al, An Introduction to Mixed-Signal IC Test and Measurement, Oxford University Press, pp. 460-461, 2001.

- [10] W. Lee et al., "A High Precision Ramp Generator for Low Cost ADC Test", Proc. of ICSICT, pp. 2103–2106, Oct., 2008.

- 저 자 소 개 —

김 인 철(학생회원)

2005년 연세대학교 전기전자 공학과 학사 졸업.

2012년 현재 연세대학교 전기전자공학과 통합박사과정.

<주관심분야: 반도체, SoC 설계, SoC 테스트>

장 재 원(학생회원)

2005년 서강대학교 컴퓨터학과 학사 졸업.

2007년 서강대학교 컴퓨터학과 석사 졸업.

2012년 현재 연세대학교 전기 전자 공학과 박사과정.

<주관심분야 : SoC 테스트, 아날로그 테스트>

강 성 호(평생회원)

1986년 서울대학교 제어계측

공학과 학사 졸업.

1988년 The University of

Texas, Austin 전기 및

컴퓨터 공학과 석사 졸업.

1992년 The University of

Texas, Austin 전기 및

컴퓨터공학과 박사 졸업.

1992년 미국 Schlumberger Inc. 연구원. 1992년 Motorola Inc. 선임 연구원. 2010년 현재 연세대학교 전기전자공학과 교수. <주관심분야: SoC 설계, SoC 테스트>