ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 13-04-26

178

# 곱셈기를 재사용하는 8×8 HEVC 코어 역변환기 설계

## 8×8 HEVC Inverse Core Transform Architecture Using Multiplier Reuse

이 종 배\*, 이 성 수\*\*

Jong-Bae Lee\*, Seongsoo Lee\*\*

#### Abstract

This paper proposed an 8×8 HEVC inverse core transform architecture reusing multipliers. In HEVC core transform, processing of lower size block is identical with even part of upper size block. So an 8×8 core transform architecture can process both 8×8 and 4×4 core transforms. However, when 8×8 core transform architecture is exploited, frame processing time doubles in 4×4 core transform, since 8×8 and 4×4 core transforms concurrently process 8 and 4 pixels, respectively. In this paper, a novel inverse core transform architecture is proposed based on multiplier reuse. It runs as an 8×8 inverse core transformer or two 4×4 inverse core transformer. Its frame processing time is same in 8×8 and 4×4 core transforms, and reduces gate counts by 12%.

#### 요 약

본 논문에서는 곱셈기를 재사용하는 8×8 HEVC 코어 역변환기 아키텍처를 제안한다. HEVC 코어 변환에서는 하위 크기 블록 전체와 상위 크기 블록의 짝수 부분이 동일하기 때문에 8×8 코어 변환기 하나로 8×8 및 4×4 코어 변환을 모두 수행할 수 있다. 그러나 8×8 코어 변환이 8 화소를 동시에 처리하는데 반하여 4×4 코어 변환은 4 화소만 동시에 처리하기 때문에 하나의 8×8 코어 변환기로 4×4 및 8×8 코어 변환을 모두 처리하게 되면 4×4 코어 변환에서 프레임을 처리하는데 필요한 시간이 8×8 코어 변환의 2배가 된다. 본 논문에서는 이러한 문제점을 해결하기 위해서 곱셈기를 재사용하여 8×8 코어 역변환기 하나를 두 개의 4×4 코어 역변환기로도 동작시킬 수 있는 새로운 코어 역변환기 아키텍처를 제안한다. 제안하는 8×8 코어 역변환기는 프레임 처리 시간이 8×8 코어 역변환과 4×4 코어 역변환에서 모두 동일하며, 기존에 제안된 아키텍처에 비해 게이트 수를 12% 줄일 수 있다.

Key words: HEVC, inverse core transform, multiplier reuse, small hardware, low power

- \* School of Electronic Engineering, Soongsil University, sslee@ssu.ac.kr, 010-9182-3835

- ★ Corresponding author

- Acknowledgment

"This research was supported by the MKE(The Ministry of Knowledge Economy), Korea, under the ITRC(Information Technology Research Center) support program supervised by the NIPA(National IT Industry Promotion Agency) (NIPA-2013-H0301-12-2006)."

Manuscript received Dec. 24, 2013; revised Dec. 30, 2013; accepted Dec. 30. 2013

## I . 서론

기존의 동영상 압축 국제 표준인 H.264/AVC (advanced video coding)[1][2]는 영상 통화에서 디지털 멀티미디어 방송까지 다양한 분야에 널리 사용되고 있지만, 최근 들어 UHDTV (ultra high definition TV)와 같은 초고화질, 초고해상도 영상 서비스가 개발됨에 따라 4k급, 8k급 영상의 처리 필요성이 대두되기 시작하였다. 이에 따라 ISO/IEC JTC1/SC29/WG11 MPEG 그룹과 ITU-T SG16Q.6

VCEG 그룹은 공동으로 차세대 비디오 코덱 기술인 HEVC (High Efficiency Video Coding)[3]을 발표하였고, 현재 많은 연구팀들이 HEVC의 하드웨어 구현에 대해 활발한 연구를 진행하고 있다.

HEVC를 구성하는 주요 프로세스에는 코어 변환 (core transform), 양자화 (quantization), 인트라 예측 (intra prediction), 움직임 추정 (motion estimation), 움직임 보상 (motion compensation), 디블록킹 필터 (deblocking filter), SAO 필터 (sample adaptive offset filter), CABAC 부호화 (context adaptive binary arithmetic coding) 등이 있다.[4] H.264/AVC 와 HEVC 등 대부분의 동영상 압축 기술은 화소의 공간적 중복성을 제거하기 위해 변환 기법 (transform)을 사용하는데, HEVC에서 사용하는 변환 기법인 코어 변환[4]-[6]은 다음과 같은 특성을 가지 고 있다.

(특성 1) 정변환과 역변환에 동일 계수 사용: HEVC 코어 변환에서는 정변환 (forward fransform) 과 역변환 (inverse transform)에 동일한 계수를 사용 한다.

(특성 2) 짝수 부분만 버터플라이 적용 가능: 변환기법에서는 대개 연산량을 줄이기 위해 버터플라이 구조 (butterfly architecture)가 적용되는데, HEVC 코어 변환에서는 짝수 부분만 버터플라이 구조를 적용할 수 있다.

(특성 3) 재귀 구조 (recursive architecture): 상위 크기 블록의 짝수 부분과 하위 크기 블록 전체의 계수가 동일한 재귀 구조를 가진다.

HEVC 코어 역변환에서는 위 (특성 3)과 같이 하위 크기 블록 전체와 상위 크기 블록의 짝수 부분이동일하기 때문에 8×8 코어 역변환기 하나로 8×8 코어역변환과 4×4 코어역변환을 모두 수행할 수 있다. 그러나 8×8 코어역변환이 8 화소를 동시에 처리하는데 반하여 4×4 코어역변환은 4 화소만 동시에 처리하기 때문에 하나의 8×8 코어역변환기로 4×4 코어역변환과 8×8 코어역변환을 모두 처리하게 되면 4×4 코어역변환과 8×8 코어역변환의 2배가된다. 본 논문에서는 이러한문제점을 해결하기 위해서곱셈기를 재사용하여8×8 코어역변환기 하나를 두개의 4×4 코어역변환기로도동작시킬수있는 새로운 코어역변환기 아키텍처를 제안한다.

## II. 제안하는 HEVC 코어 역변환기의 아키텍쳐

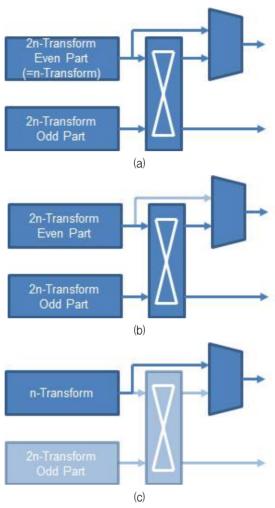

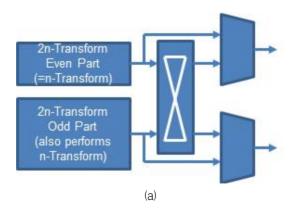

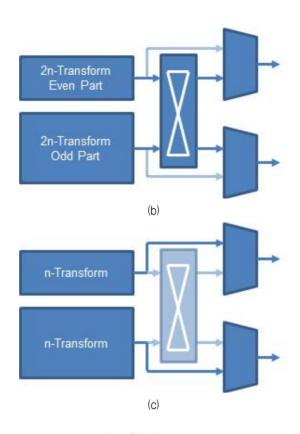

HEVC 코어 역변환기 구조에서 가장 먼저 발표되고 지금도 가장 많이 쓰이는 구조는 그림 1과 같이상위 크기 블록의 짝수 부분을 하위 크기 블록 겸용으로 동작시키는 구조[7]이다. 이 구조의 장점은 별도의 하드웨어 없이 상위 크기 블록의 코어 역변환 (그림 1에서 2n×2n 코어 역변환)을 수행하는 하드웨어로하위 크기 블록의 코어 역변환 (그림 1에서 2n×2n 코어 역변환)을 수행할 수 있다는 것이다. 그러나 서론에서 살펴보았듯이 이러한 구조는 상위 크기 블록이든 하위 크기 블록이든 같은 시간에 같은 개수의 블록을 처리할 수 있기 때문에, 숫자가 2배인 하위 크기 블록을 처리할 때에는 프레임 처리 시간이 2배로증가하는 치명적인 단점이 있다.

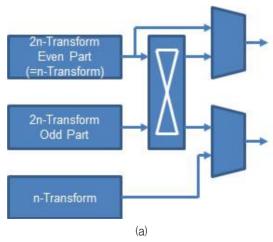

이러한 문제점을 해결하기 위해서 그림 2와 같이하위 크기 블록 처리기를 추가하여 하위 크기 블록을 동시에 2개 처리할 수 있는 구조[8]가 제안되었다. 이러한 구조는 2개의 하위 크기 블록 처리기를 가지고 있기 때문에 당연히 상위 크기 블록을 처리할 때나하위 크기 블록을 처리할 때나하위 크기 블록을 처리할 때나 프레임 처리 시간이동일하지만, 추가 하드웨어가 필요하고 그림 2 (b), (c)에서처럼 매 시점마다 사용되지 않고 있는 유휴하드웨어가 일부 존재한다는 단점이 있다.

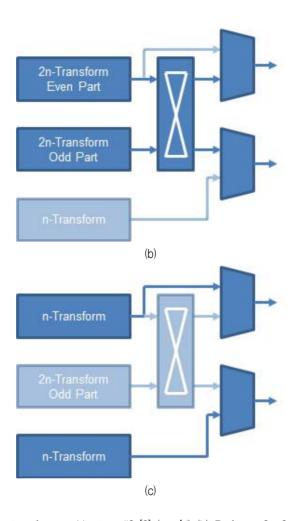

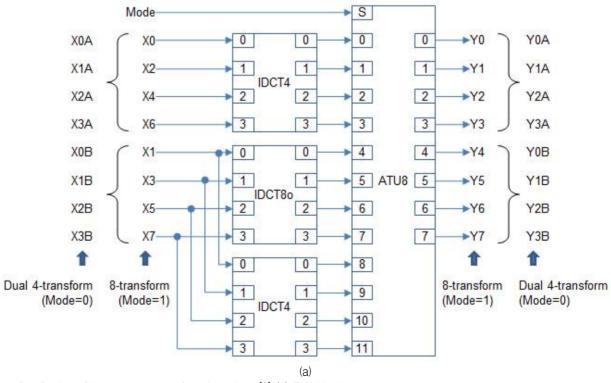

이러한 단점을 보완하기 위해서 본 논문에서는 그 림 3과 같이 상위 크기 블록의 홀수 부분 (그림 3에 서 2n×2n 홀수 코어 역변환) 하드웨어를 수정하여 상 위 크기 블록의 홀수 부분 처리와 하위 크기 블록의 전체 처리를 하나의 하드웨어로 처리하는 구조를 제 안하였다. 일반적으로 위 (특성 2)에서 홀수 부분에는 버터플라이 구조가 적용되지 않기 때문에 어레이 곱 셈기 (array multiplier)를 사용하는데, 상위 크기 블록 의 홀수 부분 (그림 3에서 2n×2n 홀수 코어 역변환) 에는 n×n개의 곱셈기가 필요하게 된다. 버터플라이 구조를 적용하지 않으면 하위 크기 블록 (그림 3에서 n×n 코어 역변환)도 같은 숫자의 곱셈기가 필요하므 로 상위 크기 블록의 홀수 부분 처리기와 하위 크기 블록의 전체 처리기는 동일한 어레이 곱셈기에서 계 수만 바꿔가면서 처리가 가능하다. 따라서 별도의 하 위 블록 처리기가 없어도 프레임 처리 시간이 늘어나 지 않는다. 다만, 어레이 곱셈기에서 계수를 바꿔가기 위한 회로가 필요하기 때문에 하드웨어 크기는 [7]보 다는 늘어나게 된다.

Fig. 1. Conventional inverse core transform architecture #1 [7] (a) Architecture (b) Performs 2n×2n inverse core transform (c) Performs n×n inverse core transform

그림 1. 기존 코어 역변환기의 아키텍쳐 #1 [7] (a) 아키텍쳐 (b) 2n×2n 코어 역변환 수행 (c) n×n 코어 역변환 수행

Fig. 2. Conventional inverse core transform architecture #2 [8] (a) Architecture

그림 2. 기존 코어 역변환기의 아키텍쳐 #2 [8] (a) 아키텍쳐

Fig. 2. Conventional inverse core transform architecture #2 [8] (cont'd) (b) Performs  $2n\times2n$  inverse core transform (c) Performs  $n\times n$  inverse core transform

그림 2. 기존 코어 역변환기의 아키텍쳐 #2 [8] (계속) (b) 2n×2n 코어 역변환 수행 (c) n×n 코어 역변환 수행

Fig. 3. Proposed inverse core transform architecture (a) Architecture

그림 3. 제안하는 코어 역변환기의 아키텍쳐 (a) 아키텍쳐

Fig. 3. Proposed inverse core transform architecture (cont'd) (c) Performs n×n inverse core transform

그림 3. 제안하는 코어 역변환기의 아키텍쳐 (계속) (c) n×n 코어 역변환 수행

## III. 제안하는 HEVC 코어 역변환기의 설계

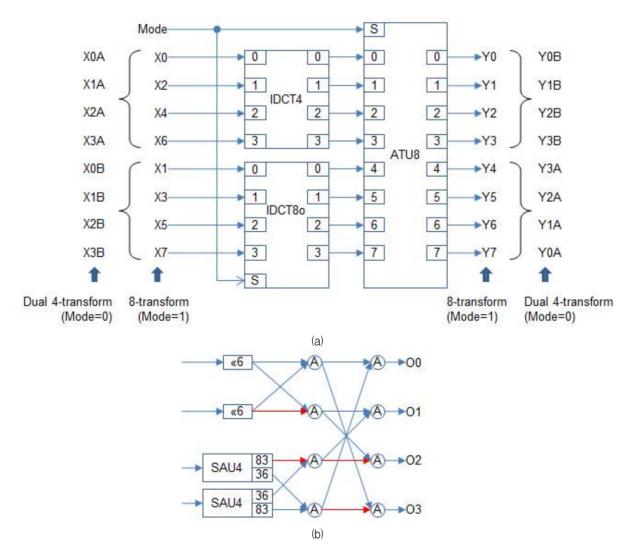

본 논문에서 제안한 아키텍쳐를 검증하기 위해서 그림 4와 같이 8×8 HEVC 코어 역변환기를 설계하였다. 제안하는 코어 역변환기는 그림 4(a)와 같이 4×4 코어 역변환 (8×8 코어 역변환의 짝수 부분과 동일)을 수행하는 IDCT4, 8×8 코어 역변환의 홀수 부분과 4×4 코어 역변환을 하나의 하드웨어로 처리하는 어레이 곱셈기인 IDCT80, 버터플라이 및 MUX 동작을수행하는 ATU8의 세 부분으로 구성되어 있다.

그림 4(b)는 IDCT4 블록인데, 어레이 곱셈기인 SAU4를 사용하여 4×4 코어 역변환의 계수인 {36,64,83}을 곱한다. 그림 4(c)는 IDCT8e 블록의 구조인데, 어레이 곱셈기인 SAU8A, SAU8B를 사용하여 mode=0일 때에는 4×4 코어 역변환의 계수인 {36,64,83}을 곱하고 mode=1일 때에는 8×8 코어 역변환의 홀수 부분 계수인 {18,50,75,89}를 곱하도록 설계되었다.

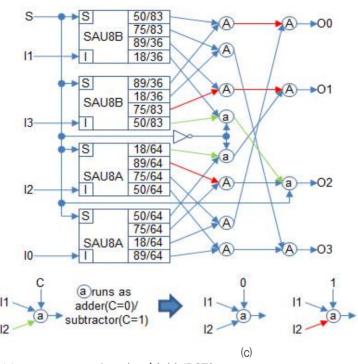

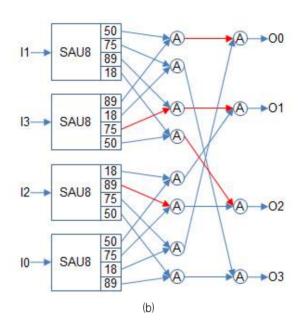

그림 5는 제안하는 8×8 HEVC 코어 역변환기와 비

교하기 위해 [8]의 아키텍처에 기반하여 동일한 8×8 HEVC 코어 역변환기를 설계한 것이다. 이 코어 역변환기는 그림 5(a)와 같이 4×4 코어 역변환 (8×8 코어역변환의 짝수 부분과 동일)을 수행하는 IDCT4를 2개 사용하며, 8×8 코어 역변환의 홀수 부분을 처리하는 어레이 곱셈기인 IDCT80, 버터플라이 및 MUX 동작을 수행하는 ATU8의 세 부분으로 구성되어 있다. 그림 5(a)의 IDCT4는 그림 4(b)와 동일한 구조를 가지며 어레이 곱셈기인 SAU4를 사용하여 4×4 코어역변환의 계수인 {36,64,83}을 곱한다. 그림 5(b)는 IDCT8e 블록의 구조인데, 8×8 코어 역변환의 홀수부분 계수인 {18,50,75,89}를 곱하도록 설계되었다.

그림 5(a)에서 mode=0일 때에는 상단의 IDCT4와 하단의 IDCT4가 동작하고 중단의 IDCT8o는 동작하지 않으며, mode=1일 때에는 상단의 IDCT4와 중단의 IDCT8o가 동작하고 하단의 IDCT4는 동작하지 않는다. 따라서 [8]에 기반한 설계에서는 매 시점마다사용되고 있지 않은 유휴 하드웨어가 일부 존재하므로 제안하는 설계에 비해 하드웨어가 커지게 된다.

본 논문에서 제안한 아키텍쳐의 면적 절감 효과를 확인하기 위해 동일한 조건에서 그림 4와 그림 5의 설계를 0.18µm 공정에서 IDEC의 CAD Tool 지원을 통해 Design Vision을 사용하여 합성하고 게이트 수를 비교하였다.

Table 1. Synthesis results

표 1. 합성 결과

|             | 제안하는 구   | 기존 구조      | 이득  |

|-------------|----------|------------|-----|

|             | 조 (그림 4) | [8] (그림 5) | (%) |

| 크기 (게이트)    | 9966     | 11268      | 12  |

| 동작 속도 (MHz) | 300      | 300        | _   |

표 1은 제안하는 구조 (그림 4)와 기존 구조[8] (그림 5)의 합성 결과를 비교한 것인데, 두 설계 모두

300MHz에서 동작하여 속도는 동일하나 2-input NAND로 환산한 게이트 수는 각각 9966게이트와 11268게이트로 제안하는 구조가 12% 가량 면적을 절 감하였음을 알 수 있다.

#### Ⅳ. 결론

본 논문에서는 효과적인 HEVC 코어 역변환기 아 키텍쳐를 제안하고 이를 바탕으로 8×8 코어 역변환기 를 설계하였다. 기존의 코어 역변환기 아키텍쳐가 하 위 크기 블록을 처리하는 부분과 상위 크기 블록의 홀수 부분을 처리하는 블록을 따로따로 가지고서 번 갈아가면서 사용하는 반면에 제안하는 코어 역변환기

Fig. 4. Design of proposed inverse core transform (a) Top block (b) IDCT4 그림 4. 제안하는 코어 역변환기의 설계 (a) 최상위 블록 (b) IDCT4

Fig. 4. Design of proposed inverse core transform (cont'd) (c) IDCT80

그림 4. 제안하는 코어 역변환기의 설계 (계속) (c) IDCT8o

Fig. 5. Design of inverse core transform based on [8] (a) Top block

그림 5. [8]에 기반한 코어 역변환기의 설계 (a) 최상위 블록

Fig. 5. Design of inverse core transform based on [8] (cont'd) (b) IDCT80

그림 5. [8]에 기반한 코어 역변환기의 설계 (계속) (b) IIDCT8o

아키텍처는 이를 하나로 합쳐서 사용하기 때문에 면적을 절감할 수 있다. 제안하는 8×8 코어 역변환기 를 설계하고 합성한 결과, 기존 아키텍처와 동일한 동작 속도와 처리 능력을 가지면서도 면적을 12% 줄 일 수 있음을 확인하였다.

#### References

- [1] T. Wiegand, G. Sullivan, G. Bjontgaard, and A. Luthra, "Overview of the H.264/AVC Video Coding Standard", IEEE Transactions on Circuits and Systems for Video Technology, vol. 13, no. 7, pp. 560–576, Jul. 2003.

- [2] J. Jung and K. Lee, "Implementation of IQ/IDCT in H.264/AVC Decoder Using GP-GPU", Journal of IKEEE, vol. 14, no. 2, pp. 76-81, Jul. 2010.

- [3] G. Sullivan, J. Ohm, W. Han, and T. Wiegand, "Overview of the High Efficiency Video Coding (HEVC) Standard", IEEE Transactions on Circuits and Systems for Video Technology, vol. 22, no. 12, pp. 1649–1668, Dec. 2012.

- [4] S. Han, W. Nam, and S. Lee, "Design of Low-Area HEVC Core Transform Architecture", Journal of IKEEE, vol. 17, no. 2, pp. 119–128, Jun.

2013.

- [5] A. Fuldseth, G. Bjøntegaard, and M. Budagavi, "CE10: Core Transform Design for HEVC," JCTVC-G495, Nov. 2011.

- [6] J. Park, W. Nam, S. Han, and S. Lee, "2-D Large Inverse Transform (16x16, 32x32) for HEVC (High Efficiency Video Coding)", Journal of Semiconductor Technology and Science, vol. 12, no. 2, pp. 203–211, Jun. 2012.

- [7] M. Budagavi and V. Sze, "Unified Forward+Inverse Transform Architecture for HEVC", Proceedings of IEEE Internation Conference on ICIP, pp. 209–212, Oct. 2012.

- [8] P. Meher, S. Park, B. Mohanty, K, Lim, and C. Yeo, "Efficient Interger DCT Architecture for HEVC", to appear in IEEE Transactions on Circuits and Systems for Video Technology, 2013.

## BIOGRAPHY

#### Jong-Bae Lee (Member)

2011: BS degree in Electronic Engineering, Hanseo University. 2011~Now: MS candidate in Electronic Engineering, Soongsil University

<Main Interest> HEVC, Low-Power SoC Design,

Multimedia SoC Design, Battery Management

## Seongsoo Lee (Life Member)

1991: BS degree in Electronic Engineering, Seoul National University.

1993: MS degree in Electronic Engineering, Seoul National University.

1998 : PhD degree in Electrical

Engineering, Seoul National University.

1998~2000 : Research Associate, University of Tokyo 2000~2002 : Research Professor, Ewha Womans

University

2002 Now: Associate Professor in School of Electronic Engineering, Soongsil University <Main Interest> HEVC, Low-Power SoC Design, Multimedia SoC Design, Battery Management