# Investigation on Suppression of Nickel-Silicide Formation By Fluorocarbon Reactive Ion Etch (RIE) and Plasma-Enhanced Deposition

Hyun Woo Kim<sup>\*</sup>, Min-Chul Sun<sup>\*\*</sup>, Jung Han Lee<sup>\*</sup>, and Byung-Gook Park<sup>\*</sup>

Abstract—Detailed study on how the plasma process during the sidewall spacer formation suppresses the formation of silicide is done. In non-patterned wafer test, it is found that both fluorocarbon reactive ion etch (RIE) and TEOS plasma-enhanced deposition processes modify the Si surface so that the silicide reaction is chemically inhibited or suppressed. In order to investigate the cause of the chemical modification, we analyze the elements on the silicon surface through Auger Electron Spectroscopy (AES). From the AES result, it is found that the carbon induces chemical modification which blocks the reaction between silicon and nickel. Thus, protecting the surface from the carbon-containing plasma process prior to nickel deposition appears critical in successful silicide formation.

Index Terms—Nickel silicide, plasma-enhanced deposition, reactive ion etch, sidewall spacer

### I. INTRODUCTION

As the logic CMOS technology goes to deepsubmicron nodes beyond 100-nm, nickel silicide has attracted attention as an alternative for future nodes due to low resistivity, good sheet resistance in narrow linewidth and low Si consumption [1-8]. And, not like its precedents such as titanium and cobalt, nickel forms the least resistive silicide phase at low temperature below  $500^{\circ}$ , which makes nickel silicide formation more sensitive to the pre-treatment and the surface defects before the silicide process [9, 10]. Especially, the control of "plasma damage" during sidewall spacer formation is known to be critical to successful growth of silicide. However, whether the physical damage on the silicon lattice or the chemical effect plays a role in suppressing the silicide formation hasn't been yet clarified.

In this work, we try to analyze the details of the process by reproducing the situation that "plasma damage" suppresses silicide formation and investigating it with step-by-step non-patterned wafer test.

#### **II. EXPERIMENTAL**

For nickel silicide formation, the following processes were done in the fabrication facilities of Inter-University Semiconductor Research Center located in Seoul National University. Right after 100:1 diluted HF cleaning removed residual or native oxide from 6 inch p-type Si (100) prime wafers, 200 Å nickel was deposited using Applied Materials Endura<sup>TM</sup> Sputter System. Silicidation anneal was performed for 60 sec at 450 °C in N2 ambient using KVR-3006T RTP System of Korea Vacuum Tech. Remaining or un-reacted metal after anneal was stripped with 4:1 mixture of 98% H<sub>2</sub>SO<sub>4</sub> and 30% H<sub>2</sub>O<sub>2</sub> at 80 °C. After nickel silicide process, analysis was done by using sheet resistance, SEM and TEM image.

Manuscript received Apr. 30, 2012; revised Nov. 20, 2012.

<sup>\*</sup> Inter-University Semiconductor Research Center and Department of Electrical Engineering and Computer Science, Seoul National University, Seoul 151-744, Republic of Korea.

<sup>\*\*</sup> TD Team (S. LSI), Device Solutions Business Group, Samsung Electronics Co. Ltd., Yongin 446-711, Republic of Korea. M.-C. Sun is also with Inter-University Semiconductor Research Center and Department of Electrical Engineering and Computer Science, Seoul National University, Seoul 151-744, Republic of Korea. E-mail : hyunoo1218@naver.com

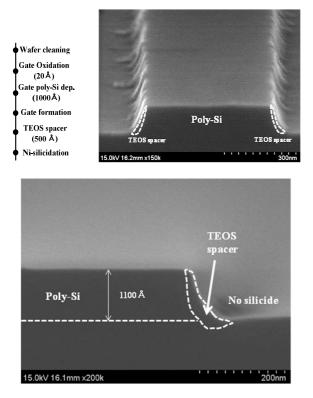

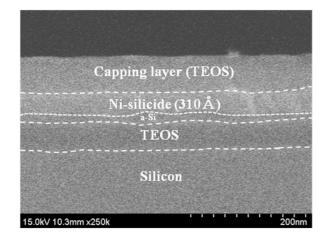

**Fig. 1.** Cross-sectional SEM image of the gate and sidewall after silicidation (No silicide is seen).

### **III. RESULTS AND DISCUSSION**

First, a situation that silicide does not properly grow after sidewall spacer formation is reproduced following the sequence shown in Fig. 1. Wafer cleaning, gate oxidation and gate poly-Si deposition are sequentially performed. Then, gate patterning is done using hydrogen bromide (HBr) gas, and sidewall spacer is formed using plasma-enhanced deposition and fluorocarbon reactive ion etch (RIE). After that, silicidation process is performed. As expected, the measured sheet resistance is unacceptably high and no nickel silicide is seen from the cross-sectional image (Fig. 1).

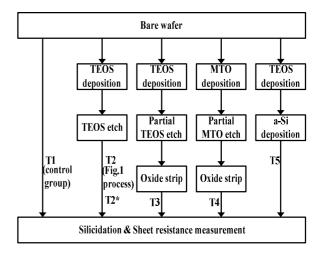

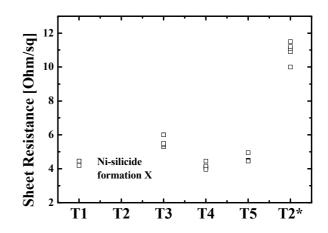

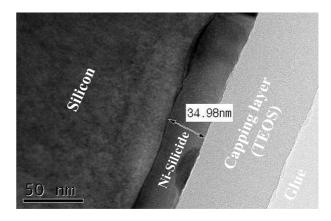

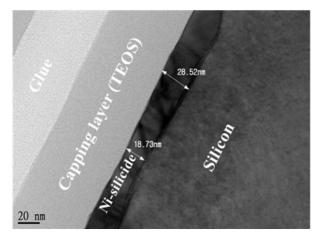

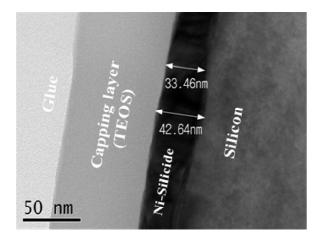

In order to understand the physics behind this phenomenon, non-patterned wafer test is designed as shown in Fig. 2. Fig. 3 shows the sheet resistances measured from each experimental group. The control nickel silicide (T1) formed on a bare wafer without any RIE or dielectric deposition steps as a reference shows sheet resistance as low as 4 ohm/sq., which indicates successful formation of silicide as shown in Fig. 4.

However, once TEOS deposition and RIE processes are performed before silicide formation (T2), no silicide

Fig. 2. Design of non-pattern wafer test (T2\*:  $O_2$ -plasma treatment).

Fig. 3. Sheet resistances measured from each experimental group.

Fig. 4. TEM image of nickel silicide on control group (T1).

is observed from the cross-section and the sheet resistance is measured very high.

**Fig. 5.** TEM image of nickel silicide after partial TEOS etching and oxide wet strip process (T3).

Fig. 6. SEM image of nickel silicide on amorphous silicon (T5).

To find out whether this occurs by RIE or deposition processes, a partial RIE sample (T3) is prepared. After the deposited TEOS is partially etched by RIE, the residual oxide is stripped off using the diluted HF solution. The reason why the residual oxide is removed using wet chemical is to only consider deposition effect without RIE effect. Sheet resistance value in Fig. 3 and TEM image in Fig. 5 show that silicide is formed on this sample. In order to understand whether the suppression of silicide formation is induced by the physical damage or chemical alteration of the surface, silicide process is done on amorphous silicon film (T5). Again, this sample shows low sheet resistance (Fig. 3) and successful silicide formation as in Fig. 6 (T5). Thus, the physical damage has no effect on silicide process. To sum up these results, the chemical modification of silicon surface by carbon-containing RIE plasma appears to be the root

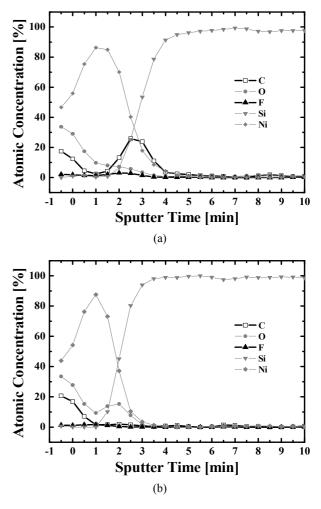

Fig. 7. Atomic concentration of each element in the depth direction from silicon surface (a) before  $O_2$ -plasma treatment, (b) after  $O_2$ -plasma treatment.

cause of the suppression mechanism. To investigate the cause of this chemical modification, we analyze the elements on the silicon surface that went through TEOS deposition and RIE processes, using PHI 700Xi Scanning Auger Nanoprobe of Physical Electronics Inc. Fig. 7 shows the atomic concentration of each element in the depth direction from silicon surface. Five elements are detected; carbon, oxygen, fluorine, silicon and nickel.

Nickel on silicon surface is used as a capping layer. By carbon-containing RIE plasma process, there is a significant amount of carbon combined with silicon on surface as shown in Fig. 7(a). From this result, carbon seems to be introduced into the silicon during RIE process, similarly to dopants of plasma doping process [11]. In nickel silicide process, it is known that the formation temperature increases as an amount of incorporated carbon increases. This is because the carbon

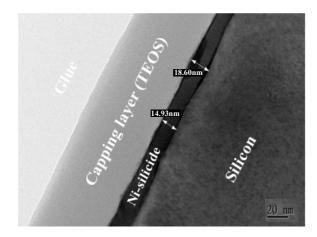

**Fig. 8.** TEM image of nickel silicide after fluorocarbon plasma etching and O<sub>2</sub>-plasma treatment process (T2\*).

**Fig. 9.** TEM image of nickel silicide after partial MTO etching and oxide wet strip process (T4).

in the Si system suppresses the nickel mono-silicide formation by making the texture of mono-silicide on the substrate unstable [12, 13]. After  $O_2$ -plasma treatment is done, these carbon elements can be removed as shown in Fig. 7(b). Thus, we can confirm that the carbon induces the chemical modification which suppresses the reaction between silicon and nickel. From this result, nickel silicide can be formed by using  $O_2$ -plasma treatment (T2\*) after TEOS deposition and RIE processes (Fig. 8).

Finally, Medium-Temperature Oxide (MTO) deposition instead of TEOS is tried to understand the effect of plasma during TEOS deposition process (T4). While the sheet resistance of TEOS group (T3) is slightly higher than that of the control group, the value of MTO group is similar to that of control group. And nickel silicide is formed well as shown in Fig. 9. This means that plasmaassisted surface modification occurs during TEOS deposition although it is not as severe as in the case of RIE.

## **III.** CONCLUSIONS

We have investigated how plasma process during sidewall formation can influence the formation of nickel silicide. Plasma-assisted surface modification is the key mechanism to suppress the reaction between nickel and silicon. From this study, we can understand either protecting the silicon surface from carbon-containing plasma or removing the plasma-modified surface is crucial to successful future silicide technology.

#### **ACKNOWLEDGMENTS**

This work was supported by the Smart IT Convergence System Research Center funded by the Ministry of Education, Science and Technology as Global Frontier Project.

## REFERENCES

- T. Ohguro et al., "Analysis of resistance behavior in Ti- and Ni-salicided polysilicon films," *IEEE Transaction on Electron Devices*, 1994, p. 2305-2317.

- [2] E. Morifuji et al., "High Performance 30 nm Bulk CMOS for 65 nm Technology Node (CMOS5)." *IEEE International Electron Devices Meeting*, 2002, pp. 655-658.

- [3] J.P. Lu et al., "A novel nickel SALICIDE process technology for CMOS devices with sub-40 nm physical gate length." *IEEE International Electron Devices Meeting*, 2002, pp. 371-374.

- [4] Qi Xiang et al., "Deep sub-100 nm CMOS with ultra low gate sheet resistance by NiSi." 2000 Symposium on VLSI Technology. Digest of Technical Papers, 2000, pp. 76-77.

- [5] A. Hokazono et al., "14 nm gate length CMOSFETs utilizing low thermal budget process with poly-SiGe and Ni salicide." *IEEE International Electron Devices Meeting*, 2002, pp. 639-642.

- [6] J.-S. Maa et al., "Effect of interlayer on thermal stability of nickel silicide." *Journal of Vaccum Science & Technology A*, vol. 19, 2001, pp. 1595-

1599.

26

- [7] H.-S. Shin et al., "Improvement of Thermal Stability of Ni-Silicide Using Vacuum Annealing on Boron Cluster Implanted Ultra Shallow Source/Drain for Nano-Scale CMOSFETs." *Journal of Semiconductor Technology & Science*, vol. 10, 2010, pp. 260-264.

- [8] M. Jang et al., "Schottky Barrier MOSFETs with High Current Drivability for Nano-regime Applications." *Journal of Semiconductor Technology & Science*, vol. 6, 2006, pp. 10-15.

- [9] R. Yang et al., "Advanced in situ pre-Ni silicide (Siconi) cleaning at 65 nm to resolve defects in NiSix modules." *Journal of Vaccum Science & Technology B*, vol. 28, 2010, pp. 56-61.

- [10] K. Kashihara et al., "Mechanism of nickel disilicide growth caused by RIE plasma-induced damage on silicon substrate." *International Workshop on Junction Technology*, 2008, pp. 154~157.

- [11] D. Lenoble et al., "The fabrication of advanced transsistors with plasma doping." *Surface and Coatings Technology*, vol. 156, 2002, pp. 262~266.

- [12] V. Machkaoutsan et al., "Improved thermal stability of Ni-silicides on Si :C epitaxial layers." *Microelectronic Engineering*, vol 84, 2007, pp. 2542~2546.

- [13] K. De Keyser et al., "Phase formation and texture of nickelsilicides on Si<sub>1-x</sub>C<sub>x</sub> epilayers." *Microelectronic Engineering*, vol 88, 2011, pp. 536-540.

Min-Chul Sun received the B.S. and M.S. degrees in 1996 and 2001 from Yonsei University and Korea Advanced Institute of Science and Technology respectively. He has been working for the Semiconductor Business Unit of Samsung

Electronics Co. Ltd. since then and is currently with Seoul National University studying toward the Ph.D. degree in electrical engineering. He participated in the IBM-Samsung Joint

Development Project at the IBM Semiconductor Research and Development Center (IBM SRDC, NY) as Front-End-Of-Line integrator for 65- and 45-nm technologies. His current research interests include the ultra-low-power multi-channel transistors, CMOScompatible nano-electronics, hybrid channel devices and advanced junction technology with the consideration of circuit design. Mr. Sun is a Student Member of the Institute of Electrical and Electronics Engineers (IEEE) and the Institute of Electronics Engineers of Korea (IEEK).

Seoul national university, Seoul, Korea. His research

current interests include nanoscale silicon devices,

single-electron transistors, quantum devices and silicon

nanowire biosensor.

Jung Han Lee (S'07) was born in Seoul, Korea, in 1981. He received the B.S. degree in physics department from Korea University, Korea, in 2007. He is currently working toward the Ph.D. degree in nano-science and technology at

Hyun Woo Kim received the B.S degrees in 2008 from Kyung-pook National University (KNU) and the M.S. degrees from Seoul National University in 2010. He is currently working toward the Ph.D. degree in Electrical Engineering at Seoul

National University (SNU), Seoul, Korea. His research interest is Tunnel FET with nickel silicide. Mr. Kim is currently a Student Member of the Institute of Electronics Engineers of Korea (IEEK).

**Byung-Gook Park** received his B.S. and M.S. degrees in Electronics Engineering from Seoul National University (SNU) in 1982 and 1984, respectively, and his Ph. D. degree in Electrical Engineering from Stanford University in 1990. From 1990 to

1993, he worked at the AT&T Bell Laboratories, where he contributed to the development of 0.1 micron CMOS and its characterization. From 1993 to 1994, he was with Texas Instruments, developing 0.25 micron CMOS. In 1994, he joined SNU as an assistant professor in the Department of Electrical Engineering and Computer Science, where he is currently a professor. In 2002, he worked at Stanford University as a visiting professor, on his sabbatical leave from SNU. He led the Interuniversity Semiconductor Research Center (ISRC) at SNU as the director from June 2008 to 2010. His current research interests include the design and fabrication of nanoscale CMOS, flash memories, silicon quantum devices and organic thin film transistors. He has authored and co-authored over 800 research papers in journals and conferences, and currently holds 53 Korean and 22 U.S. patents. He has served as a committee member on several international conferences, including Microprocesses and Nanotechnology, IEEE International Electron Devices Meeting, International Conference on Solid State Silicon Devices and Materials, and IEEE Nanoelectronics Workshop (technical program chair in 2005, general chair in 2007). He is currently serving as an executive director of Institute of Electronics Engineers of Korea (IEEK) and the board member of IEEE Seoul Section. He received "Best Teacher" Award from SoEE in 1997, Doyeon Award for Creative Research from ISRC in 2003, Educational Award from College of Engineering, SNU, in 2006, and Haedong Research Award from IEEK in 2008.