# Asymmetric Cascaded Multi-level Inverter: A Solution to Obtain High Number of Voltage Levels

## M. R. Banaei<sup>†</sup> and E. Salary\*

Abstract – Multilevel inverters produce a staircase output voltage from DC voltage sources. Requiring great number of semiconductor switches is main disadvantage of multilevel inverters. The multilevel inverters can be divided in two groups: symmetric and asymmetric converters. The asymmetric multilevel inverters provide a large number of output steps without increasing the number of DC voltage sources and components. In this paper, a novel topology for multilevel converters is proposed using cascaded sub-multilevel Cells. This sub-multilevel converters can produce five levels of voltage. Four algorithms for determining the DC voltage sources magnitudes have been presented. Finally, in order to verify the theoretical issues, simulation is presented.

Keywords: Voltage Levels, Asymmetric state, H-bridge cascaded.

#### 1. Introduction

Multilevel inverters produce a stepped output phase voltage with a refined harmonic profile when compared to a two-level inverter [1, 2]. The concept of multilevel inverters, introduced about 30 years ago [1], entails performing power conversion in multiple voltage steps to obtain improved power quality, lower switching losses, better electromagnetic compatibility, and higher voltage capability. Nowadays, there exist three commercial topologies of multilevel voltage source inverters: the most popular being the diode-clamped [3, 4], flying capacitor [5, 6] and cascaded H-bridge [7-9] structures. Among these inverter topologies, cascaded multilevel inverter reaches the higher output voltage and power levels, and the higher reliability due to its modular topology and the simplicity [10].

Among these inverter topologies, the cascaded H-bridge multilevel inverters require the least number of total main components. One aspect which sets the cascaded H-bridge apart from other multilevel inverters is the capability of utilizing different DC voltages on the individual H-bridge cells which results in splitting the power conversion and asymmetrical multilevel inverters can be obtained [8, 9]. To provide a large number of output steps without increasing the number of DC voltage sources, asymmetric multilevel converters can be used. The cascaded H-bridge can operate as symmetric or asymmetric converter. In asymmetric multilevel converters the DC voltage sources are proposed to be chosen as different value according to different methods [11-13].

Recently, several multilevel inverter topologies have

Received: March 19, 2012; Accepted: September 20, 2012

been developed for cascaded multilevel inverters. Novel topologies of cascaded multilevel inverters using a reduced number of switches and gate driver circuits are presented in recent years [14-18]. In [14, 15] novel configuration of cascaded multilevel inverters have been proposed. The suggested topologies need fewer switches and gate driver circuits but they require multiple DC sources and some switches of suggested topologies have high peak inverse voltage. The proposed inverter in [14] can be used as symmetric and asymmetric converter and three algorithms for determination of magnitudes of DC voltage sources have been presented but in asymmetric converter it has some limitations. In asymmetric state to obtain uniform step voltage it can not be used from Trinary algorithm for determination of magnitudes of DC voltage sources. It can not perform difference operation among DC sources. In order to increase the steps in the output voltage, a new topology has been recommended in [17], which benefits from a series connection of sub-multilevel converters. In [18], the optimal structures for this topology are investigated for various objectives such as minimum number of switches and DC voltage sources and minimum standing voltage on the switches for producing the maximum output voltage levels [18]. These topologies require multiple DC sources and bi-directional switches. Although these topologies need a less number of bi-directional switches but need great number of IGBTs.

Operations of multilevel inverters depend on modulation strategies. There are several modulation strategies for multilevel inverters.

#### 2. Presented Topology in [15]

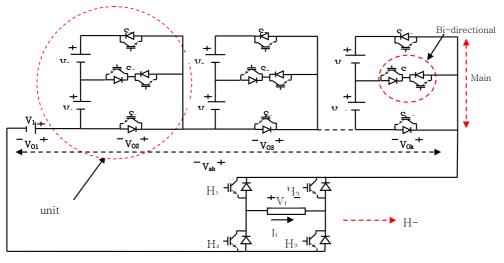

Fig. 1 shows proposed structure in [15]. The basic unit for the multilevel converter presented in [15], is illustrated in Fig. 1. This consists of two DC voltage sources (with a

<sup>†</sup> Corresponding Author: Electrical Engineering Department, Faculty of Engineering, Azarbaijan Shahid Madani University, Tabriz, Iran. (m.banaei@ azaruniv. edu)

<sup>\*</sup> Electrical Engineering Department, Faculty of Engineering, Azarbaijan Shahid Madani University, Tabriz, Iran.

Fig. 1. Proposed structure in [15].

voltage equal to  $V_{dc}$ ) two unidirectional switches and a bidirectional switch. The basic unit shown in Fig. 1 can be extended. If *n* dc voltage sources are used in the extended unit as shown in Fig. 1, then the number of output voltage levels (*S*) and switches ( $N_{sw}$ ) are given by the following equations, respectively [15]:

$$S = 2n + 1 \tag{1}$$

$$N_{sw} = \frac{3S+7}{4} \quad n \text{ is odd} \tag{2}$$

$$N_{sw} = \frac{3S+9}{4} \quad n \text{ is even} \tag{3}$$

The suggested topology [15] operates in symmetric state and some switches (H-bridge) of suggested topology have high peak inverse voltage.

#### 3. Cascaded Sub-Multilevel Cells

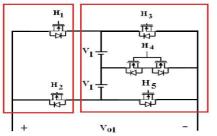

If two switches are added to basic recommended unit in [15], a new sub-multilevel inverter is obtained. Fig. 2 shows the suggested sub-multilevel inverter. This consists of two DC voltages equal to  $V_1$  and five switches. The main advantages of the proposed converter are doubling

added switches basic recommended unit in [15]

Fig. 2. Suggested sub-multilevel inverter.

the output voltage levels. Table 1 indicates the values of  $V_{o1}$  for states of switches. The sub-multilevel inverter can generate five voltage output levels.

Table 1. Values of  $V_{O1}$  for states of switches.

| Level   | ON switches                   |

|---------|-------------------------------|

| 0       | $H_2 H_5 \text{ or } H_1 H_3$ |

| $V_1$   | $H_2H_4$                      |

| $2V_1$  | $H_2 H_3$                     |

| $-V_1$  | $H_1 H_4$                     |

| $-2V_1$ | $H_1 H_5$                     |

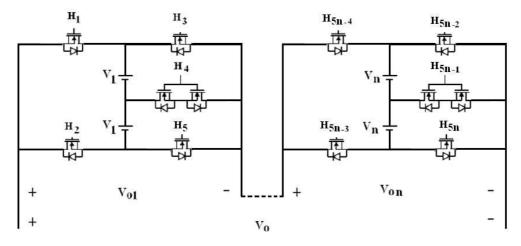

This topology achieves reduction in the number of switches required, using only five switches while in any of the other three famous configurations (H-bridge cascaded, diode clamped and flying capacitor multilevel inverters) to generation of five levels eight switches are needed. The basic unit shown in Fig. 2 can be extended as shown in Fig. 3. Fig. 3 shows the circuit topology of the proposed inverter that is called Cascaded Sub-Multilevel Cells. DC voltage sources are independent each other, and value of them could be determined by different methods. In the other hand the Cascaded Sub-Multilevel Cells structure can operates as symmetric and asymmetric multilevel inverter.

The Cascaded Sub-Multilevel Cells requires unidirectional and bi-directional switches. The unidirectional switches have been made of common emitter anti-parallel MOSFET with diode. The bi-directional switches with capability of blocking voltage and conducting current in both directions are needed in Cascaded Sub-Multilevel Cells structure. There are several arrangement can be used to create such a bi-directional switch. The common drain anti-parallel MOSFET with diode pair arrangement shown in Fig. 1 has been used in this paper. This bi-directional switch arrangement consists of two diodes and two MOSFET. Each switch requires one gate driver. Each switch in the inverters requires an isolated driver circuit. The isolation

Fig. 3. Circuit topology of the proposed inverter.

can be given using either pulse transformers or optoisolators [14]. The reliability of a multilevel inverter is proportional to the number of its components. Clamping diodes and balancing capacitors are not needed in the Cascaded Sub-Multilevel Cells. Another advantage of the Cascaded Sub-Multilevel Cells is circuit layout flexibility and modularized circuit layout and packaging is possible in it same as H-bridge cascaded topology. The number of output voltage levels can be easily adjusted by changing the number of sub-multilevel inverters.

#### 4. Switching Algorithm

Several modulation strategies have been proposed for multilevel inverters. The modulation methods used in multilevel inverters can be classified according to switching frequency [19-25]. In this paper, the fundamental frequency switching technique has been used but in this paper calculation of optimal switching angles and minimizing total harmonic distortion (THD) is not the final goal. The advantageous of the fundamental frequency switching method is its low switching frequency compared to the other control methods [25]. The modulation of the

$V_{dc}$   $V_{dc}$  V

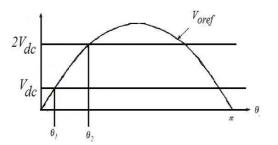

Fig. 4. A generalized quarter wave, symmetric, stepped voltage waveform.

Cascaded Sub-Multilevel Cells is to choose a series of switching angles to combine separate elements into a single unit as desired sinusoidal voltage waveform. Fig. 4 shows a generalized quarter wave, symmetric, staircase voltage waveform synthesized by a 2s + 1 level inverter, where s is the number of switching angles.

For uniform step waveform, the Fourier series expansion of the output voltage waveform using the fundamental frequency switching scheme shown in Fig. 5 is given by:

$$V_{O}(\omega t) = \sum_{p=1,3,\dots}^{\infty} \frac{4V_{dc}}{p\pi} (\cos(p\theta_{1}) + \cos(p\theta_{2}) + \dots + \cos(p\theta_{s}))\sin(\omega t)$$

(4)

The switching angles can be found by solving the following equations:

$$\begin{array}{c}

\cos(\theta_1) + \cos(\theta_2) + \dots + \cos(\theta_s) = m\\ \cos(3\theta_1) + \cos(3\theta_2) + \dots + \cos(3\theta_s) = 0\\ \vdots\\ \cos(p\theta_1) + \cos(p\theta_2) + \dots + \cos(p\theta_s) = 0\end{array}\right\}$$

(5)

where  $m = \frac{\pi V_1}{4V_{dc}}$  and the modulation index m<sub>a</sub> is given by

$m_a = m/s$ . Here V<sub>1</sub> is magnitude of fundamental harmonic. For example, to control the fundamental amplitude and to eliminate harmonics in the five-level inverter, two nonlinear equations can be set up as follows:

$$\cos(\theta_1) + \cos(\theta_2) = m$$

$$\cos(3\theta_1) + \cos(3\theta_2) = 0$$

Different algorithm such as iterative method and artificial neural networks can be used to solving the set of nonlinear equation.

In the simple method the switching angles can be found by solving the following equation:

$$\theta_s = \sin^{-1}(\frac{sV_{dc}}{V_{peak}}) \tag{6}$$

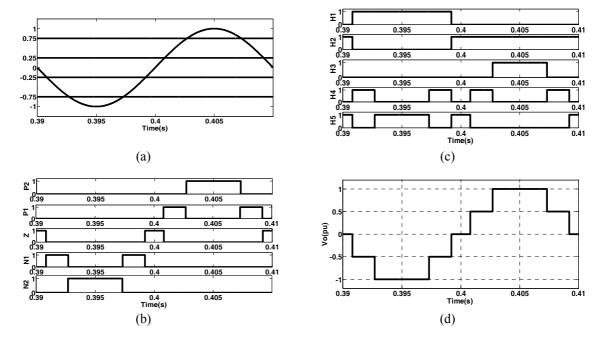

where  $V_{\text{peak}}$  is the peak value of the reference voltage. The frequency of output voltage is the same as frequency of sine reference wave. Fig. 5 show the basic concept of the conduction angle determination. In this figure half cycle of sine reference wave has been shown. Operation of five-level Cascaded Sub-Multilevel Cells is shown in Fig. 6. Modulation waveforms to switching are shown in Fig. 6(a). At each instant, the result of the comparison is decoded in order to generate the correct switching function corresponding to a given output voltage level. The switching pulses are shown in Fig. 6(b). In Fig. 6(b), Z indicates to zero level, P<sub>1</sub> and P<sub>2</sub> indicate to positive levels and N<sub>1</sub> and N<sub>2</sub> indicate to negative levels. Switching pulses

Fig. 5. Basic concept of the conduction angle determination.

produce input gate signals of switches that are shown in Fig. 6(c). The output voltage of this example is shown in Fig. 6(d).

### 5. Operational Principle of the Cascaded Sub-Multilevel Cells

The operational principle of the Cascaded Sub-Multilevel Cells is to generate five level output voltage by each sub-multilevel inverter.

The output phase voltage is obtained by summing the output voltage of sub-multilevel inverters as the following:

$$V_{O} = V_{O1} + V_{O2} + \dots + V_{On}$$

(7)

If all DC voltage sources in Fig. 1 are equal to  $\frac{V_{dc}}{2}$  $(V_1 = V_2 = ... = V_n = \frac{V_{dc}}{2})$ , the inverter is then known as symmetric multilevel inverter. The number of output voltage levels (S) in symmetric multilevel inverter may be related to the number of sub-multilevel inverters (*n*) by:

$$S = 4n + 1 \tag{8}$$

The maximum output voltage for this topology is obtained by summing the DC voltage sources and it  $(V_{O \max})$  is:

Fig. 6. Operation of five- level Cascaded Sub-Multilevel Cells topology (a) modulation signals (b) Switching pulses (c) gates signals (d) output phase voltage.

$$V_{O\max} = n \frac{V_{dc}}{2} \tag{9}$$

To provide a large number of output levels without increasing the number of components, asymmetric multilevel inverters can be used. The DC voltage sources are proposed to be chosen according to a geometric progression with a factor of two (Binary) or three (Trinary) in cascaded H-bridge inverters [8, 11-14]. The Cascaded Sub-Multilevel Cells can be used as asymmetric multilevel inverters and Binary or Trinary methods can be used to choose value of DC voltage sources. In the following, we propose three methods for determination value of DC voltage sources for n cascaded sub-multilevel inverters. Existence of different algorithm to determine value of DC voltage sources gives flexibility to multilevel inverter and freedom action for designer.

In Binary and Trinary methods, the values of DC voltage sources are chosen according to the following equations:

$$V_i = (2^{i-1}) \frac{V_{dc}}{2}, \quad i = 1, 2, ..., n$$

(10)

$$V_i = (3^{i-1}) \frac{V_{dc}}{2}, \quad i = 1, 2, ..., n$$

(11)

In third method the DC voltage sources are suggested to be chosen according to the following algorithm:

$$V_i = (5^{i-1}) \frac{V_{dc}}{2}, \quad i = 1, 2, ..., n$$

(12)

For n cascaded sub-multilevel inverters, the effective number of output voltage levels and maximum output voltages are given by Table 2. The total numbers of components needed in these four methods are totally different at higher voltage levels.

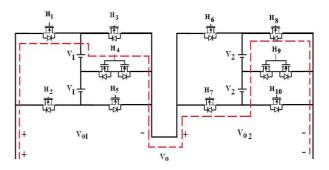

Fig. 7 shows an example of novel multilevel inverter that consists of two sub-multilevel inverters. If the suitable values for DC voltage sources are selected and proper switching are used, then output voltage levels between  $+2(V_1+V_2)$  and  $-2(V_1+V_2)$  can be obtained. These levels are:

$$\begin{array}{cccc} 0, \pm V_1, \ \pm V_2, \ \pm 2V_1, \ \pm 2V_2, \ \pm (V_1 \pm V_2), \ \pm (2V_1 \pm V_2), \\ \pm (V_1 \pm 2V_2) \ \text{and} \ \pm 2(V_1 \pm V_2) \end{array}$$

The maximum output voltage of this new topology is  $2(V_1 + V_2)$ . The different modes of the Cascaded Sub-Multilevel Cells topology shown in Fig. 4 are demonstrated in Table 3. Note that different switching patterns for producing the zero level exist and in Table 3 only two patterns of them is shown. A current path to obtain  $V_1 - 2V_2$  level has shown in Fig. 7.

Table 2. Output voltage levels and maximum output voltages.

|              | voltage levels         | $V_{O \max}$                        |

|--------------|------------------------|-------------------------------------|

| Symmetric    | 4 <i>n</i> +1          | $(2n)\frac{V_{dc}}{2}$              |

| Binary       | $2^{n+2} - 3$          | $(2^{n+1}-1)\frac{V_{dc}}{2}$       |

| Trinary      | $2(3^n - \frac{1}{2})$ | $(3^n-1)\frac{V_{dc}}{2}$           |

| Third method | 5 <i>n</i>             | $(\frac{5^n-1}{2})\frac{V_{dc}}{2}$ |

Fig. 7. Novel multilevel inverter with two sub-multilevel inverters.

Table 3. Different output voltage modes of Cascaded Sub-Multilevel Cells.

| On Switches                                        | Vo              | On Switches                                                | Vo              |

|----------------------------------------------------|-----------------|------------------------------------------------------------|-----------------|

| $H_{2}H_{4}H_{6}H_{8}$                             | $V_1$           | $H_{1}H_{4} \ H_{7} \ H_{10}$                              | $-V_1$          |

| ${ m H}_2  { m H}_3  { m H}_6  { m H}_8$           | $2V_1$          | $H_{1}H_{5}H_{7}H_{10}$                                    | $-2V_{1}$       |

| ${ m H_{1}}{ m H_{3}}{ m H_{7}}{ m H_{9}}$         | $V_2$           | ${\rm H}_{2}{\rm H}_{5}{\rm H}_{6}{\rm H}_{9}$             | $-V_2$          |

| $H_{1}H_{3}H_{7}H_{8}$                             | $2V_2$          | $H_2H_5H_6H_{10}$                                          | $-2V_{2}$       |

| H2 H4 H7 H9                                        | $V_{1} + V_{2}$ | $H_1H_4H_6H_9$                                             | $-V_{1}-V_{2}$  |

| $H_2 \ H_4 \ H_6 \ H_9$                            | $V_{1} - V_{2}$ | $H_{1}H_{4}H_{7}H_{9}$                                     | $-V_{1}+V_{2}$  |

| ${ m H}_2 \ { m H}_3 \ { m H}_7 \ { m H}_9$        | $2V_1 + V_2$    | $H_1  H_5  H_6  H_9$                                       | $-2V_{1}-V_{2}$ |

| ${ m H}_2  { m H}_3  { m H}_6  { m H}_9$           | $2V_1 - V_2$    | $\mathrm{H}_{1}\mathrm{H}_{5}\mathrm{H}_{7}\mathrm{H}_{9}$ | $-2V_1 + V_2$   |

| $\mathrm{H}_2\mathrm{H}_4\mathrm{H}_7\mathrm{H}_8$ | $V_1 + 2V_2$    | $H_{1}H_{4}H_{6}H_{10}$                                    | $-V_1 - 2V_2$   |

| ${\rm H}_2  {\rm H}_4  {\rm H}_6  {\rm H}_{10}$    | $V_1 - 2V_2$    | $H_{1}H_{4}H_{7}H_{8}$                                     | $-V_1 + 2V_2$   |

| ${\rm H}_2{\rm H}_3{\rm H}_7{\rm H}_8$             | $2V_1 + 2V_2$   | $H_{1}H_{5}H_{6}H_{10}$                                    | $-2V_1 - 2V_2$  |

| ${\rm H}_2  {\rm H}_3  {\rm H}_6  {\rm H}_{10}$    | $2V_1 - 2V_2$   | $H_1 \ H_5 \ H_7 \ H_8$                                    | $-2V_1 + 2V_2$  |

| ${\rm H_{1}}{\rm H_{3}}{\rm H_{6}}{\rm H_{8}}$     | 0               | $H_2 H_5 H_7 H_{10}$                                       | 0               |

Depending on the availability of DC sources, the voltage levels are not limited to a specific ratio. By using DC sources with different value in any unit, more levels can be created in the output voltage, but this paper is focused on a general design principle of a uniform step multilevel inverter, with n series-connected sub-multilevel inverters per phase.

Although this topology requires multiple DC sources, it may be available in some systems such as photovoltaic panels, fuel cells and DC battery which can generate DC voltage sources.

#### 6. Comparison Study

In comparison with the traditional two-level converters and by increasing the number of voltage levels, the small voltage levels to the generation of high power quality waveforms, lower harmonic components, lower voltage ratings of components, lower switching losses, reduction of dv/dt stresses on the load and gives the possibility of working with low speed semiconductor switches [28, 29]. The main disadvantage associated with the multilevel inverters is requiring a great number of semiconductor switches. Each switch in the inverter requires an isolated driver circuit. The isolated driver circuits need separate isolated power supply for each semiconductor switch. Hence the reliability of a multilevel inverter is proportional to the number of its components.

In comparison among the most popular multilevel inverters and Cascaded Sub-Multilevel Cells we can say: Clamping diodes are not required in the flying capacitor, cascaded H-bridge and Cascaded Sub-Multilevel Cells while balancing capacitors are not needed in the diodeclamped, cascaded H-bridge and Cascaded Sub-Multilevel Cells. Cascaded H-bridge and Cascaded Sub-Multilevel Cells requires multiple DC sources. Table 4 compares the main power component requirements per phase leg among these four multilevel inverters in symmetric state, where S is the number of voltage levels. In Table 4, the number of main switches needed by each inverter to achieve the same number of voltage levels is the same except for the Cascaded Sub-Multilevel Cells. The Cascaded Sub-Multilevel Cells thirteen-level inverter, for example, requires 15 main switches, while the other multilevel inverters need 24 switches.

Among the mature multilevel inverters, the cascaded Hbridge multilevel inverter requires the least number of components to achieve the same number of output voltage levels. With its modularized structure, it can flexibly expand the output power capability and is favorable to manufacturing so to probe the reduction in component numbers achieved by new configuration; comparison between cascaded topology and new multilevel in asymmetric state is shown.

Operation of Cascaded Sub-Multilevel Cells in asymmetric state is the same as cascade H-bridge inverter but in the cascade H-bridge one DC source exists in Hbridge unit while in the Cascaded Sub-Multilevel Cells two DC sources exist in sub-multilevel inverter. In the other hands one DC source divided two DC sources and sum of DC sources values in Cascaded Sub-Multilevel Cells is equal to one DC source value in cascade H-bridge inverter. Table 5 shows comparison of the number of switches (No. of sw) between Cascaded Sub-Multilevel Cells in this paper with the cascade H-bridge in asymmetric states for some cases in production S level voltage.

Another situation that requires a solution in inverters is the ratings of semiconductor switches. In other word, voltage and current ratings of the switches in a multilevel inverter have important function on the cost and realization of the inverter. The currents of all switches are proportional with the rated current of the load but this is not the case for the voltage rating of the switches. In multilevel inverters the voltage rating of the switches or peak inverse voltage (PIV) of switches are proportional with the value of DC sources or DC buses and structure of inverter. To provide a large number of output levels without increasing the number of switches, asymmetric multilevel inverters can be used but the voltage rating of the switches is bigger than symmetric multilevel inverters when both groups produce same voltage value. In suggested sub-multilevel inverter that is shown in Fig. 2 two groups of switches exist.

PIV of unidirectional switches is the same as cascade Hbridge switches but PIV of bi-directional switches is half of other switches PIV. In comparison between cascade Hbridge and Cascaded Sub-Multilevel Cells, symmetric state is compared with symmetric state and asymmetric state with asymmetric state.

In the third algorithm to selection DC sources value the voltage rating of the switches is bigger than other states but asymmetric multilevel inverter with this algorithm can produce larger number of levels than other states.

Table 4. Comparison of power component requirement in symmetric state.

| Inverter               | Diode-<br>clamped | Flying capacitor       | Cascaded<br>H-bridge | Cascaded Sub-<br>Multilevel Cells |

|------------------------|-------------------|------------------------|----------------------|-----------------------------------|

| Main<br>Switches       | 2(S-1)            | 2(S-1)                 | 2(S-1)               | $\frac{5(S-1)}{4}$                |

| DC Source<br>(DC bus)  | S-1               | S-1                    | $\frac{S-1}{2}$      | $\frac{S-1}{2}$                   |

| Clamping<br>Diode      | 2(S-1)            | 0                      | 0                    | 0                                 |

| Balancing<br>Capacitor | 0                 | $\frac{(S-1)(S-2)}{2}$ | 0                    | 0                                 |

Table 5. Comparison of main switches requirement between cascade H-bridge and Cascaded Sub-Multilevel Cells.

|    | Biı          | nary |                                      |          | Trii         | nary                                                    |              | Fifnary  |                                     |

|----|--------------|------|--------------------------------------|----------|--------------|---------------------------------------------------------|--------------|----------|-------------------------------------|

| Ca | scaded       | Mu   | scaded<br>Sub-<br>ıltilevel<br>Cells | Cascaded |              | Cascaded<br>Cascaded<br>Cascaded<br>Multilevel<br>Cells |              | S<br>Mul | scaded<br>Sub-<br>Itilevel<br>Cells |

| S  | No. of<br>sw | S    | No. of<br>sw                         | S        | No. of<br>sw | S                                                       | No. of<br>sw | S        | No. of<br>sw                        |

| 7  | 8            | 13   | 10                                   | 9        | 8            | 17                                                      | 10           | 25       | 10                                  |

| 15 | 12           | 29   | 15                                   | 27       | 12           | 53                                                      | 15           | 125      | 15                                  |

Reduction of dv/dt stresses on the load is one of the advantageous of multilevel inverters. By using Cascaded Sub-Multilevel Cells the dv/dt stresses on the load is less than cascade H-bridge inverter because in the cascade H-bridge one DC source exists in H-bridge unit while in the Cascaded Sub-Multilevel Cells two DC sources exist in sub-multilevel inverter. In design inverter with 1000 V

maximum voltage when number of H-bridge cells in cascaded H-bridge and sub-multilevel inverters in Cascaded Sub-Multilevel Cells is the same, for example, cascaded H-bridge requires four DC sources with 250 V value and voltage steps is 250 V, while the Cascaded Sub-Multilevel Cells need eight DC sources with 125 V value and voltage steps is 125 V. So by using of Cascaded Sub-Multilevel Cells dv/dt stresses on the load is half of state that load is fed by cascade H-bridge. The two main components of the power losses in a switch are conduction losses and switching losses. Always, in each sub-multilevel inverter, a set of two switches is on at any given time. In design nine-level symmetrical multilevel inverters, for example, eight switches are on at any given time in cascaded H-bridge, while the Cascaded Sub-Multilevel Cells need four switches to generate one level so Cascaded Sub-Multilevel Cells has less on-state voltage drop and conduction losses of switches.

#### 7. Simulation Results

In order to verify the validity of the proposed multilevel inverter in the generation of a desired output voltage, a prototype is simulated based on the suggested topology according to that one shown in Fig. 2 and 4. The MATLAB software has been used for simulation. The system parameters in simulation are listed in Table 6.

Table 6. Simulation study parameters.

|        | Nominal<br>frequency | R-L Load                      | DC sources |

|--------|----------------------|-------------------------------|------------|

| values | 50HZ                 | $70 \Omega$ , $55 \text{ mH}$ | 120V       |

#### 6.1. Symmetric state

In the first simulation all DC voltage sources are the same. The magnitude of each voltage sources is considered 25 V ( $V_1 = V_2 = \frac{V_{dc}}{2} = 25$  V). This structure generates nine voltage levels in each output phase. Table 7 shows the ON switches lookup table of nine-level multilevel inverter. It is important to note that there are different switching patterns for producing the voltage levels. Fig. 8(a) and 8(b) reveal the output voltage, respectively.

Table 7. Look-up table of a single-phase nine-level inverter.

| On Switches                                    | Vo  | On Switches                                     | Vo   |

|------------------------------------------------|-----|-------------------------------------------------|------|

| ${\rm H}_{2}{\rm H}_{4}{\rm H}_{6}{\rm H}_{8}$ | 30  | ${\rm H}_{1}{\rm H}_{4}{\rm H}_{7}{\rm H}_{10}$ | -30  |

| ${ m H}_{2}{ m H}_{3}{ m H}_{6}{ m H}_{8}$     | 60  | ${ m H}_{1}{ m H}_{5}{ m H}_{7}{ m H}_{10}$     | -60  |

| ${ m H}_{2}{ m H}_{3}{ m H}_{7}{ m H}_{9}$     | 90  | ${ m H}_{1}{ m H}_{5}{ m H}_{6}{ m H}_{9}$      | -90  |

| ${\rm H}_{2}{\rm H}_{3}{\rm H}_{7}{\rm H}_{8}$ | 120 | ${\rm H}_{1}{\rm H}_{5}{\rm H}_{6}{\rm H}_{10}$ | -120 |

| ${ m H_1}  { m H_3}  { m H_6}  { m H_8}$       | 0   | $H_2 H_5 H_7 H_{10}$                            | 0    |

Fig. 8. Nine-level multilevel inverter: (a) output phase voltage; (b) harmonic spectrum of load voltage.

Another set of waveforms for a 9-level inverter are shown in Fig. 9. In this state, the switching angles are selected to eliminate or weak  $3^{rd}$ ,  $5^{th}$  and  $7^{th}$  harmonics at  $m_a=0.6125$ . This figure shows ability of proposed converter in selective harmonic elimination.

**Fig. 9.** (a) Output voltage, (b) corresponding FFT of 9 level inverter for 3<sup>rd</sup>, 5<sup>th</sup> and 7<sup>th</sup> harmonics elimination

#### 6.2. Asymmetric state

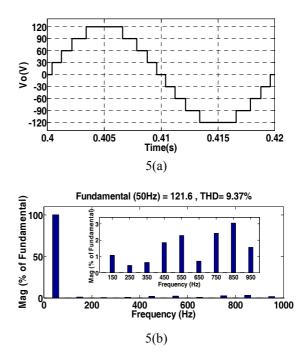

Fifnary algorithm is chosen to show Cascaded Sub-Multilevel Cells capability in operation at asymmetric states. If the DC voltage sources in the Cascaded Sub-Multilevel Cells are chosen as  $V_1 = 10$  V and  $V_2 = 50$  V, this circuit can generate twenty five level voltages. Table 8 shows the ON switches lookup table of twenty five-level multilevel inverter. The output voltage waveform and harmonic spectrum of load voltage are shown in Fig. 10(a) and 10(b), respectively.

Table 8. Look-up table of a single-phase twenty five-level inverter.

| On Switches                                     | V <sub>0</sub> (V) | On Switches                                     | $V_0(V)$ |

|-------------------------------------------------|--------------------|-------------------------------------------------|----------|

| ${\rm H}_{2}{\rm H}_{4}{\rm H}_{6}{\rm H}_{8}$  | 10                 | ${ m H}_{1}{ m H}_{4}{ m H}_{7}{ m H}_{10}$     | -10      |

| ${\rm H}_{2}{\rm H}_{3}{\rm H}_{6}{\rm H}_{8}$  | 20                 | ${\rm H}_{1}{\rm H}_{5}{\rm H}_{7}{\rm H}_{10}$ | -20      |

| ${\rm H}_{1}{\rm H}_{3}{\rm H}_{7}{\rm H}_{9}$  | 30                 | ${ m H}_{2}{ m H}_{5}{ m H}_{6}{ m H}_{9}$      | -30      |

| ${\rm H}_{1}{\rm H}_{3}{\rm H}_{7}{\rm H}_{8}$  | 40                 | ${\rm H}_{2}{\rm H}_{5}{\rm H}_{6}{\rm H}_{10}$ | -40      |

| ${ m H}_{2}{ m H}_{4}{ m H}_{7}{ m H}_{9}$      | 50                 | ${ m H}_{1}{ m H}_{4}{ m H}_{6}{ m H}_{9}$      | -50      |

| ${\rm H}_{2}{\rm H}_{4}{\rm H}_{6}{\rm H}_{9}$  | 60                 | ${ m H}_{1}{ m H}_{4}{ m H}_{7}{ m H}_{9}$      | -60      |

| ${\rm H}_{2}{\rm H}_{3}{\rm H}_{7}{\rm H}_{9}$  | 70                 | ${ m H}_{1}{ m H}_{5}{ m H}_{6}{ m H}_{9}$      | -70      |

| ${ m H}_{2}{ m H}_{3}{ m H}_{6}{ m H}_{9}$      | 80                 | ${ m H}_{1}{ m H}_{5}{ m H}_{7}{ m H}_{9}$      | -80      |

| ${\rm H}_{2}{\rm H}_{4}{\rm H}_{7}{\rm H}_{8}$  | 90                 | ${\rm H}_{1}{\rm H}_{4}{\rm H}_{6}{\rm H}_{10}$ | -90      |

| ${\rm H}_{2}{\rm H}_{4}{\rm H}_{6}{\rm H}_{10}$ | 100                | ${ m H}_{1}{ m H}_{4}{ m H}_{7}{ m H}_{8}$      | -100     |

| $H_{2}H_{3}H_{7}H_{8}$                          | 110                | ${\rm H}_{1}{\rm H}_{5}{\rm H}_{6}{\rm H}_{10}$ | -110     |

| $H_{2}H_{3}H_{6}H_{10}$                         | 120                | $H_{1}H_{5}H_{7}H_{8}$                          | -120     |

| ${ m H_1} \ { m H_3} \ { m H_6} \ { m H_8}$     | 0                  | ${ m H}_2 \ { m H}_5 \ { m H}_7 \ { m H}_{10}$  | 0        |

6(b)

**Fig. 10.** Twenty five-level multilevel inverter (a) output phase voltage and (b) harmonic spectrum of load voltage.

The inverter can output twenty five-level voltages per phase with the fewest components. Total harmonic distortion (THD) of output voltage is as low as 5%. It can be observed from the harmonic spectrum of voltages that, presented topology is effective to meet low harmonic level.

#### 8. Conclusions

Multilevel converters are very interesting for high voltage applications, energy conversion and considerably improve the output voltage quality. This paper has proposed a new topology of the cascaded converter called Cascaded Sub-Multilevel Cells. The main advantages of the Cascaded Sub-Multilevel Cells are:

- improve the output voltage quality

- reduced number of switching devices

- operates in symmetric an asymmetric states

- existence of different algorithms for calculating of magnitudes of DC voltage sources and freedom action to designer for design multilevel inverter

- · small on-state voltage drop and conduction losses

- reduction of dv/dt stresses on the load

Four procedures for calculating of magnitudes of DC voltage sources have been presented. These procedures give freedom action to designer for design multilevel inverter. Comparison between the conventional topologies of multilevel inverters and the proposed multilevel inverter is shown in this paper and simulation results exhibit the good performance and feasibility of the proposed topology.

#### References

- A. Nabe, I. Takahashi, and H. Akagi, "A new neutralpoint clamped PWM inverter", *in Proceeding of IEEE Industry Applications Society Conference*, pp. 761-766, 1980.

- [2] J. S. Lai and F. Z. Peng, "Multilevel converters—A new breed of power converters", *IEEE Trans. Ind. Appl.*, Vol. 32, No. 3, pp. 509-517, May/Jun. 1996.

- [3] D. Krug, S. Bernet, S. S. Fazel, K. Jalili, and M. Malinowski, "Comparison of 2.3-kV medium-voltage multilevel converters for industrial medium-voltage drives", *IEEE Trans. Ind. Electron.*, Vol. 54, No. 6, pp. 2979-2992, 2007.

- [4] Y. Cheng, C. Qian, M. L. Crow, S. Pekarek, and S. Atcitty, "A comparison of diode-clamped and cascaded multilevel converters for a STATCOM with energy storage", *IEEE Trans. Ind. Electron.*, Vol. 53, No. 5, pp. 1512-1521, 2006.

- [5] F. Richardeau, P. Baudesson, and T. Meynard, "Failures-tolerance and remedial strategies of a PWM multicell inverter", *in Proceeding of IEEE Power Electronics Specialist Conference, Galway, Ireland*, pp. 649-654, 2000.

- [6] F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing", *IEEE Trans. Ind. Applicat.*, Vol. 37, pp. 611-618, 2001.

- [7] F. Z. Peng, J. W. McKeever, and D. J. Adams, "A power line conditioner using cascade multilevel

inverters for distribution systems", *in Proceeding of IEEE Industry Applications Society Conference*, Vol. 2, pp.1316-1321, 1997.

- [8] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: a competitive solution for high-power applications", *IEEE Trans. Ind. Applicat.*, Vol. 36, pp. 834-841, 2000.

- [9] K. A. Corzine and Y. L. Familiant, "A new cascaded multilevel H-bridge drive", *IEEE Trans. Power Electron.*, Vol. 17, pp.125-131, 2002.

- [10] J. I. Leon, S. Vazquez, A. J. Watson, L. G. Franquelo, P. W. Wheeler and J. M. Carrasco, "Feed-forward space vector modulation for single-phase multilevel cascaded converters with any DC voltage ratio", *IEEE Trans. Industrial Electronics*, Vol. 56, No. 2, pp. 315-325, 2009.

- [11] M. Manjrekar and T.A. Lipo, "A hybrid multilevel inverter topology for drive application", *in Proceeding of the APEC 98*, pp. 523-529, 1998.

- [12] C. Rech and J. R. Pinheiro, "Hybrid Multilevel Converters: Unified Analysis and Design Considerations", *IEEE Trans. Ind. Electron.*, Vol. 54, pp. 1092-1104, 2007.

- [13] Y. S. Lai and F. S. Shyu, "Topology for hybrid multilevel inverter", *IEE Proc. Electr. Power Applicat.* 149, pp. 449-458, 2002.

- [14] E. Babaei and S. H. Hosseini, "New cascaded multilevel inverter topology with minimum number of switches", *Energy Conversion and Management*, Vol. 50, 2761-2767, 2009.

- [15] M. R. Banaei and E. Salary, "New multilevel inverter with reduction of switches and gate driver", *Energy Conversion and Management*, Vol. 52, pp. 1129-1136, 2011.

- [16] K. El-Naggar and T. H. Abdelhamid, "Selective harmonic elimination of new family of multilevel inverters using genetic algorithms", *Energy Con*version and Management, Vol. 49, pp. 89-95, 2008.

- [17] E. Babaei, S. H. Hosseini, G.B. Gharehpetian, M. Tarafdar Haque and M. Sabahi, "Reduction of dc voltage sources and switches in asymmetrical multilevel converters using a novel topology", *Electric Power Systems Research*, pp. 1073-1085, 2007.

- [18] E. Babaei, "Optimal Topologies for Cascaded Sub-Multilevel Converters", *Journal of Power Electronics*, Vol. 10, No. 3, pp. 251-261, 2010.

- [19] N. Celanovic and D. Boroyevic, "A fast space vector modulation algorithm for multilevel three-phase converters", in Proceeding of Conf. Rec. IEEE-IAS Annu. Meeting, Phoenix, AZ, pp. 1173-1177, 1999.

- [20] J. Rodriguez, P. Correa, and L. Moran, "A vector control technique for medium voltage multilevel inverters", *in Proceeding of IEEE APEC, Anaheim*, *CA*, pp.173-178, 2001.

- [21] G. Carrara, S. Gardella, M. Marchesoni, R. Salutari and G. Sciutto, "A new multilevel PWM method: a theoretical analysis", *IEEE Trans. On. Pow. Electr.*, Vol. 7, No. 3, pp. 497-505, 1992.

- [22] L. Tolbert and T. G. Habetler, "Novel multilevel inverter carrier-based PWM method", *IEEE Trans. Ind. Applicat.*, Vol. 35, pp. 1098-1107, 1999.

- [23] Y. Liang and C. O. Nwankpa, "A new type of STATCOM Based on cascading voltage-source inverters with phase-shifted unipolar SPWM", *IEEE Trans. Ind. Applicat.*, Vol. 35, pp. 1118-1123, 1999.

- [24] K. A. Corzine, M. W. Wielebski, F. Z. Peng and J.Wang, "Control of cascaded multi-level inverters", *IEEE Trans Power Electron*; Vol. 19, No. 3, pp. 732-738, 2004.

- [25] Z. Du, L. M. Tolbert and J. N. Chiasson, "Active harmonic elimination for multilevel converters", *IEEE Trans. Power. Electron.* Vol. 21, No.2, pp. 459-469, 2006.

- [26] E. Babaei and S. H. Hosseini, "Charge balance control methods for asymmetrical cascade multilevel converters", *in Proceeding of international conference on electrical machines and systems, Korea*; pp. 74-79, 2007.

- [27] C. K. Lee, S. Y. Ron Hui, and H. Shu-Hung Chung, "A 31-Level Cascade Inverter for Power Applications", *IEEE Trans. Ind. Elect.*, Vol. 49, No. 3, pp. 613-617, 2002.

- [28] P. Zhiguo and F. Z. Peng, "Harmonics optimization of the voltage balancing control for multilevel converter/ inverter systems", in *Proceeding of IEEE 39th Annual Industry Applications Conference*, pp. 2194-2201, October, 2004.

- [29] J. Chiasson, L. Tolbert, K. Mc Kenzie and Z. Du, "Real-time computer control of a multilevel converter using the mathematical theory of resultants", Elsevier J. Math. Comput. Simul. Vol. 63, pp.197-208, 2003.

**Mohamad Reza Banaei** was born in Tabriz, Iran. He received his M.Sc. degree from the Poly Technique University of Tehran, Iran, in control engineering in 1999 and his Ph.D. degree from the electrical engineering faculty of Tabriz University in power engineering in 2005. He is an Associate

Professor in the Electrical Engineering Department of Azarbaijan Shahid Madani University, Iran, which he joined in 2005. His main research interests include the power electronics, renewable energy, modeling and controlling of FACTS and Custom Power devices and power systems dynamics.

**Ebrahim Salary** was born in Khoram Abad, Iran. He received his B.S. degree in power electrical engineering from Dezful Azad University, Dezful, Iran, in 2004 and his M.S. degree from Azarbaijan Shahid Madani University, Tabriz, Iran, in 2010. His main research

interests are power electronics, power

quality improvement and renewable energy.