# Improvement of Thermal Stability of Nickel Silicide Using Co-sputtering of Ni and Ti for Nano-Scale CMOS Technology

Meng Li, Sung-Kwen Oh, Hong-Sik Shin, and Hi-Deok Lee\*

Abstract—In this paper, a thermally stable nickel silicide technology using the co-sputtering of nickel and titanium atoms capped with TiN layer is proposed for nano-scale metal oxide semiconductor field effect transistor (MOSFET) applications. The effects of the incorporation of titanium ingredient in the co-sputtered Ni layer are characterized as a function of Ti sputtering power. The difference between the one-step rapid thermal process (RTP) and two-step RTP for the silicidation process has also been studied. It is shown that a certain proportion of titanium incorporation with two-step RTP has the best thermal stability for this structure.

*Index Terms*—Nickel silicide, titanium, co-sputtering, two-step RTP, thermal stability

# **I. INTRODUCTION**

silicides have been widely Metal used in microelectronic applications, particularly as the low resistance layer to reduce the series resistances of source, drain and gate regions in MOSFETs [1]. Although TiSi2 and CoSi<sub>2</sub> have been widely used for the salicide (selfaligned silicide) process, they have several limits such as agglomeration and the phase transformation of TiSi<sub>2</sub> in the high temperature thermal process of CMOS (Complementary Metal Oxide Semiconductor) fabrication. Moreover, with the scale-down of devices,

the narrow line effect of  $TiSi_2$  and the large Si consumption of  $CoSi_2$  have become serious problems in the fabrication of a ultra-shallow source/drain junction. Having advantages such as low temperature silicidation process, low silicon consumption, no bridging failure property, smaller mechanical stress, no adverse narrow line effect on sheet resistance, smaller contact resistance for both n- and p-Si and so on, nickel silicide has been thought as the most promising silicide layer [2]. Even so, NiSi has several challenges and one of them is the high-temperature degradation of NiSi [3]. There have been many attempts to improve the thermal stability of NiSi films [4-7].

In this work, we propose a structure formed by cosputtering of nickel and titanium atoms to improve the thermal stability of NiSi films for application to the nano-scale MOSFET technology. The effects of silicidation method, one-step RTP versus two-step RTP, have also been investigated for thermal stable NiSi technology.

# **II. EXPERIMENTAL**

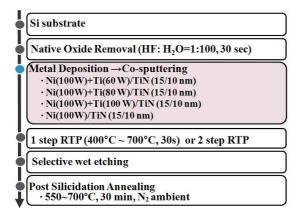

The experimental process flow for this work using a ptype Si substrate is summarized in Fig. 1. After removing the native oxide in diluted hydrofluoric acid (1:100), a 15 nm-thick Ti-incorporated Ni layer was deposited on the p-type Si substrate by co-sputtering of Ni and Ti targets using a radio frequency magnetron sputter system, followed by in situ deposition of a 10nm-thick TiN layer. The atomic ratio of Ti was controlled by split of the RF power of Ti target as 60, 80, and 100 W, respectively. A

Manuscript received Nov. 8, 2012; accepted Jan. 29, 2013. Dep. EE., Chungnam National University, Daejeon, Korea E-mail : hdlee@cnu.ac.kr

Fig. 1. Process flow for the experiments.

pure Ni film was also deposited using 100 W RF power for comparison. The TiN capping layer is commonly used to prevent oxygen contamination during silicide formation [8]. The base pressure was under  $5 \times 10^{-7}$  Torr and the working pressure was 2 mTorr with Ar plasma. A one-step RTP at various temperatures from 400~800°C for 30s, or two kinds of two-step RTPs (TSR1 : first RTP 500°C, second RTP 600°C, and selective wet etching, or TSR2 : first RTP 500°C, selective wet etching, and second RTP 600°C) were applied for each co-sputtering power condition. An SPM solution ( $H_2SO_4$  :  $H_2O_2 = 4:1$ ) was used for selective wet etching to remove the capping layer and the unreacted metal. Then high temperature furnace annealing (post silicidation annealing) was carried out for the samples with the RTP of 600°C at 550~700°C for 30 min in N2 (99.99%) ambient to evaluate the thermal stability of the formed Ni-silicide.

Sheet resistance was measured by the four point probe (FPP) method. X-ray diffraction (XRD) was employed to analyze the phases of the Ni-silicide films. Field emission scanning electron microscopy (FE-SEM) was used to study the interfacial structures and surface morphological stability of the Ni-silicide films. The depth profile of the elements Ni, Ti and Si was investigated by secondary ion mass spectrometry (SIMS).

### **III. RESULTS AND DISCUSSIONS**

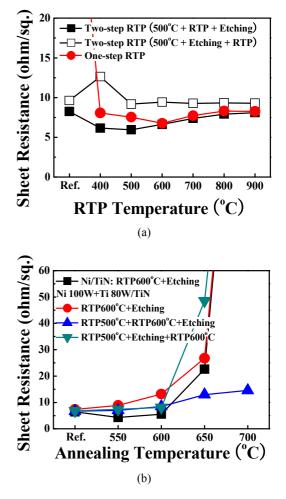

First, sheet resistance of the samples (Ni 100 W+Ti 80 W) with two kinds of two-step RTPs (TSR1 vs. TSR2) was compared as shown in Fig. 2(a). The sheet resistance using TSR1 (first RTP 500°C, second RTP, and wet

Fig. 2. Sheet resistance of Ni silicide as a function of (a) RTP temperature, and (b) post-silicidation annealing temperature for Ni(100 W)+Ti(80 W)/TiN samples.

etching) had a lower and more stable RTP window than that using TSR2 (first RTP 500°C, wet etching, and second RTP). TSR1 also shows much better thermal stability, i.e. stable sheet resistance for wide temperature range than the others as shown in Fig. 2(b). Hence, the TSR1 (first RTP 500°C, second RTP 600°C, and wet etching) was chosen as the reference two-step RTP from now on.

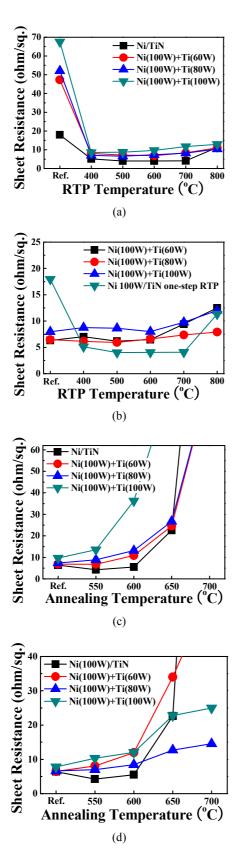

Then the sheet resistance windows of the samples with one-step RTP, two-step RTP (TSR2) and postsilicidation annealing were compared with each other as a function of RF power of Ti target as shown in Fig. 3. In case of one-step RTP, although all samples with the Ti incorporation shows better RTP and post-silicidation annealing window than the reference sample, they shows little dependence on the RF power of Ti target as shown in Fig. 3(a) and (c), respectively. However, in case of

**Fig. 3.** Sheet resistance of Ni silicide as a function of RTP temperature for (a) one-step RTP, (b) two-step RTP, and as a function of post-silicidation annealing temperature for (c) one-step RTP, (d) two-step RTP.

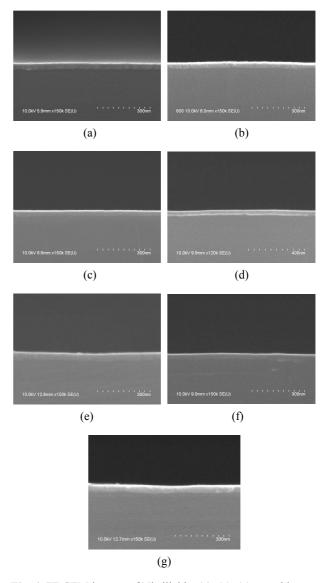

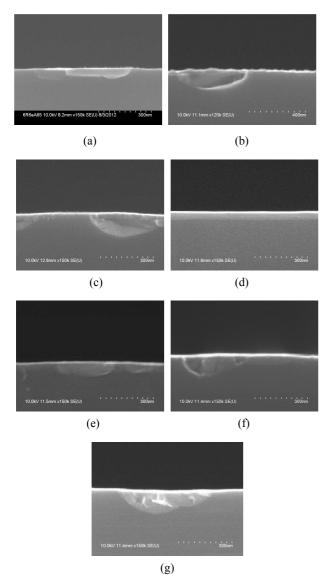

**Fig. 4.** FE-SEM images of Ni silicide. (a), (c), (e) are with onestep RTP(600°C) and (b),(d),(f) are with two-step RTP  $(1^{st}$  RTP: 500°C,  $2^{nd}$  RTP: 600°C). (a) and (b), (c) and (d) and (e) and (f) are with Ti 60 W, 80 W, 100 W, respectively. (g) is pure Ni/TiN for comparison.

two-step RTP, the samples with (Ni100 W+Ti 80 W) case shows the most stable sheet resistance window up to 800°C for both the RTP and post-silicidation annealing as shown in Fig. 3(b) and (d), respectively.

The morphological stability of the Ni silicide films before and after post-silicidation annealing was analyzed using FE-SEM as shown in Fig. 4 and Fig. 5, respectively. All samples had similar good crosssectional profile after both the one-step and two-step RTP whether Ti atoms are incorporated or not as shown in Fig. 4. However, the situation changes greatly after the post-silicidation annealing. The samples deposited by RF

**Fig. 5.** FE-SEM images of Ni silicide after post-annealing 650°C. Images (a), (c), (e) are with one-step RTP( $600^{\circ}$ C), and (b), (d), (f) are with two-step RTP( $1^{st}$  RTP:  $500^{\circ}$ C,  $2^{nd}$  RTP: 600°C). (a) and (b), (c) and (d), and (e) and (f) are with Ti 60 W, 80 W, 100 W, respectively. (g) is pure Ni/TiN for comparison.

power of Ni(100 W)+Ti(80 W) and annealed by two-step RTP showed the best morphological profile, and no obvious agglomeration was observed after 650°C postannealing as in Fig. 5(d), while agglomeration was observed for the other samples more or less after 650°C post-annealing.

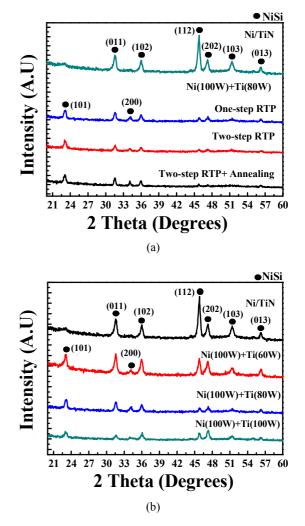

XRD results in Fig. 6(a) show that there are only NiSi peaks after one-step RTP, two-step RTP and 650°C postannealing and no obvious peak shift occurred for Ni(100 W)+Ti(80 W)/TiN samples. Fig. 6(b) shows that

Fig. 6. XRD phase analysis for Ni silicide (a), Ni/TiN after one-step RTP, and Ni(100 W)+Ti(80 W) after one-step RTP, two-step RTP and two-step RTP+ post-annealing in N<sub>2</sub> ambient for 30 min, (b) pure Ni, Ni+Ti(60 W, 80 W, 100 W) samples after RTP600°C, respectively.

different proportion of Ti did not make the shift of NiSi peaks, either. However, the intensity of the peaks changed dramatically. Variation of the intensity of a series of certain degree of texture was exhibited as a function of the RF power of Ti. The existence or increase of epitaxial components [NiSi(202), (102), (200)], and the decrease of axiotaxial components [NiSi(112), (103)] indicate better thermal stability of NiSi due to the lower interface energy. Addition of a refractory element (W, Ti, and Ta) to the Ni-Si reaction system can increase the activation energy of NiSi formation and improve the morphological stability of NiSi by increasing the activation energy of agglomeration. [9] It is believed that the kinetics of atom diffusion and thermodynamics

determine the morphological stability of the NiSi films. That is, agglomeration of NiSi will be retarded by the Ti atoms which are believed to exist at the grain boundary of NiSi because Ti atoms did not react with Ni or Si as shown in Fig. 6. The addition of a refractory element may slow down the growth of the grain boundary and surface diffusion, thus improving the morphological stability. In our research, a certain concentration of Ti controlled by the RF power and the two-step RTP suggest the best thermal stability of formed NiSi film, which means that the increase of Ti concentration improves the thermal stability of NiSi film, but further increase of Ti concentration will degrade the thermal stability.

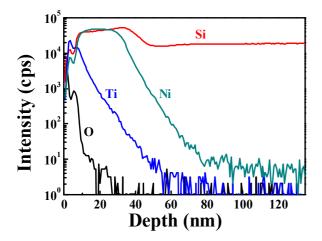

The depth profile of elements was analyzed using SIMS as shown in Fig. 7. Based on the results of XRD in Fig. 5, the majority of Ti atoms appear near the surface of the film and it can be assumed that Ti does not combine with Ni or Si to form a compound [10]. Moreover, there was a thin surface Ti-related layer (maybe Ti<sub>w</sub>Ni<sub>x</sub>Si<sub>y</sub>O<sub>z</sub> or a mixture of compounds containing these elements) above the NiSi layer. The observed formation of the Ti-related compound layer is considered to be due to the low solubility of Ti in NiSi and the strong chemical activity of Ti. This conclusion was similarly reported by R.T.P. Lee et al. using Ni and Ti alloy targets [11]. Also as our results showed, the sheet resistance was larger with the samples having a larger proportion of Ti in the Ni layer. R.T.P. Lee et al. considered that this was due to the increase of the thickness of the Ti-related layer with increasing

**Fig. 7.** SIMS depth profile of Ni(100 W)+Ti(80 W)/TiN sample after one-step RTP at 600°C.

proportion of Ti [11]. And D. Deduytsche *et al.* reported that a small amount of refractory can dissolve into the NiSi lattice or can be present at the grain boundaries, decreasing the NiSi grain size, and presented this result as another possible reason for the increase of sheet resistance [9].

# **IV. CONCLUSIONS**

The thermal stability of Ni-silicide was improved by co-sputtering of Ni and Ti with a capping layer of TiN in this study. The effects of different proportions of Ti in the Ni layer were also studied. Ni(100 W)+Ti(80 W) and two-step RTP condition the gave the best morphologically stable NiSi film. The NiSi's phase intensity using the structure in this study was also observed by XRD, which showed some certain but stronger diffraction intensity peaks than that using the pure Ni structure. The two-step RTP formed NiSi films with better thermal stability possibly because it changed the texture of NiSi layer. Though the Ti-incorporated NiSi in this study resulted in a slightly larger sheet resistance than pure NiSi, it significantly improved the morphological and thermal stability of NiSi films. Therefore, the proposed NiSi is highly promising for the nano-scale CMOS technology.

#### ACKNOWLEDGMENTS

This work was supported in part by the Ministry of Knowledge Economy(MKE) and Korea Institute for Advancement of Technology(KIAT) through the Workforce Development Program in Strategic Technology. This research was also financially supported in part by research fund of Chungnam National University in 2011.

#### REFERENCES

- M. C. Poon, C. H. HO, F. Deng, S. S. Lau, and H. Wong, "Thermal stability of cobalt and nickel silicides", *Microelectronics Reliability*, Vol. 38, No. 9, pp. 1495-1498, Sep, 1998.

- [2] H. Iwai, T. Ohguro, and S. Ohmi, "NiSi salicide technology for scaled CMOS", *Microelectronic Engineering*, Vol. 60, No. 1-2, p. 157-169, Jan,

2002.

- [3] C. Lavoie, F. M. d'Heurle, C. Detavernier, and C. Cabral Jr., "Towards implementation of a nickel silicide process for CMOS technologies", *Microelectronic Engineering*, Vol. 70, No. 2-4, pp. 144-157, Nov, 2003.

- [4] J. G. Yun, S. Y. Oh, B. F. Huang, H. H. Ji, Y. G. Kim, S. H. Park, H. S. Lee, D. B. Kim, U. S. Kim, H. S. Cha, S. B. Hu, J. G. Lee, S. K. Baek, H. S. Hwang, H. D. Lee, "Highly thermal robust NiSi for nanoscale MOSFETs utilizing a novel hydrogen plasma immersion ion implantation and Ni-Co-TiN tri-layer", *IEEE Electron Device Letters*, Vol. 26, No. 2, pp. 90-92, Feb., 2005.

- [5] Y. J. Kim, C. J. Choi, R. J. Jung, S. Y. Oh, J. G. Yun, W. J. Lee, H. H. Ji, J. S. Wang, and H. D. Lee, "The Effect of Triple Capping Layer (Ti/Ni/TiN) on the Electrical and Structural Properties of Nickel Monosilicide", *Journal of The Electrochemical Society*, Vol. 153 No. 1, pp. 35-38, 2006.

- [6] S. Y. Jung, Y. J. Kim, W. J. Lee, Y. Y. Zhang, Z. Zhong, S. G. Li, I. H. Kang, G. W. Lee, J. S. Wang, H. D. Lee, "Characterization of the Dopant Dependence of Ni-Silicide on a SOI Substrate for a Nano-Scale CMOSFET", *Journal of the Korean Physical Society*, Vol. 50, No. 6, p. 1883~1886, June, 2007.

- [7] C. J Choi, Y. W OK, T. Y Seong, H. D. Lee, "Effects of a SiO<sub>2</sub> Capping Layer on the Electrical Properties and Morphology of Nickel Silicides", *Japanese Journal of Applied Physics*, Vol. 41, No. 4A, pp. 1969-1973, 2002.

- [8] H. S. Shin, S. K. Oh, M. H. Kang, G. W. Lee, and H. D. Lee, "Improvement of Thermal Stability of Ni-Silicide Using Vacuum Annealing on Boron Cluster Implanted Ultra Shallow Source/Drain for Nano-Scale CMOSFETs", *Journal of Semiconductor Technology and Science*, Vol. 10, No.4, pp. 260-264, Dec., 2010.

- [9] D. Deduytsche, C. Detavernier, R. L. Van Meirhaeghe, J. L. Jordan-Sweet, and C. Lavoie, "Formation and morphological stability of NiSi in the presence of W, Ti, and Ta alloying elements", *Journal of Applied Physics*, Vol. 101, No. 4, 044508, 2007.

- [10] S. L. Chiu, Y. C. Chu, C. J. Tsai, and H. Y. Lee, "Effects of Ti Interlayer on Ni/Si Reaction

Systems", *Journal of The Electrochemical Society*, Vol. 151, No. 7, pp.452-455, 2004.

[11] R. T. P. Lee, D. Z. Chi, M. Y. Lai, N. L. Yakovlev, and S. J. Chua, "Effects of Ti Incorporation in Ni on Silicidation Reaction and Structural/Electrical Properties of NiSi", *Journal of The Electrochemical Society*, Vol. 151 No. 9, pp. 642-647, 2004.

**Meng Li** was born in China in 1982. He received the B.S. degree in electronics engineering from Mokwon University, Daejeon, Korea, in 2011. He is currently working toward the M.S. degree in the Department of Electronics Engineering, Chungnam

National University, Daejeon, Korea. His research interests include nickel silicide and Schottky barrier MOSFETs.

**Sung-Kwen Oh** received the B.S. degree in electronics engineering, in 2011, and is currently working toward the M.S. degree in the Department of Electronics Engineering from the Chungnam National University, Daejeon, Korea. His

research interests include germanide, Ge-MOSFETs, and Schottky barrier MOSFETs.

**Hong-Sik Shin** received the B.S. and M.S. degree in electronics engineering from the Chungnam National University, Daejeon, Korea in 2008 and 2010, respectively. He is currently working toward the Ph.D. degree in the Department of Electro-

nics Engineering, Chungnam National University, Daejeon, Korea. From 2008 to 2010, he was with the ETRI, Daejeon, Korea, as a researcher. His research interests include Printed electrode, Organic TFT, Ge-MOSFETs, Ni-silicide, and Schottky barrier MOSFETs.

**Hi-Deok Lee** received the B.S., M.S., and Ph.D. degrees all in electrical engineering from the Korea Advanced Institute of Science and Technology(KAIST), Daejeon, Korea, in 1990, 1992, and 1996, respectively.

In 1993, he joined the LG Semicon Company, Ltd. (currently SK Hynix Semiconductor Ltd.), Chongju, Choongbuk, Korea, where he has been involved in the development of 0.35-µm, 0.25-µm, and 0.18-µm CMOS technologies, respectively. He was also responsible for the development of 0.15-µm and 0.13-µm CMOS technologies. Since 2001, he has been with Chungnam National University, Daejeon, Korea, with the Department of Electronics Engineering. From 2006 to 2008, he was with the University of Texas, Austin, and SEMATECH, Austin, as a Visiting Scholar. His research interests are in the areas of nanoscale CMOS technology and its reliability physics, silicide technology, and Test Element Group design. His research interests also include development of high performance analog MOSFETs and high voltage MOSFETs, and analysis of their noise and reliability characteristics. Dr. Lee is a member of the Institute of Electronics Engineers of Korea. He received the Excellent Professor Award from Chungnam National University in 2001 and 2004.