# A New Resistance Model for a Schottky Barrier Diode in CMOS Including N-well Thickness Effect

Jaelin Lee\*, Suna Kim\*, Jong-Phil Hong\*\*, and Sang-Gug Lee\*

Abstract—A new resistance model for a Schottky Barrier Diode (SBD) in CMOS technology is proposed in this paper. The proposed model includes the n-well thickness as a variable to explain the operational behavior of a planar SBD which is firstly introduced in this paper. The model is verified using the simulation methodology ATLAS. For verification of the analyzed model and the ATLAS simulation results, SBD prototypes are fabricated using a 0.13µm CMOS process. It is demonstrated that the model and simulation results are consistent with measurement results of fabricated SBD.

*Index Terms*—CMOS, capacitance, cut-off frequency, n-well thickness, resistance, Schottky barrier diodes

### I. Introduction

As research interest in RF circuits extends to higher frequency, up to even terahertz range, high speed operation of RF circuit becomes a critical factor in amplifier, mixer, oscillator, detector, etc. CMOS technology is a good choice in terms of cost and the integration. However, the switching speed of CMOS transistors limits the high frequency performance. To overcome the speed limitation, researches on Schottky barrier diode (SBD) in CMOS technology has recently been carried out [1, 2]. The SBD which has a Schottky barrier junction formed by a metal and a lowly-doped

semiconductor is a fast device. Since the SBD is a majority carrier device, its switching speed is fast and also its resistance and capacitance values are small due to its simple structure. The SBD therefore can have relatively high cut-off frequency  $(f_T)$  which is an index to evaluate the high frequency performance of a device.

In the GaAs planar SBD, a decrease in the thickness of the n-type-layer results in a decrease of the cut-off frequency [3]. On the other hand, in the SiGe planar SBD, a decrease in the thickness of the n-type-layer results in a decrease of the resistance, which leads to an increase of the cut-off frequency [4]. The thickness of the n-type-layer thus is an important parameter that affects the cut-off frequency of the SBD. Although the CMOS SBDs presented in [1, 2] show good performance, the authors did not explain how process selects parameters and did not conduct simulations based on a theoretical analysis. With technology scaling, an accurate model that incorporates the layer thickness is needed for the CMOS SBD design.

In this paper, a new resistance model for a CMOS SBD that takes into account the n-well thickness effect is analyzed and verified with the ATLAS device simulator. Several prototypes are fabricated in a 0.13µm CMOS process and evaluated to verify the proposed model and the simulation results.

#### II. RESISTANCE MODEL FOR A CMOS SBD

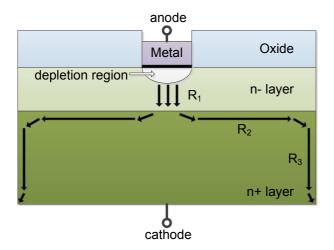

Fig. 1 shows a basic SBD structure: a Dot-matrix SBD [5]. In Fig. 1,  $R_1$  is the vertical spreading resistance,  $R_2$  is the horizontal spreading resistance of the undepleted n-layer,  $R_3$  is the sidewall resistance. At the metal-n-layer junction, junction capacitance  $C_{70}$  exists. Among the

E-mail: jphong@chungbuk.ac.kr

Manuscript received Mar. 7, 2013; accepted Apr. 29, 2013

<sup>\*</sup>Department of Electrical Engineering, KAIST, Daejeon, Korea E-mail : smacley@kaist.ac.kr

<sup>\*\*</sup> Department of Electrical Engineering, Chungbuk National University, Cheongju, Korea

Fig. 1. Current distribution in the Dot-matrix Schottky barrier diode.

resistance components indicated in Fig. 1,  $R_1$  is the most significant factors related to the cut-off frequency. The cut-off frequency is expressed as

$$f_T = \frac{1}{2\pi RC_{i0}} \ . \tag{1}$$

In Eq. (1), R is the sum of  $R_1$ ,  $R_2$ , and  $R_3$ , and they are respectively defined as [5];

$$\begin{split} R_1 &= \frac{4(t-d)}{\pi a^2 q \mu_n N_d} \ , \\ R_2 &= \frac{\ln(b/a)}{2\pi \delta q \mu_n N_d} \ , \\ R_3 &= \frac{h}{\pi b \delta q \mu_n N_d} \ , \end{split} \tag{2}$$

and

$$C_{j0} = \frac{\pi a^2}{4} \sqrt{q \varepsilon_s N_D / 2 \phi_{bi}} . \tag{3}$$

Here, a is the diameter of the anode, b is the diameter of the cathode, q is the electron charge,  $\mu_n$  is the mobility of n- layer,  $N_d$  is the doping concentration of the n- layer, t is the thickness of the n-layer, d is the thickness of the depleted n-layer,  $\delta$  is the skin depth of the n- layer,  $\varepsilon_s$  is the permittivity of the n-layer, and  $\varphi_{bi}$  is the Schottky barrier height. The previously reported SBD model expressed in (2) and (3), however, is not suitable to CMOS SBD, because it can only be realized in a planar structure where the anode and the cathode should be

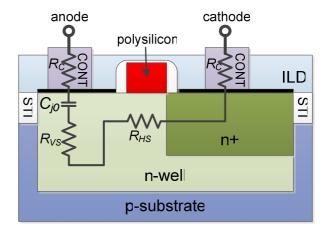

Fig. 2. Cross section of a planar Schottky barrier diode.

positioned on the same surface, contrary to the structure illustrated in Fig. 1.

Fig. 2 shows the structure and equivalent circuit of a planar SBD in CMOS technology. Planar SBD has rectangular structure while dot-matrix diode has circular structure. In Fig. 2, the polysilicon separates the anode and cathode of the SBD. This structure offers a minimum spreading resistance [2]. In this structure, the R of the SBD can be described by the combination of the vertical spreading resistance ( $R_{VS}$ ) and horizontal spreading resistance ( $R_{HS}$ ) in the n-well region and the contact resistances ( $R_{C}$ ) as follows:

$$R = \sqrt{R_{VS}^{2} + R_{HS}^{2}} + R_{C}$$

$$= \sqrt{\left(\frac{t - d}{w l q \mu_{n} N_{d}}\right)^{2} + \left(\frac{s + \frac{l}{n}}{w t q \mu_{n} N_{d}}\right)^{2}} + R_{C}$$

$$= \frac{1}{w q \mu_{n} N_{d}} \sqrt{\left(\frac{t - d}{l}\right)^{2} + \left(\frac{s + l/n}{t}\right)^{2}} + R_{C}.$$

(4)

In Eq. (4), t is the thickness of the n-well region, d is the thickness of the depleted n-well region, s is the minimum distance between the anode and cathode, l is the anode length, w is the anode width, and n is the current spreading factor, which has a value of  $2\sim3$  [6].  $R_{VS}$  which corresponds to  $R_1$  is inversely proportional to the anode area and proportional to the thickness of the undepleted n-well region. On the other hand, note that  $R_{HS}$  is newly proposed for CMOS planar SBD instead of  $R_2$  in (2). From (4), a smaller t increases  $R_{HS}$ , because the

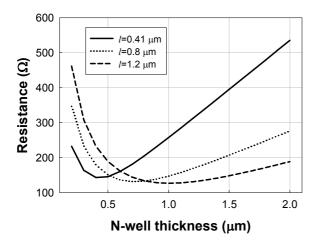

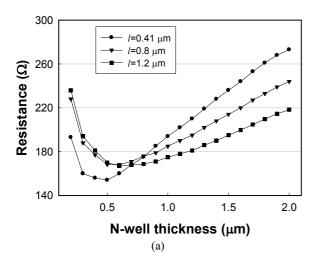

Fig. 3. Calculated resistance based on (4).

current path of the diode is limited by t. A larger s+l/n increases the length of current path in n-well, thus it also increases  $R_{HS}$ .  $R_C$  is the contact resistance, which is regarded as very small value.

When the n-well is very thin,  $R_{HS}$  dominates the total resistance of the SBD, whereas when the n-well is thick enough, then the current path is unaffected by t and  $R_{VS}$  becomes the dominant component. Fig. 3 shows the calculated resistance of a planar SBD based on (4) for three different anode lengths as a function of the n-well thickness, while the width of the anode is fixed at 1.04  $\mu$ m.

For the calculation, d=0.1  $\mu$ m, n=2, s=0.2  $\mu$ m,  $\mu_n$ =800 cm<sup>2</sup>/V-s,  $N_d$ =6.5·10<sup>17</sup>/cm<sup>3</sup>, and  $R_c$ =0 are adopted. In Fig. 3, when the n-well thickness is relatively thin (<0.5 $\mu$ m),  $R_{HS}$  is dominant and thus larger anode length leads to higher overall total resistance. On the other hand, when the n-well is relatively thick, narrower anode length shows lower total resistance since  $R_{VS}$  becomes the dominant factor and is inversely proportional to the anode area. Therefore, the anode length should be selected differently according to the thickness of the n-well.

The main factor of the capacitance in the CMOS planar SBD is the junction capacitance between the metal and n-well and it is proportional to the anode area as in (3).

## III. MODEL VERIFICATION USING ATLAS

Fig. 4(a) shows the cross section of a planar SBD realized by ATLAS. In Fig. 4(a), the bulk semiconductor material is silicon because this SBD is based on a CMOS process.

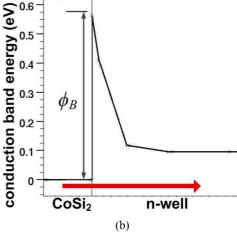

**Fig. 4.** (a) Cross section of a planar SBD from ATLAS simulation, (b) conduction energy band diagram of metal-n-well junction.

Table 1. Process variables for ATLAS simulation

| Variable                         | Value                                 |

|----------------------------------|---------------------------------------|

| N <sub>D</sub> . (for n-well)    | $6.5 \cdot 10^{17} / \text{cm}^3$     |

| N <sub>D+</sub> (for n+ region)  | 5·10 <sup>20</sup> /cm <sup>3</sup>   |

| x <sub>j</sub> (n+ depth)        | 0.45 um                               |

| N <sub>A</sub> (for p-substrate) | 1.5·10 <sup>17</sup> /cm <sup>3</sup> |

| φ <sub>B</sub> (Barrier height)  | 0.56 eV                               |

There are several process and dimension variables in the simulation. The doping concentrations of the p-substrate, n-well, and n+ region, and the barrier height of the Schottky junction belong to process variables, which are pre-determined in a given 0.13 µm CMOS technology.

In particular, the doping concentrations of the n-well and p-substrate are extracted from the conductivity information. For example, the conductivity of the n-well is  $\sigma_{n-} = q \mu_n N_D$ , and so,  $N_D$  can be extracted using the inversely proportional relationship between  $\mu_n$  and

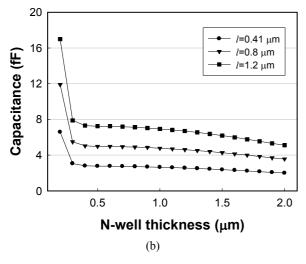

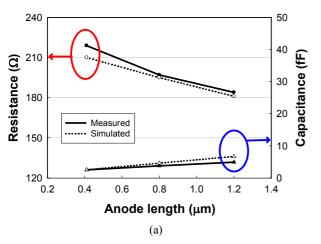

$N_D$  [7]. CoSi<sub>2</sub> a well known silicide material, is used for the contact metal. Fig. 4(b) shows the form of the Schottky barrier between CoSi2 and the n-well region. The size of the anode and the cathode, the length of polysilicon, and the n-well thickness are dimension variables. In the simulation, for n-well thickness range of 0.2 µm to 2-µm and three different anode lengths, the resistance and capacitance of each SBD are extracted from a 2-port S-parameter analysis over the frequency range of 10 to 20-GHz. The width of each SBD is fixed at 1.04 µm. Fig. 5 shows the simulation results of the resistance and capacitance extracted from ATLAS simulator. As shown in Fig. 5(a), the simulation results agree well with the proposed model of the total resistance for CMOS SBD. Because the proposed model deals only with the resistance from the drift current, which is the

**Fig. 5.** Simulation result for (a) resistance, (b) capacitance as a function of the n-well thickness and the anode length.

dominant current of the SBD, there is a slight mismatch between the simulation and model. In Fig. 5(b), the capacitance of the SBD becomes higher as the anode length increases. When the n-well is thicker than a certain point (0.4  $\mu$ m in this case), the capacitance is nearly constant for each anode length. Although the capacitance seems to be affected by the n-well thickness, the degree of this effect is much less significant than that of the anode area.

## IV. FABRICATION AND MEASUREMENT

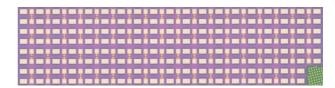

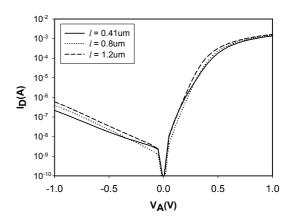

Fig. 6 shows a micrograph of the fabricated chip. Several prototypes of the Schottky barrier diode were fabricated in a 0.13 μm CMOS process. Each prototype is designed to have different anode and cathode areas (length, width) while varying the number of cells. Fig. 7 shows measured I-V characteristics of three prototypes that have different anode lengths while the anode width is fixed at 1.04 μm. By adapting saturation current to equation [8], schottky barrier height is extracted as 0.56 eV on average. The S-parameters of the 0V biased SBDs are measured in a 1-port configuration with a vector network analyzer over the frequency range of 10 to 20-GHz. From measured S11, R and C are extracted and cutoff frequency is calculated using (5).

Fig. 6. Micrograph of several prototypes of Schottky barrier diode.

Fig. 7. Measured I-V characteristic of fabricated SBD.

$$Z = \frac{1 - S11}{1 + S11} = R + \frac{1}{i\omega C}$$

(5)

Primary calibration is done by a calibration substrate, and the capacitances from pads are removed by an open dummy pattern.

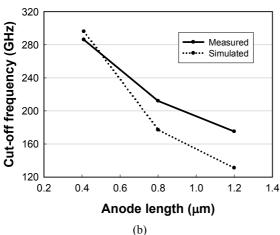

Fig. 8(a) shows the simulated and measured resistance and capacitance of three prototypes that have different anode lengths while the anode width is fixed at  $1.04\mu m$ . The n-well thickness for the prototypes is estimated as  $1.2\mu m$  from the PDK, and this value is used for the simulation. In Fig. 8(a), the measurement results are in good agreement with the proposed model and simulation results; specifically, the total resistance becomes smaller with larger anode length in a thick n-well. The measured values of the resistance are slightly higher than that of the simulation results. This is attributed to the lack of calibration for the metal sheet resistance and the  $R_C$  effect in the simulation. Due to the lack of process

**Fig. 8**. (a) Simulated and measured resistance and capacitance, (b) corresponding cut-off frequency.

information, there are some error among calculation, simulation and measurement. As shown in Fig. 8(b), from the measured resistance and capacitance, the highest cut-off frequency of the prototype SBD is 286 GHz, when the anode length is  $0.41 \, \mu m$ .

#### V. CONCLUSION

The dependency of the n-well thickness on the resistance of the CMOS Schottky barrier diode is described by a newly proposed resistance model in this paper. Depending on the dimension of the n-well thickness, the dominant resistance factor is changed. In the case of a thin n-well structure, short anode length is preferred for low dominant horizontal resistance, while long anode length improves the total resistance by decreasing the dominant vertical resistance in a thick nwell structure. The proposed model is verified with an ATLAS simulation and measurement of prototypes fabricated in a 0.13 µm CMOS process. As the n-well thickness is predicted to decrease with CMOS technology scaling, the proposed resistance model and the verification results can be very helpful for the design of CMOS SBDs in each technology considering the nwell thickness.

## ACKNOWLEDGEMENT

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korean government (MEST) (No. 2010-0027023)

#### REFERENCES

- [1] R. Han, Y. Zhang, D. Coquillat, H. Videlier, W. Knap, E. Brown, and K. K. O, "A 280-GHz Schottky diode detector in 130-nm digital CMOS", *IEEE J. Solid-State Circuits*, vol. 46, no. 11, pp.2602-2012, Nov. 2011

- [2] S.-M.Chen, Y.-K.Fang, F.R.Juang, W.-K.Yeh, C.-P.Chao, and H.-C.Tseng, "Terahertz Schottky barrier diodes with various isolation designs for advanced radio frequency applications", *Thin Solid Films*, vol 519, no. 1, pp.471-474, Oct. 2010

- [3] W. Kellner, N. Enders, D. Ristow and H. Kniepkamp, "Design considerations for planar

- schottky barrier diodes", *Solid-State Electronics*, Vol. 23, pp.9-15, Mar. 1979

- [4] R. Rassel, J. Johnson, B. Orner, S. Reynolds, M. Dahlstrom, J. Rascoe, A. Joseph, B. Gaucher, J. Dunn, and S. S. Onge, "Schottky barrier diodes for millimeter wave SiGe BiCMOS applications", *IEEE Bipolar/BiCMOS Circuit Technol. Meeting*, pp.255-258, Oct. 2006

- [5] S. A. Maas, *Microwave Mixers*. Boston, MA: Artech House, 1993

- [6] Q. Zhang and T.S.Sudarshan, "Lateral current spreading in SiC Schottky diodes using metal overlap edge termination", *Solid-State Electronics*, Vol. 45, pp.1847-1850, 2001

- [7] Ben G. Streetman and Sanjay Kumar Banerjee, Solid State Electronic Devices. Prentice Hall, 2006

- [8] Veljko Milanovic, Michael Gaitan, Janet C. Marshall, and Mona E. Zaghloul, "CMOS Foundary Implementation of Schottky diodes for RF Detection", *IEEE T. on Electron Devices*, Vol. 43, No. 12, Dec. 1996

Jaelin Lee was born in Daegu, Korea in 1988. She received the B.S. degree in the Department of Electronic and Electrical Engineering from Korea Advanced Institute of Science and Technology (KAIST), Korea in 2011. She is currently

pursuing the Master degree in the Department of Electrical Engineering from KAIST, Korea. Her interests include device physics, extremely high-frequency (THz) CMOS devices and circuits.

Suna Kim received the B.S. and M.S. degrees in electrical engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2006 and 2009, respectively. She is currently working toward the Ph.D. degree in electrical

engineering at KAIST. Her research interests include RF integrated circuit designs and further digital calibration circuit designs for wireless transceivers. Lately, her research interests extend to extremely high-frequency (THz) device and circuit designs based on CMOS technology.

Jong-Phil Hong received B.S. degree in electronic engineering from Korea Aerospace University, Seoul, Korea, in 2005. He received M.S. and Ph. D degree at department of information and communications engineering, Korea Advanced Institute

of Science and Technology (KAIST), Dajeon, Korea, in 2007 and 2010, respectively. In 2010, he joined Samsung Electronics, Giheung, Korea, as a senieer engineer in the mixed-signal circuit design team. Since 2012, he has been with the Chungbuk National University, Cheongju, Korea, in the department of electrical engineering as an assistant professor. His main research interests include RF integrated circuits such as LNA, Mixer, VCO and frequency synthesizer for wireless and wire-line communication systems. Currently, his research interests are toward digital PLLs and high frequency (THz) circuit design based on CMOS technology.

Sang-Gug Lee received the B.S. degree in electronic engineering from Kyungpook National University, Korea, in 1981, and the M.S. and Ph.D. degrees in electrical enginnering at the University of Florida, Gainesville, in 1989 and 1992, respectively.

In 1992, he joined Harris Semiconductor, Melbourne, Florida, where he was engaged in silicon-based RFIC designs. From 1995 to 1998, he was with Handong University, Pohang, Korea as an Assistant Professor in the School of Computer and Electrical Engineering. From 1998 to 2009, he was with the Information and Communication University, Daejeon, Korea, and become as a Professor. Since 2009, he has been with the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in the Department of Electrical Enginnering as a Professor. His research interests include CMOS-based RF, analog, and mixed mode IC designs for various radio transceiver applications. Lately, his reaserch interests are in low-power transceivers and extreme high-frequency (THz) circuit design based on CMOS technology, and display and energy-harvesting IC designs.