# Preliminary Works of Contact via Formation of LCD Backplanes Using Silver Printing

Yong Suk Yang, In-Kyu You, Hyun Han, Jae Bon Koo, Sang Chul Lim, Soon-Won Jung, Bock Soon Na, Hye-Min Kim, Minseok Kim, and Seok-Hwan Moon

The fabrication of a thin-film transistor backplane and a liquid-crystal display using printing processes can eliminate the need for photolithography and offers the potential to reduce the manufacturing costs. In this study, we prepare contact via structures through a poly(methyl methacrylate) polymer insulator layer using inkjet printing. When droplets of silver ink composed of a polymer solvent are placed onto the polymer insulator and annealed at high temperatures, the silver ink penetrates the interior of the polymer and generates conducting paths between the top and bottom metal lines through the partial dissolution and swelling of the polymer. The electrical property of various contact via-hole interconnections is investigated using a semiconductor characterization system.

Keywords: Organic thin-film transistors, inkjet printing, contact via, silver ink, conductivity, penetration, LCD.

http://dx.doi.org/10.4218/etrij.13.1912.0018

### I. Introduction

A liquid-crystal display (LCD) is organized into a number of parts, including backlights, polarizers, glass, liquid crystals, and color filters, each of which requires numerous unit processes for their manufacturing [1], [2]. In the early mass production stage, the most striking feature in terms of cost has been the high proportion of material and component costs, reaching approximately 70% to 75% of the total cost amount [3], [4]. As competition in the LCD industry heats up and investments intensify incrementally, panel prices are decreasing. However, a drop in material prices has not caught up with this downward trend. For this reason, the current cost structure is at a price point that is not attractive to consumers. Although innumerable parts account for the bulk of LCD panel costs, LCD panel makers have reached their limit in shaving panel costs by adjusting the price of each part and are therefore placing more focus on methods and technologies to trim panel costs incurred in the manufacturing process [5].

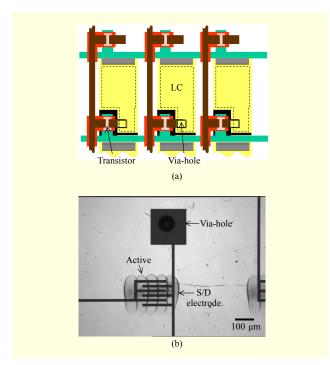

Figure 1(a) shows the typical structure of a thin-film transistor (TFT) backplane for an LCD panel. The pixels of the LCD panel are addressed in rows and columns, and the column and row wires are attached to transistor switches, one for each pixel [3]. The circuit layout process of a TFT-LCD is very similar to that of semiconductor products. The layers of a semiconductor, insulator, and metal for a TFT-LCD are typically formed using the vacuum deposition and photolithography processes, which are costly and difficult to produce.

Because activities to simplify the procedures, heighten the yields, and speed up the manufacturing processes can have a positive impact on the reductions in the production costs of the

Manuscript received Nov. 30, 2012; revised May 9, 2013; accepted June 3, 2013.

This study was supported by the Development of New Materials and Solution Process for LCD Backplanes funded by ISTK (B551179-09-06-00).

Yong Suk Yang (phone: +82 42 860 1171, jullios@etri.re.kr), In-Kyu You (ikyou@etri.re.kr), Jae Bon Koo (kjb0706@etri.re.kr), Sang Chul Lim (lsc@etri.re.kr), Soon-Won Jung (jungsoonwon@etri.re.kr), Bock Soon Na (bsna@etri.re.kr), and Seok-Hwan Moon (shmoon@etri.re.kr) are with the Components & Materials Research Laboratory, ETRI, Daejeon, Rep. of Korea.

Hyun Han (hyunh@krict.re.kr) is with the Division of Advanced Materials, Solar Energy Materials Research Group, Korea Research Institute of Chemical Technology, Daejeon, Rep. of Korea

Hye-Min Kim (kimhm@kaeri.re.kr) was with the Components & Materials Research Laboratory, ETRI, Daejeon, Rep. of Korea, and is now with the Energy Application Technology Research Team, Korea Atomic Energy Research Institute, Daejeon, Rep. of Korea.

Minseok Kim (gemin7@korea.ac.kr) was with the Components & Materials Research Laboratory, ETRI, Daejeon, Rep. of Korea, and is now with the School of Electrical Engineering, Korea University, Seoul, Rep. of Korea.

Fig. 1. (a) Top view of LCD backplane and (b) photograph of printed via-hole, active material, and source-drain electrode.

TFT backplane, the interest in LCD display has focused the attention on printing processes, and several printing techniques to pattern electronic parts have been reported [6]-[8]. For printed electronics, contact printing uses a master in a drum or flat plate system, with examples being screen printing, gravure, offset, and micro-contact printing [9]. On the other hand, inkjet printing requires no master, allows digital control of the ejection to provide drop-on-demand (DOD) printing, and is a noncontact process [10]-[12]. Figure 1(b) reveals the typical image of a TFT and via-hole printed on a SiO<sub>2</sub>/Si substrate using inkjet printing.

In 2001, Kawase and others reported that polymer electronic circuits fabricated entirely using a roll-to-roll process have problems with not only TFT devices but also interconnections, via-holes, and resistors [13], [14]. They asserted that the formation of via-holes constitutes a new issue that cannot be solved with the conventional features of inkjet printing because the insulator must be removed locally to achieve a vertical interconnection. They also suggested that via-holes can be created through the selective removal of the poly(vinyl phenol) (PVP) polymer insulator by the inkjet printing of a solvent for the insulator. However, this method has a disadvantage in that it is difficult to apply to various organic insulators and is easy to generate a rough surface of the insulator.

In this paper, we report on the fabrication of contact via-holes by silver printing. The contact via-hole interconnections are formed during a simple process consisting of inkjet printing of silver ink on a polymer insulator and annealing at a high temperature. To confirm the generation of the via-hole interconnections, we measure the electrical property of metal-insulator-metal capacitors, the transaction image, and the element concentrations. The repeatability of the via-holes is also measured based on the current-voltage (*I-V*) characteristics for 30 samples.

# II. Experimental Methods

Contact via-hole interconnections are developed in a SiO<sub>2</sub> (3,000 Å)/Si wafer, which is prepared as a substrate after cleaning sequentially with acetone and isopropyl alcohol for 10 min during each step and then rinsing with de-ionized water. Au and Cr metals as a bottom electrode are deposited in situ on thermally-oxidized silicon using a conventional e-beam evaporator at a pressure of below 10<sup>-4</sup> Pa. Poly(methyl methacrylate) (PMMA, Aldrich, MW=120,000) as a polymer insulator is prepared without further purification. The crosslinking agent, 1,6-bis(trichlorosilyl)hexane (Acro Organics, UK), is purified by distillation under an inert atmosphere. For a 300-nm-thick film, PMMA (80 mg/ml in anhydrous n-butyl acetate) is blended with 1,6-bis(trichlorosilyl) hexane (5 µl); the mixture is then filtered using a 0.1-µm syringe filter and spincoated at 2,000 rpm onto the substrate. Finally, the PMMA film is annealed on a hot plate at 100°C for 30 min to remove the solvent. All steps are performed in a glove box [15].

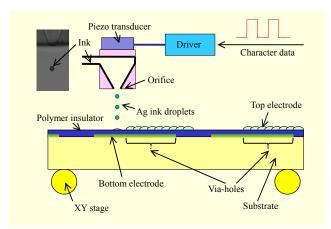

The contact via-hole is formed in this structure using an inkjet printing process with conductive silver ink. We use the commercial inks based on organosilver compounds, which are produced by InkTec (Republic of Korea). The silver ink (Ag=15 wt%) consists of organosilver complexes containing carboxylic acid (80%), methanol (15%), and anisole (5%) [16], [17]. An additional 5% of PMMA solvent, dichloromethane (Aldrich, USA), is added to the organosilver ink. The inkjet DOD fabrication of a via-hole array consists of a basic setup utilizing a heated fluid reservoir coupled to a piezoelectric ceramic through which a machined nozzle dispenses uniform polymer droplets onto the substrate mounted to xyz microcontrollers, as illustrated in Fig. 2. The spherical drops, with a diameter of 55 µm, are generated using a Microfab device equipped with a nozzle 50 µm in diameter. The substrate is placed on a movable xyz table, onto which the spherical drops are deposited in a dust-free atmosphere. To achieve an interconnection between the bottom and top electrodes, the droplets of silver ink are precisely dropped onto the PMMA(3000 Å)/Au(1000 Å)/Cr(30 Å)/SiO<sub>2</sub>(3000 Å)/Si area. After the printing, the samples are annealed in a temperature range between 110°C and 170°C for 30 min to

Fig. 2. Schematic image of contact via interconnections produced using inkjet printing method.

remove solvents from the silver film. Finally, Al metal as a top electrode is deposited *in situ* on the printed Ag/PMMA/Au/Cr/SiO<sub>2</sub>/Si samples using an e-beam evaporator at a pressure below 10<sup>-4</sup> Pa.

The electrical property is measured using a semiconductor characterization system (Keithley 4200). The cross-section image and element concentrations are measured using a scanning electron microscope (SEM) and energy dispersive X-ray spectrometry (EDX).

## III. Results and Discussion

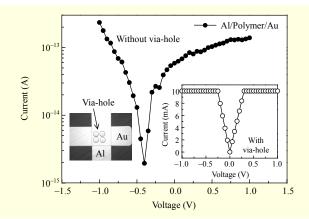

In our work, we fabricate an Al/PMMA/Au capacitor with via-hole interconnections using silver ink droplets, as shown in the inset of Fig. 3. The annealing temperature in the via-hole printing process is 150°C for 30 min. Four via-holes are formed in the area overlapping between the Al and Au electrodes. The diameter of each via-hole is approximately 100 µm. Figure 3 shows the I-V characteristics of Al/PMMA/Au capacitors with or without via-hole interconnections, which are tested at room temperature and ambient pressure. The I-V curve for the Al/PMMA/Au capacitor without via-hole interconnections represents the insulating property of the PMMA polymer precisely, and the leakage current is below 0.15 pA at a voltage of  $\pm 1$  V. The *I-V* curve for the sample with via-hole interconnections indicates the behavior of a short circuit, as shown in the inset of Fig. 3. In this result, the excessive electric current is limited by the compliance of the semiconductor characterization system.

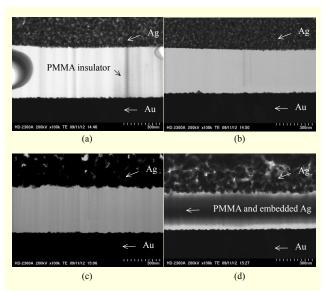

Figures 4(a) through 4(d) show the cross-sectional images of an Al/printed Ag/PMMA/Au capacitor annealed at various temperatures during the via-hole process. The cross-sections are prepared through ion beam milling utilizing a focused ion beam (FIB), and the images are observed using an SEM. The

Fig. 3. *I-V* characteristics of Al/PMMA/Au capacitors with or without via-hole interconnections. Inset is photograph of Al/PMMA/Au capacitor with via-hole interconnections using silver ink droplets. Compliance current is 10 mA.

Fig. 4. Cross-sectional SEM images of Al/printed Ag/PMMA/Au capacitor annealed at (a) 110°C, (b) 130°C, (c) 150°C, and (d) 170°C for 30 min.

samples reflected in Figs. 4(a) through 4(d) are annealed at temperatures of 110°C, 130°C, 150°C, and 170°C for 30 min, respectively. In the FIB-SEM images, three shaded regions are observed. The top layer is the printed Ag layer, which displays a dark gray color. As the annealing temperature increases, more densely packed silver layers are observed. The middle layer is a PMMA polymer insulator, which is smooth and a light gray color, as shown in Fig. 4(a). However, when the annealing temperature increases, the thickness of the PMMA decreases and the color changes from light gray to dark gray. The bottom layer is the evaporated Au layer of another dark gray color. EDX studies over the dark gray region indicate the presence of metal ingredients, such as silver and gold.

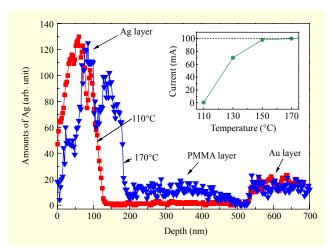

Fig. 5. Depth profiles of silver components in Al/printed Ag/PMMA/Au capacitors measured by EDX. Inset is current at V=0.3 V for samples annealed at 110°C and 170°C for 30 min. Compliance current is 100 mA.

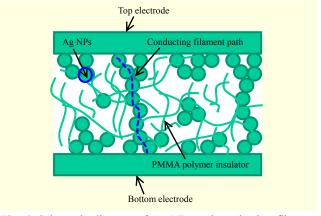

Figure 5 reveals the depth profiles of silver components in Al/printed Ag/PMMA/Au capacitors measured by EDX. The samples are annealed at temperatures of 110°C, 130°C, 150°C, and 170°C for 30 min after the inkjet printing of Ag ink on the PMMA. The region of the Ag, PMMA, and Au layers is distinguished well. The silver amount in the bottom electrode does not necessarily imply a measurement/interpretation error but could actually originate from the porosity of evaporated Au electrodes as used in the experiments. As the annealing temperature increases, the amount of embedded Ag in PMMA increases, and the PMMA then becomes metallic in the area of the via-holes. This result indicates that the color change of PMMA to dark gray may be attributed to an increase in the embedded Ag nanoparticles (NPs) in the PMMA polymer insulator. On the other hand, the EDX analysis of the light gray region in the PMMA indicates a few Ag components. The current at V=0.3 V for the samples annealed within the temperature range between 110°C and 170°C for 30 min are given in the inset of Fig. 5. The compliance current is 100 mA, and the area of via-holes is approximately  $3.14\times10^4$  µm<sup>2</sup>. As the annealing temperature is increased, the leakage current of the samples increases to the compliance current. This result indicates that the conducting path through the PMMA insulator might be made during the inkjet printing and annealing processes at a high temperature. In particular, the solvents in Ag ink might play an important role in the embedding of Ag NPs into the PMMA materials by the partial dissolution and swelling of the polymer film. Figure 6 shows a schematic diagram of the Ag NPs and the conducting filament path through the PMMA insulator. Both the penetration of the Ag NPs and the formation of a conducting filament path in the polymer insulator are significant in making a printed via-hole.

Fig. 6. Schematic diagram of Ag NPs and conducting filament path through PMMA insulator.

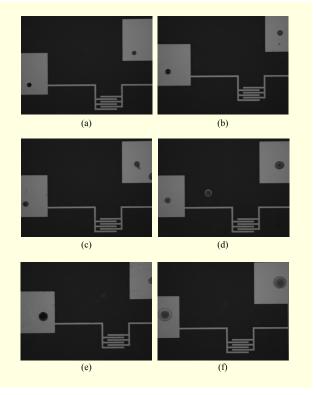

Fig. 7. Optical microscope images of via-hole samples printed using various jetting voltages. Measured sizes of via-holes are approximately (a) 45  $\mu$ m, (b) 60  $\mu$ m, (c) 65  $\mu$ m, (d) 75  $\mu$ m, (e) 85  $\mu$ m, and (f) 130  $\mu$ m.

To increase the integration of printed electronic devices, it is important to reduce the size of the via-holes. Figures 7(a) through 7(f) show optical microscope images of the via-hole samples printed according to various jetting voltages. The operating frequency is 1 kHz and the duty of pulse voltage is half in a cycle. The distance between nozzle and substrate is approximately 0.5 mm, and the temperature is room temperature. The minimum pulse voltage for ejecting the silver

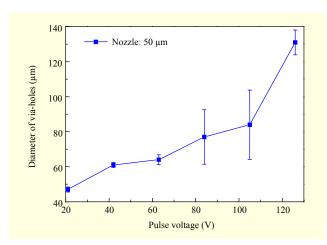

Fig. 8. Plot of pulse voltage dependence of via-hole diameter.

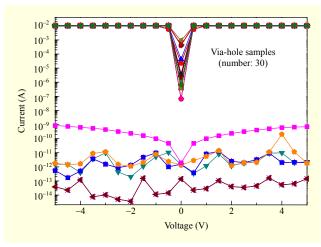

Fig. 9. Plot of current vs. voltage for thirty samples.

ink is approximately 21 V, below which a droplet cannot be formed or ejected. The via-hole result observed at the minimum pulse voltage is shown in Fig. 7(a). The diameter of the via-hole is approximately 45  $\mu$ m. Figure 8 shows the jetting pulse voltage dependence of the average and standard deviation of diameter of the via-holes. When the jetting voltage increases, both the magnitude and the variation of the diameter increases. At a higher jetting voltage, the droplets from the nozzle have a faster speed but are very irregular in size and direction.

To obtain the repeatability of the printed via-holes, we fabricate thirty Al/printed Ag/PMMA/Au capacitors after the via-hole process and measure the *I-V* curves repeatedly. The ramp rate is 20 mV/s. Figure 9 shows a plot of the current versus voltage, which contains all results of the thirty samples. Only the *I-V* curves of five samples do not show a normal conducting path property. Eventually, the measured yield of the via-holes is approximately 83.3%.

### IV. Conclusion

In this study, we investigated the fabrication of contact via interconnections in a PMMA polymer insulator and their electric characteristics using *I-V* measurements. The DC conductivity of Al/printed Ag/PMMA/Au capacitors was measured for various annealing temperatures. When the annealing temperature increased, the amount of embedded Ag in the PMMA increased and the current of the samples increased to compliance. This result indicates that a conducting path for Ag NPs through the PMMA layer may have been made during the inkjet printing and annealing at a high temperature of above 150°C. The yield obtained in the experiment was approximately 83.3% of the electrical repeatability.

### References

- [1] S.S. Yoo et al., "Fabrication of TFTs for LCD Using 3-Mask Process," *J. Inf. Disp.*, vol. 6, no. 3, 2005, pp. 18-21.

- [2] S.J. Park et al., "Realization of 6Mask LTPS CMOS Panel for AMLCD Application," SID Symp. Dig. Tech. Papers, vol. 38, no. 1, 2007, pp. 73-75.

- [3] Nikkei FPD2006: Flat-Panel Display, report, Redondo Beach, CA: InterLingua, 2006, pp. 2-14.

- [4] S. Jurichich, "Summary of the TFT LCD Materials Report," DisplaySearch, 2007, pp. 1-2. http://www.display search.com/products/samples/execsummary-materials.pdf

- [5] W. den Boer and G.S. Smith, "Dual Select Diode AMLCDs: A Path Towards Scalable Two Mask Array Designs," *J. SID*, vol. 13, no. 3, 2005, pp. 199-204.

- [6] S.H. Nam et al., "Enhancement of Roll Printing Accuracy for TFT-LCD," SID Symp. Dig. Tech. Papers, vol. 39, no. 1, 2008, pp. 648-650.

- [7] J. Kim et al., "Influence of Low Molecular Weight PDMS Chains in PDMS-Based Non-photolithography," MRS Proc., vol. 921, 2006, PROC-0921-T06-03.

- [8] T. Shimoda, "Ink-Jet Technology for Fabrication Processes of Flat Panel Displays," SID Symp. Dig. Tech. Papers, vol. 34, no. 1, 2003, pp. 1174-1181.

- [9] M. Lahti, S. Leppävouri, and V. Lantto, "Gravure-Offset Printing Technique for the Fabrication of Solid Films," *Appl. Surface Sci.*, vol. 142, no. 1, Apr. 1999, pp. 367-370.

- [10] H. Sirringhaus et al., "High-Resolution Inkjet Printing of All-Polymer Transistor Circuits," Sci., vol. 290, no. 5499, 2000, pp. 2123-2126.

- [11] A.C. Arias et al., "All-Additive Ink-Jet-Printed Display Backplanes: Materials Development and Integration," *J. SID*, vol. 15, no. 7, 2007, pp. 485-490.

- [12] K.J. Baeg et al., "Polymer Dielectrics and Orthogonal Solvent

Effects for High-Performance Inkjet-Printed Top-Gated P-Channel Polymer Field-Effect Transistors," *ETRI J.*, vol. 33, no. 6, Dec. 2011, pp. 887-896.

- [13] T. Kawase et al., "Inkjet Printed Via-Hole Interconnections and Resistors for All-Polymer Transistor Circuits," *Adv. Mater.*, vol. 13, no. 21, 2001, pp. 1601-1605.

- [14] T. Kawase et al., "Inkjet Printing of Polymer Thin Film Transistors," *Thin Solid Films*, vol. 4438-439, 2003, pp. 279-287.

- [15] Y-Y. Noh and H. Sirringhaus, "Ultra-thin Polymer Gate Dielectrics for Top-Gate Polymer Field-Effect Transistors," *Organic Electron.*, vol. 10, no. 1, Feb. 2009, pp. 174-180.

- [16] InkTec Co., Ltd., product brochure, p. 5. http://www.inktec. com/english/pdf/upload pdf/(E)Electronic Ink 3.3 72dpi(3).pdf

- [17] S. Chung et al., "All-Inkjet-Printed Organic Thin-Film Transistors with Silver Gate, Source/Drain Electrodes," *Jap. J. Appl. Phys.*, vol. 50, 2011, pp. 03CB05 1-03CB05 5.

Yong Suk Yang received his MS and PhD in physics from Pusan National University, Busan, Rep. of Korea, in 1995 and 1999, respectively. In 2001, he joined ETRI, Daejeon, Rep. of Korea, where he has been involved in research on organic and inorganic energy devices. His current research interests include printed

electronics and display by inkjet and large area EHD printing technologies.

**In-Kyu You** received his PhD in material science and engineering from Korea University, where his research focused on process development, defect modeling, and electrical properties for electronic materials. He joined the Memory Institute of Hyundai Electronics in December 1995 as a principal technical

researcher. From 1995 to 1998, he worked as part of the FeRAM team on a FeRAM process integrated device and on PZT ferroelectric thin film development. He joined ETRI, Daejeon, Rep. of Korea, in 1999 and researched and developed a ferroelectric device. Currently, he focuses on printed electronics, such as TFT and memory-based devices. He is a director of the Korea Printed Electronics Association and Korea Printed Research Association.

Hyun Han received his BS and MS from the Department of Chemical & Biological Engineering at Hanbat National University, Daejeon, Rep. of Korea, in 2010 and 2012, respectively, where his research focused on printed circuits for organic electronics and device physics of solution processed organic

devices. He joined the Division of Advanced Materials of the Solar Energy Materials Research Group of KRICT in October 2012 as a researcher. Currently, he focuses on solution processable printed electronics, such as organic thin-film transistors and devices based on organic light-emitting diodes.

Jae Bon Koo received his BS from Korea University, Seoul, Rep. of Korea, in 1994 and his MS and PhD from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Rep. of Korea, in 1996 and 2000, respectively. His PhD work focused on material science and engineering. From 2000 to 2005, he

was a senior researcher with Samsung SDI and worked on the development of backplane TFTs for active matrix organic light-emitting diodes (AMOLEDs). He is currently a principal research engineer with ETRI, Daejeon, Rep. of Korea. His current research interests include the processing and the characterization of printed electronic devices, such as printed TFTs and circuits for the application of next-generation displays.

Sang Chul Lim received his BS and MS in material science and engineering from Hanbat National University, Rep. of Korea, in 1996 and 1999, respectively, and his PhD in material science and engineering from Chungnam National University in 2005. He is currently a senior researcher with ETRI, Daejeon, Rep. of

Korea. His research interests include organic semiconductor devices, flexible electronic device by soluble process, and oxide semiconductor devices.

Soon-Won Jung received his BS from Youngdong University, Yeongdong, Rep. of Korea, in 1998 and his MS and PhD from Cheongju University, Cheongju, Rep. of Korea, in 2000 and 2004, respectively, all in electronic engineering. From 2006 to 2007, he was a full-time lecturer with the Department of Computer

Engineering, Youngdong University. From 2007 to 2009, he was a postdoctoral researcher with ETRI, Daejeon, Rep. of Korea. He is currently a senior researcher with ETRI. He is the author or coauthor of more than 45 peer-reviewed journal papers. His current research interests include the

processing and the characterization of printed electronic devices, nonvolatile memory devices, device physics and process technologies for functional devices, and flexible electronics.

**Bock Soon Na** received her BS in chemistry from Chungnam National University, Daejeon, Rep. of Korea. She joined the Center for Anti-Cancer Research of KRICT in 1996 as a researcher. From 1996 to 2008, She developed anti-cancer drugs that selectively attack only cancer cells and operated NMR. In 2009, She

joined ETRI, Daejeon, Rep. of Korea, and works in printed electronics, such as TFTs and memory-based devices and flexible devices.

Hye-Min Kim received her BS from the Department of Advanced Materials at Hannam University. She was appointed as a researcher on the Energy Application Technology Research Team of KAERI in December 2012. She focuses on synthesis, characterization, and device fabrication using various semiconducting

materials for printed electronics.

**Minseok Kim** received his BS and MS in electronic engineering from Cheongju University, Cheongju, Rep. of Korea, in 2007 and 2009, respectively. From 2009 to 2012, he worked for ETRI, Daejeon, Rep. of Korea, as a researcher and developed roll-printing-based silver nanoparticle patterning and researched its physical properties

for organic/inorganic TFTs. He is currently pursuing his PhD at Korea University, Seoul, Rep. of Korea, where his research is focused on device physics of flexible/printed devices and circuits including organic/inorganic-based semiconducting, dielectric, and conducting materials.

Seok-Hwan Moon received his PhD in mechanical engineering from Sungkyunkwan University, Rep. of Korea, in 1999. Currently, he is the team leader of the Energy Application Technology Research Team at ETRI, Daejeon, Rep. of Korea. He has been researcher in the field of electronic cooling, focusing on micro heat

pipes, for 14 years. His current project deals with heat spreader technologies for LED and CPV.