## High Quality Vertical Silicon Channel by Laser-Induced Epitaxial Growth for Nanoscale Memory Integration

Yong-Hoon Son<sup>1,2,3</sup>, Seung Jae Baik<sup>4,\*</sup>, Myounggon Kang<sup>1</sup>, Kihyun Hwang<sup>1</sup>, and Euijoon Yoon<sup>2,3,5,\*</sup>

Abstract—As a versatile processing method for integration, laser-induced nanoscale memory epitaxial growth is proposed for the fabrication of vertical Si channel (VSC) transistor. The fabricated VSC transistor with 80 nm gate length and 130 nm pillar diameter exhibited field effect mobility of 300 cm<sup>2</sup>/Vs, which guarantees "device quality". In addition, we have shown that this VSC transistor provides memory operations with a memory window of 700 mV, and moreover, the memory window further increases by employing charge trap dielectrics in our VSC transistor. Our proposed processing method and device structure would provide a promising route for the further scaling of state-of-theart memory technology.

*Index Terms*—Vertical silicon channel, laser-induced epitaixal growth, 1T DRAM, floating body effect

## I. INTRODUCTION

Recently, integration of memory cells such as flash or dynamic random access memory (DRAM) confronts

serious scaling issues [1]. In case of DRAM, as an alternative technology with relaxed scaling constraints, capacitor-less one-transistor (1T) DRAM cells have been investigated by several research groups [2, 3]. Impact ionization or gate induced drain leakage generates excess majority carriers in floating body, which switches the channel conductance of metal-oxide-semiconductor field effect transistor (MOSFET) from a low conductance state to a high conductance state [2, 3]. The drain current between two states can then be sensed in the linear operation regime of MOSFET, allowing us to determine memory states. 1T DRAM can be scalable to the minimum unit cell area of  $4F^2$  (F: minimum feature size) in vertical device architecture [3], which provides larger scale integration at the same technology node. Vertical integration of memory cells is also important in recent flash memory development [4], where the effective unite cell size can be reduced below 4F<sup>2</sup> by three dimensional stacked integration. These indicate that the formation of high quality vertical Si channel (VSC) is essential in nanoscale memory integration. In channel-first-gate-last scheme, VSC can be readily formed by etching Si wafers [5] via conventional semiconductor manufacturing processes, but several integration difficulties can be addressed in this scheme: e.g., forming gate electrodes with accurate vertical lengths and controlling sidewall profile or its surface roughness by dry etching [6]. In gate-first-channel-last scheme, high quality VSC can be attained without using Si wafers, which requires selective epitaxial growth techniques on pre-patterned vertical holes as VSC molds. Among selective epitaxial growth techniques [7], laser-induced epitaxial growth (LEG) has been proved to give high quality as Si wafers at low processing temperatures [8]. In this work, we have

Manuscript received Nov. 14, 2013; accepted Feb. 22, 2014 <sup>1</sup> Semiconductor R&D center, Samsung Electronics Co., Ltd.

Gyeonggi-do 449-711, Korea

<sup>&</sup>lt;sup>2</sup> Department of Materials Science and Engineering, Seoul National University, Seoul 151-742, Korea

<sup>&</sup>lt;sup>3</sup> Hybrid Materials Program (WCU), Department of Materials Science and Engineering, Seoul National University, Seoul 151-744, Korea

<sup>&</sup>lt;sup>4</sup> Department of Electrical, Electronic, and Control Engineering, Hankyong National University, Gyeonggi-do 456-749, Korea

<sup>\*</sup>E-mail : sjbaik@hknu.ac.kr

<sup>&</sup>lt;sup>5</sup> Department of Nano Science and Technology, Graduate School of Convergence Science and Technology, Seoul National University, Suwon 443-270, Korea

<sup>\*</sup>E-mail : eyoon@snu.ac.kr

fabricated VSC transistors using the gate-first-channellast scheme using LEG to prove that LEG is an essential element in nanoscale memory integration. In addition, 1T DRAM cell with an ultimate scalability of  $4F^2$  will be demonstrated using the fabricated VSC transistor, whose promising aspect in scaling will also be discussed.

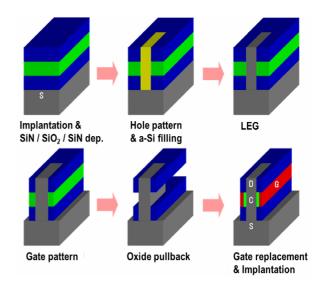

Table 1 show the process sequence and detailed process parameters to fabricate the VSC transistors on a bulk-silicon substrate. Fig. 1 illustrates the sequence of gate replacement process, where single crystalline silicon channel is obtained by LEG process. After the conventional shallow trench isolation process, ion implantations (P<sup>+</sup>, 20 keV, 8×10<sup>12</sup> cm<sup>-2</sup>) were performed to form bottom source and drain junctions. In addition, silicon nitride/silicon oxide/silicon nitride (SiN/SiO<sub>2</sub>/SiN) layers were deposited by low pressure chemical vapor deposition (LPCVD); where the top and bottom SiN layers were used as the isolation layer, and the sandwiched SiO<sub>2</sub> was used for the dummy gate. The holes for transistor channels were patterned by ArFbased photolithography and dry etching. Subsequently, 50 nm-thick amorphous silicon thin film was deposited by LPCVD and then chemical-mechanical polishing process was employed to remove the amorphous silicon on top of the SiN layer. Afterward, in order to perform an epitaxial growth of amorphous silicon in the channel hole area, an Nd:YAG laser beam was irradiated with a wavelength of 532 nm and a pulse duration of 150 ns [9], where the energy density of irradiated laser beam was adjusted to optimize the epitaxial growth. The vertical channel region was doped by  $B^+$  (3×10<sup>13</sup> cm<sup>-2</sup>, 27 keV) implantation to control short channel effect, and top source/drain junction was formed by ion-implanting P<sup>+</sup>  $(10^{13} \text{ cm}^{-2}, 10 \text{ keV})$  and As<sup>+</sup>  $(10^{15} \text{ cm}^{-2}, 10 \text{ keV})$  followed by a rapid thermal annealing at 1000°C for dopant activation. We have used two different types of gate dielectric (SiO<sub>2</sub> and SiO<sub>2</sub>/SiN/SiO<sub>2</sub>) prior to the gate material deposition for a comparative study of 1T DRAM devices. The single dielectric layer SiO<sub>2</sub> of 4 nm is formed by thermal oxidation followed by NH<sub>3</sub> anneal at 900°C, and the multilayered dielectric SiO<sub>2</sub>/SiN/SiO<sub>2</sub> (4 nm/6 nm/6 nm) is fabricated by additional thin film deposition of SiN and SiO<sub>2</sub> using an LPCVD on the 4nm-thick thermal oxide. Finally, we have used doped polycrystalline Si as the gate electrode, followed by the contact formation and metallization using a conventional

Fig. 1. Schematic process sequence of gate replacement process.

**Table 1.** Details of critical process parameters in the fabrication of VSC, and their process sequence.

| Parameters    | Conditions             | Process sequence                                                                                                                                                                                                                                                                                                           |

|---------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pillar height | 150 nm                 | <ul> <li>Shallow trench isolation</li> <li>SiN/SiO<sub>2</sub> layer deposition</li> <li>Channel hole etch</li> <li>Channel Si formation (a-Si dep. &amp; crystallization by LEG)</li> <li>Gate replacement process (oxide etchback, oxidation, poly-Si dep.)</li> <li>Contact formation</li> <li>Metallization</li> </ul> |

| Pillar        | 130 nm                 |                                                                                                                                                                                                                                                                                                                            |

| Gate oxide    | SiO <sub>2</sub> , ONO |                                                                                                                                                                                                                                                                                                                            |

| Channel Si    | a-Si, poly-Si, c-Si    |                                                                                                                                                                                                                                                                                                                            |

| Gate material | Doped Poly-Si          |                                                                                                                                                                                                                                                                                                                            |

| Gate length   | 80 nm                  |                                                                                                                                                                                                                                                                                                                            |

silicon process technology.

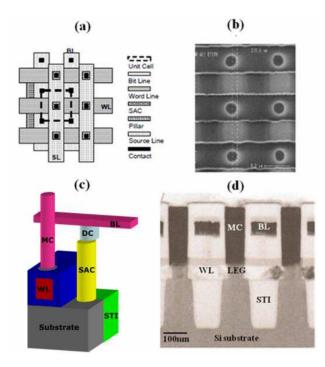

Fig. 2 shows schematic diagrams and electron microscopy images of VSC transistor, where Fig. 2(a) displays the layout of the VSC transistor with the gate all around structure and the unit cell area of  $4F^2$ . The planar scanning electron microscopy (SEM) image in Fig. 2(b) depicts the contact hole with a diameter of 90 nm. Fig. 2(c) illustrates three dimensional schematic representing the unit cell area of 4F2 with stacked word line (WL), bit line (BL), self-aligned contact (SAC) to the active Si, and direct contact (DC) to SAC shifted by 0.5F. In Fig. 2(d), a cross-sectional transmission electron microscopy image of the fabricated VSC transistor is shown, where single crystalline VSC is formed by LEG.

The crystallinity of VSC plays a crucial role in the device performance. The polycrystalline and epitaxial single crystalline silicon channels are prepared by changing the energy density of the incident laser beam

**Fig. 2.** Schematic diagrams and electronic microscopy images of VSC transistors (a) planar layout, (b) planar SEM image, (c) three dimensional illustration, (d) cross sectional TEM image.

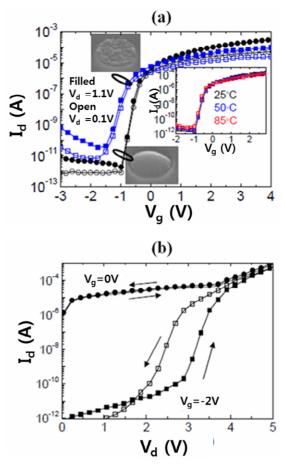

ranging from 700 mJ/cm<sup>2</sup> to 1000 mJ/cm<sup>2</sup> during the LEG process [9-12]. Fig. 3(a) shows the transfer characteristics of the vertical pillar transistor with polycrystalline (900 mJ/cm<sup>2</sup>) and single crystalline (1000 mJ/cm<sup>2</sup>) LEG silicon. For the fabricated transistor with the single crystalline LEG silicon, the electrical characteristics can be summarized as follows: field effect mobility of 300 cm<sup>2</sup>/Vs, threshold voltage of 0.2 V, and sub-threshold slope of 100mV/decade. While the transistor with poly-crystalline silicon shows field effect mobility of 80 cm<sup>2</sup>/Vs, threshold voltage of -0.3 V and sub-threshold slope of 145 mV/decade. In addition, the inset SEM images in Fig. 3(a) indicate different surface morphologies of polycrystaline and single-crystalline Si depending on the energy density of the incident laser beam. Moreover, negligible temperature dependence in leakage currents of VSC transistor with LEG Si indicates high quality crystalline nature (inset graph of Fig. 3(a)) [13, 14].

The drain current of VSC transistor is a function of the potential of VSC, and the potential at VSC is variable according to the charge density in VSC. That is, due to the floating body effect [2, 3], the VSC transistor can be used as 1T DRAM. Drain voltage hysteresis

Fig. 3. (a) Transfer curves of the VSC transistors with polycrystalline (upper curves) and single crystalline (lower curves) VSC. Inset shows the planar SEM images of surface morphologies of poly crystalline (upper image) and single crystalline LEG Si (lower image). Right inset shows temperature dependent transfer curves of VSC transistor with single crystalline Si channel, (b) The output characteristics (semi-logarithmic current versus voltage) of VSC transistor with hysteresis measurement.

demonstrates the floating body effect as shown in Fig. 3(a). Considering that the measurement time of hysteresis sweep was estimated to be around 100 ms, the memory window determined from this drain voltage implies the memory window for the 100ms retention time. As shown in Fig. 3(a), the memory window is 0 V at the gate bias of 0 V, while memory window of 0.7 V is observed with the gate bias of -2 V. This implies that an additional negative gate bias is required for sensing with refresh time around 100 ms in our VSC 1T DRAM. Applying a negative bias of -2 V on the gate provides a deeper potential well for the storage of excess holes inside the vertical silicon channel, which increases the memory window and retention time [2, 3].

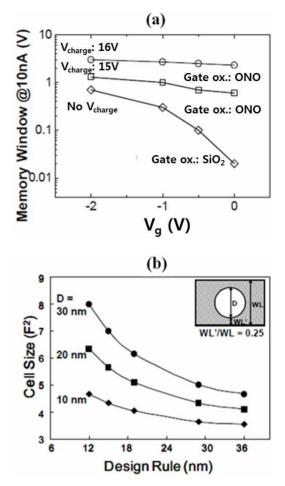

Electron trapping at the gate insulator is an alternative strategy for the enhancement of the memory window instead of the negative gate bias. To prove this concept, two types of gate dielectrics, i.e.,  $SiO_2$  and  $SiO_2/$  $SiN/SiO_2$  (ONO), were compared to observe the further enhancement of memory window. The former is almost trap-free dielectric, and the latter has a trap-rich SiN layer between trap-free SiO<sub>2</sub> layers. Prior to applying drain bias for the hyeteresis measurement, charging bias (V<sub>charge</sub>) was applied to trap electrons in the gate dielectrics. In an ONO gate dielectric, electrons are charged in nitride layer by tunneling through the bottom oxide, which is a well-known mechanism in charge trap flash memories [15]. The negative charges in the gate dielectric enhance the junction barrier between the channel and source/drain. As shown in Fig. 4(a), electron trapping at ONO gate dielectric enhances memory window, and this enhancement increases with more electron trapping by increasing V<sub>charge</sub>. Charge retention of ONO can be larger than 10 years [15], and thus, V<sub>charge</sub> is necessary only during the memory production. This approach based on charge trapping gives more promising options in the application VTC 1T DRAM since negative voltages are not required for device operations.

In scaling VTC 1T DRAM, the diameter of the pillar is the key parameter in determining the cell size. Fig. 4(b) shows simulated cell size of VTC 1T DRAM versus design rule, where several pillar diameters are used and the width of WL is set twice of the design rule. It is seen that VTC 1T DRAM can provide a solution for high density DRAM with the cell area of about  $4F^2$  when structure parameters are optimized, that is, smaller pillar diameter is crucial. To attain ultimate scalability in VTC 1T DRAM, development of patterning and dry etching technologies for nano-sized holes would be important; and further investigation on the performance of LEG in nano-sized pillars is also required.

In summary, we have demonstrated that LEG is a promising process method for nanoscale memory integration by demonstrating high performance VSC transistors with field effect mobility around 300 cm<sup>2</sup>/Vs. In addition, we have demonstrated a VSC 1T DRAM by employing charge trap gate dielectric, which exhibited enhanced memory window as the amount of charge trapping increased. We believe that high quality VSC by LEG is a promising elements in future nanoscale

**Fig. 4.** (a) Memory window versus applied gate bias at various charging conditions, (b) Simulated cell size (the unit is the square of the minimum feature size F) of VSC transistor versus design rule, where three pillar diameters are applied.

memory integration, and in particular, VSC 1T DRAM harnessing charge trap dielectric will provide a solution for scaled DRAM below 20 nm.

## ACKNOWLEDGMENTS

This research was supported by BK21 plus program and WCU Hybrid Materials Program, Department of Materials Science and Engineering, Seoul National University, Korea, funded by Ministry of Education, Science and Technology.

## REFERENCES

- [1] K. Kim, Technical Digest of IEEE International Electron Device Meeting 2010, p. 1, 2010

- [2] T. Ohsawa, K. Fujita, T. Higashi, Y. Iwata, T.

Kajiyama, Y. Asao, and K. Sunouchi, IEEE J. Solid-State Circuits, 37, pp.1510-1522, 2002

- [3] E. M. Vogel, Nature Nanotechnology, Vol.2, pp.25-32, 2006

- [4] H.-S. Kim, W. Cho, H. Cho, J. Kim, S. I. Shim, Y. Jang, J.-H. Jeong, B.-K. Son, D. W. Kim, K. Hwang, J.-J. Shim, J. S. Lim, K.-H. Kim, S. Y. Yi, J.-Y. Lim, D. Chung, H.-C. Moon, S. Hwang, J.-W. Lee, Y.-H. Son, U.-I. Chung, and W.-S. Lee, 2009 Symposium on VLSI Technology, pp. 192-193 (2009)

- [5] S. Hall, C. H. De Groot, V. D. Kunz, and P. Ashburn, IEEE Transactions on Electron Devices, Vol. 51, Issue. 1, pp. 158-161 (2004)

- [6] S. J. Ahn, G. H. Koh, K. W. Kwon, S. J. Baik, G. T. Jung, T. N. Hwang, H. S. Jeong, and K. Kim, Technical Digest of IEEE International Electron Devices Meeting 2003, pp.10.4.1-10.4.4 (2003)

- [7] T. O. Sedgwick, M. Berkenblit, and T. S. Kuan, Applied Physics Letters, Vol. 54, Issue. 26, pp. 2689-2691 (1989)

- [8] Y.-H. Son, S. J. Baik, S. Jeon, J.-W. Lee, G. Hwang, Y. G. Shin, and E. Yoon, IEEE Transactions on Electron Devices, Vol. 58, No. 11, pp.3863-3868 (2011)

- [9] Y.-H. Son, J.-W. Lee, P. Kang, M.-G. Kang, J. B. Kim, S. H. Lee, Y.-P. Kim, I. S. Jung, B. C. Lee, S. Y. Choi, U.-I. Chung, J. T. Moon, and B.-I. Ryu, 2007 Symposium on VLSI Technology Digest of Technical Papers, pp. 80-81, 2007

- [10] J. S. Im, H. J. Kim and M. O. Thompson, Applied Physics Letters, Vol. 63, No. 14, pp. 1969-1971 (1993)

- [11] V. V. Gupta, H. J. Song, and J. S. Im, Vol. 71, No. 1, pp.99-101, 1997

- [12] S. D. Brotherton, D. J. McCulloch, J. P. Gowers, J. R. Ayres, and M. J. Trainor, Journal of Applied Physics, Vol. 82, No. 8, pp.4086-4094, 1997

- [13] H.-L. Chen and C.-Y. Wu, IEEE transactions on electron devices, Vol. 45, No. 10, pp. 2245-2247, 1998

- [14] C. H. Kim, K-S. Sohn, and J. Jang, J. Appl. Phys. 81, pp.8084-8090, 1997

- [15] S. J. Baik, K. S. Lim, W. Choi, H. Yoo, J.-S. Lee, and H. Shin, Nanoscale, 3, pp. 2560-2565 (2011)

**Yong-Hoon Son** received the B.S. and M.S. degrees in materials science and engineering from Hongik University, Seoul, Korea, in 2000 and 2002, respectively. He is currently working toward the Ph.D. degree in the Department of

Materials Science and Engineering, Seoul National University, Seoul, with a scholarship from Samsung. In 2002, he joined the Process Development Team, Semiconductor Research and Development Center, Samsung Electronics Company, Ltd., Yongin, Korea, where he had been engaged in research on epitaxy for 3-D SRAM and 3-D NAND development from 2002 to 2009. He is the holder of 114 U.S patents and invented the terabit cell array transistor (TCAT) for 3-D NAND Flash devices. His current research interests are Ge epitaxy for 3-D devices and optoelectronics.

Seung Jae Baik received the B.S., M.S., and Ph.D. degrees from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1994, 1996, and 2001, respectively, all in electrical engineering. From 2001 to 2009, he was

with Samsung Electronics Company, Ltd., Yongin, Korea, where he contributed to novel Si devices, highdensity Flash memory devices, and charge trap Flash memory devices, as a Senior Engineer and Principal Engineer. From 2009 to 2012, he has been with KAIST as a Research Professor; where he did research works on amorphous Si based solar cells, colloidal quantum dot based solar cells, and memory materials. Since 2012, he has worked as an assistant professor in Hankyong National University. His current research interests include high-density/novel memory devices, thin-film Si solar cells, and nanostructured devices.

**Myounggon Kang** received Ph.D. degree in the department of electrical engineering, Seoul National University, Seoul, Korea. He is currently Samsung Electronic Company, Kyungido Korea. His current research interests are circuit design of High Density NAND flash

memory and NAND cell compact modeling.

Kihyun HWANG received the B.S., M.S., and Ph.D. degrees in Material Science and Engineering from Seoul National University, Korea, in 1991, 1993, and 1997, respectively. In 1996, he joined Samsung Electronics Company, Ltd., Gyunggi-Do, Korea.

He has been responsible for NAND flash memory process and DRAM capacitor structure and materials. Currently, he has been vice president of Samsung Electronics Co., Ltd..

**Euijoon Yoon** received the B.S. and M.S. degrees in materials science and engineering from Seoul National University, Seoul, Korea, in 1983 and 1985, respectively, and the Ph.D. degree in electronic materials from Massachusetts Institute of

Technology, Cambridge, in 1990, where he worked on low temperature heteroepitaxy of GaAs on Si by plasmaenhanced metal-organic chemical vapor deposition (MOCVD). After his Ph.D., he was with AT&T Bell Laboratories, Murray Hill, NJ, as a Postdoctoral Member of the Technical Staff from 1990 to 1992, where he worked on hydrogen plasma passivation of III-V surfaces and its in situ real-time monitoring. Subsequently, he joined Seoul National University in 1992, where he worked on heteroepitaxy of SiGe and SiGeC on Si by ultrahigh vacuum chemical vapor deposition, heteroepitaxy of III-V and III-nitride semiconductors by MOCVD, and their applications to light-emitting diodes for solid-state lighting. From July 1998 to July 1999, he stayed at University of California, Santa Barbara, as a Visiting Professor. Since 2008, he has been in charge of a national project on highefficiency solid-state lighting supported by the Korean Government. Dr. Yoon served as the Program Chair of the 8th International Conference on Nitride Semiconductors (ICNS-8), Jeju, Korea, in 2009. Currently, he serves as the Chair of the 16th International Conference on Metal-Organic Vapor Phase Epitaxy (ICMOVPE-XVI), Busan, Korea, in May 2012.