# 技術論文

J. of The Korean Society for Aeronautical and Space Sciences 42(9), 789-794(2014)

DOI:http://dx.doi.org/10.5139/jKSAS.2014.42.9.789

# FPGA 열제어용 히트싱크 효과의 실험적 검증

박진한\*, 김현수\*, 고현석\*\*, 진봉철\*\*, 서학금\*\*

# Experimental Verification of Heat Sink for FPGA Thermal Control

Jin-Han Park\*, Hyeon-Soo Kim\*, Hyun-Suk Ko\*\*, Bong-Cheol Jin\*\* and Hak-Keum Seo\*\* Samsung Thales\*, Agency for Defense Development\*\*

# **ABSTRACT**

The FPGA is used to the high speed digital satellite communication on the Digital Signal Process Unit of the next generation GEO communication satellite. The high capacity FPGA has the high power dissipation and it is difficult to satisfy the derating requirement of temperature. This matter is the major factor to degrade the equipment life and reliability. The thermal control at the equipment level has been worked through thermal conduction in the space environment. The FPGA of CCGA or BGA package type was mounted on printed circuit board, but the PCB has low efficient to the thermal control. For the FPGA heat dissipation, the heat sink was applied between part lid and housing of equipment and the performance of heat sink was confirmed via thermal vacuum test under the condition of space qualification level. The FPGA of high power dissipation has been difficult to apply for space application, but FPGA with heat sink could be used to space application with the derating temperature margin.

## 초 록

정지궤도급 차세대 통신위성에 탑재될 디지털신호처리기에는 디지털 고속통신을 위한 FPGA가 사용된다. 적용된 FPGA는 높은 열소산량을 가지고 있으며, 이로 인한 접합온도의 상승은 부하경감 요구조건을 만족하기 어렵고 장비의 수명과 신뢰도 저하의 주요 원인이다. 지상과는 달리 우주환경에서의 전장품의 열제어는 대부분 열전도를 통하여 이루어지고 있다. CCGA 또는 BGA 형태의 FPGA는 인쇄회로기판에 장착되지만, 인쇄회로기판의 열전도율은 FPGA의 열제어에 효율적이지 못하다. FPGA의 열제어를 위하여 부품 리드와하우징을 직접 연결하는 히트싱크를 제작하였으며, 우주인증레벨의 열진공시험을 통하여그 성능을 확인하였다. 높은 전력소모량을 가진 FPGA는 우주환경에 적용하기 어려웠으나, 히트싱크를 적용함으로써 부하경감 온도 마진을 확보하였다.

Key Words : Thermal Analysis(열해석), Derating Requirement(부하경감 요구조건), Junction Temperature(접합온도), FPGA(Field Programmable Gate Array), Thermal Vacuum Test(열진공시험)

<sup>†</sup> Received: June 27, 2014 Accepted: August 7, 2014

<sup>\*</sup> Corresponding author, E-mail: jinhan22.park@samsung.com

# I. 서 론

전자부품 및 전장품을 설계할 때 열적인 영향에 대한 고려가 중요한 요소로 대두되고 있다. 현대의 전자 부품들은 더 빠르고 좋은 능력에 대한 요구에 의하여 회로의 밀도와 열소산의 증가가 필연적으로 동반되고 있다[1]. 전자부품의 부하경감 요구조건(Derating Requirement)을 만족하기 위하여 높은 열소산 부품에 대한 열제어가 필요하며, 그 필요성을 구체적으로 살펴보면 다음과 같다. 전자부품의 높은 접합온도는 전류의증가를 야기하고 이는 열소산의 증가로 이어진다. 이러한 결과는 다시 접합온도의 증가를 야기하는 악순환을 발생시키며, 결국 부품의 실패를초래한다. 그리고 접합온도 및 부품온도는 신뢰도와 역수 관계에 있다. 즉 온도가 올라가게 되면 부품의 신뢰도가 떨어진다[2].

정지궤도급 차세대 통신위성용 디지털신호처리기에서는 디지털 고속통신을 위하여 FPGA가사용되고 있다. 적용된 FPGA는 전력소모량이 10W에 이르며, 높은 부품 온도 및 접합온도의상승으로 인하여 부하경감 요구조건을 만족시키기 어렵고 결과적으로 신뢰도 저하의 주요 원인이 되고 있다.

지상에서의 전력소모량이 큰 전자부품의 열제어는 주로 냉각팬 등과 같은 대류에 의하여 이루어지나, 우주환경에서의 전자부품의 열제어는 대부분 전도에 의해서만 이루어진다. CCGA (Ceramic Column Grid Array) 또는 BGA(Ball Grid Array) 형태인 FPGA의 기존 열전달은 인쇄회로기판과 하우징 및 이들의 접합면을 통하여이루어지고 있다. 금속에 비하여 상대적으로 매우 낮은 인쇄회로기판의 열전도율은 FPGA의 열제어에 효율적이지 못하며, 별도의 열전달 경로가 필요하다.

본 논문의 연구 목적은 높은 전력소산량을 가진 FPGA의 열제어를 위하여 추가적인 열전달경로인 히트싱크를 추가하고, 부하경감 요구조건을 만족시킴으로써 정지궤도 위성에 적용 가능성을 확인하는 것이다.

# Ⅱ. 본 론

# 2.1 열해석 결과

#### 2.1.1 열해석 방법

본 논문에서는 디지털신호처리기의 열해석을 위하여 노드 네트워크 모델링(Nodal Network Modeling)

Fig. 1. Thermal Conduction through 2-dimensional Plate

방법으로 모델링하였다. 이 방법은 열 해석시에 가장 많이 사용되는 모델링 방법으로서 열 해석할 대상을 일정한 수의 노드로 분할을 한 뒤 노드와 노드를 열저항으로 연결시키는 방법이다[3].

평면에서의 1차원 전도에 대하여, 온도는 x 좌 표만의 함수이며 열은 이 방향으로만 전달된다. Fig. 1에서 열전달은  $T_{s,1}$ 인 곳에서  $T_{s,2}$ 인 곳으로의 전도를 통하여 일어난다. 먼저 벽 내부의 조건을 고려하여 전도 열전달률을 얻을 수 있는 온도분포를 구하고자 하는데, 이는 적당한 경계조건으로 열 방정식을 풀어 결정할 수 있다. 온도분포로부터 전도 열전달률을 구하기 위하여 Fourier 법칙을 사용한다[4].

$$q_x = -kA \frac{dT}{dx} = \frac{kA}{L} (T_{s,1} - T_{s,2})$$

(1)

여기서 k는 열전도율(thermal conductivity), A는 열전달 방향에 수직한 벽의 면적이며, 평면 벽에서는 x에 무관하게 일정하다. 열 확산과 전기 충전 사이에는 유사성이 존재한다. 전기저항이 전기전도에 관계가 있는 것과 같이 열저항은 열전도에 관계가 있다. 저항을 전달률에 대한구동 포텐셜(driving potential)의 비율로서 정의한다면, 식 (1)로부터 전도 열저항은 다음 식 (2)와 같다[1].

$$R_{t, cond} \equiv \frac{T_{s, 1} - T_{s, 2}}{q_{x}} = \frac{L}{kA}$$

(2)

열 모델링의 온도계산을 위하여 상용 프로그램인 TAS(Thermal Analysis System, Havard Thermal Inc.)을 사용하였다. TAS는 각 노드의 온도를 계산하기 전에 기본적으로 열저항, 플레이트 모델링, 복사 등으로 구성되어 있는 전체 열 모델링을 노드 네트워크 형식으로 변환한다. TAS는 노드와 노드사이의 에너지 균형이 일어나는 정상

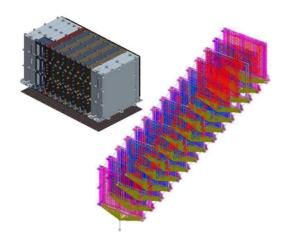

Fig. 2. Configuration of Digital Signal Process Unit(left) and Thermal Model (right)

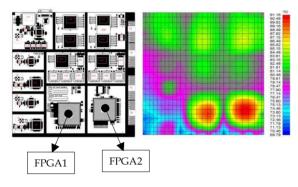

Fig. 3. DSP Board and Thermal Analysis

Result

상태에서의 온도 분포를 얻기 위해 유한차분법을 사용한다[3].

Figure 2는 차세대 통신위성용 디지털신호처리 기의 형상 및 열모델이다.

## 2.1.2 열해석 결과

디지털신호처리기의 열해석은 인증온도(Qual. level temperature)인 장착면 온도 +65℃를 기준으로 이루어 졌으며, FPGA가 위치하는 DSP보드의 온도는 각각 +91℃(FPGA1)와 +90℃(FPGA2)이다. DSP보드의 부품배치 및 온도분포는 Fig. 3과 같다.

#### 2.1.3 FPGA 접합온도

디지털신호처리기의 열해석은 인증레벨의 장착면 온도인 +65℃를 기준으로 수행되었고, 장착면 온도가 실제 위성에 탑재되었을 때의 온도(Acceptance level temperature)는 +60℃이다. 보드레벨의 온도가 장착면 온도에 대하여 선형적으로 변화한다고 가정하면, FPGA가 위치한 보드의온도는 열해석온도에서 5℃가 낮은 +86℃와 +85℃이다.

Table 1. Junction Temperature Margin of FPGA from Thermal Analysis Results

| Part  | Power<br>Dissi.<br>[W] | Ть<br>[℃] | Rj-b<br>[℃/W] | Tj<br>[℃] | Tjmax<br>[℃] | Tj-derated<br>[℃] | Margin<br>[℃] |

|-------|------------------------|-----------|---------------|-----------|--------------|-------------------|---------------|

| FPGA1 | 9.6                    | +86.0     | 2.2           | +107.1    | +125.0       | +85.0             | -22.1         |

| FPGA2 | 9.6                    | +85.0     | 2.2           | +106.1    | +125.0       | +85.0             | -21.1         |

Tb: Board level temperature from thermal analysis, assuming acceptance level

Rj-b: Resistance between board to junction

Tj: calculated junction temperature

Tjmax: allowable max. junction temperature

Tj-derated: derated-junction temperature,

referenced from ECSS-Q-ST-30-11,

디지털신호처리기에 적용된 FPGA의 열소산량은 9.6W로 계산되어지며, 보드와 FPGA 접합부사이의 열저항(R<sub>j-b</sub>)은 2.2℃/W이다[5].

디지털신호처리기의 실제 사용온도인 60℃를 가정한 FPGA의 접합온도(T<sub>i</sub>)는 Table 1과 같이 +107.1℃(FPGA1)와 +106.1℃(FPGA2)로 계산되어 진다.

유럽우주기구(ESA) ECSS-Q-ST-30-11은 FPGA에 대한 부하경감 지침으로 최대 접합온도(T<sub>jmax</sub>)에서 40℃를 차감하여 적용할 것을 권장하고 있다[6]. 본 논문에서 적용한 FPGA의 최대 접합온도(T<sub>jmax</sub>)는 +125℃이므로 ECSS-Q-ST-30-11의 지침을 적용한 부하경감 접합온도(T<sub>j-derated</sub>)는 +85℃이다.

ECSS-Q-ST-30-11의 부하경감 지침을 적용하였을 때 2개의 FPGA 모두 20℃정도의 역마진이발생했으며, 인쇄회로기판의 열전도를 통한 열제어만으로는 FPGA의 부하경감 요구조건을 만족하기 어려움을 알 수 있다.

#### 2.2 히트싱크

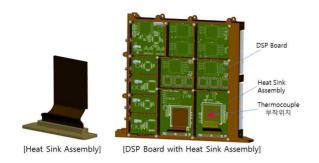

#### 2.2.1 히트싱크 형상

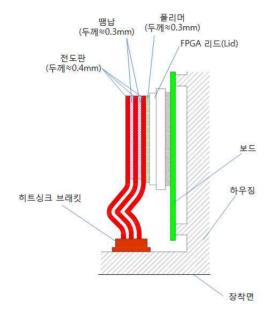

FPGA의 열전도 경로 추가를 위한 히트싱크는 FPGA 리드(Lid)부분의 열을 전달하는 전도판, 전도판을 하우징에 고정시키기 위한 브래킷, FPGA 리드와 전도판 사이 및 브래킷과 전도판 사이를 고정하기 위한 폴리머 등으로 구성된다. Fig. 4 및 Fig. 5는 히트싱크의 형상과 DSP보드의 형상을 보여준다.

### 2.2.2 전도판

FPGA에서 발생한 열을 장착면으로 전달하는 전도판은 넓은 단면적을 가질수록 유리하나 단면 적이 크게 되면 강성도가 비례하여 증가한다.

Fig. 4. DSP Board with Heat Sink Assembly

Fig. 5. Detail View of Heat Sink Assembly

궤도환경에서 발생하는 열주기로 인하여 전도 판은 수축 및 팽창을 반복하게 되며, 이로 인한 열응력은 FPGA로 전달된다. 또한 발사환경에서 발생하는 진동 및 충격 하중 역시 전도판을 통하 여 FPGA로 전달된다.

궤도환경의 열응력 및 발사환경의 진동 및 충격 하중 전달은 전도판의 강성에 비례하여 증가하며, FPGA의 손상을 초래할 수 있다.

전도판에 의한 FPGA로의 하중 전달을 최소화하고, 열전도율을 높이기 위해 얇은 구리판 3장을 겹쳐 제작하였으며, 진동 및 충격 완화를 위한 굽힘 형상으로 제작되었다.

전도판의 재질은 열전도율이 높은 구리 재질을 사용하였으며, 표면은 니켈도금이다. 3장의 전도판 사이의 고정은 FPGA 상단부분에 한하여 연납(Sn63Pb37)을 적용하였다.

#### 2.2.3 폴리머 접착

FPGA의 리드의 재질은 SiC로서 매우 낮은 열 팽창율(Thermal Expansion Coefficient)인 2.77 x

Table 2. Properties of DIS-A-PASTE 2310-PMF [7]

| Item                                   | Property                       |  |  |

|----------------------------------------|--------------------------------|--|--|

| Hardness                               | Durometer A 80                 |  |  |

| Lap shear, @+25℃, Al to Al, [psi]      | 360                            |  |  |

| Tensile strength [psi]                 | 350                            |  |  |

| Elongation [psi]                       | 70                             |  |  |

|                                        | 550 @55℃                       |  |  |

| Young's modulus [psi]                  | 650 @25℃                       |  |  |

|                                        | 1650 @-60℃                     |  |  |

| Glass transition temperature [℃]       | -72                            |  |  |

| Thermal expansion coefficient          | alpha 1 : 50x10 <sup>-6</sup>  |  |  |

| [in/in/℃]                              | alpha 2 : 160x10 <sup>-6</sup> |  |  |

| Thermal conductivity, @+25℃            | 0.84                           |  |  |

| [W/mK]                                 |                                |  |  |

| Outgassing @ 10 <sup>-6</sup> torr [%] | TML: 0.51                      |  |  |

| Outgassing @ 10 torr [%]               | CVCM: 0.04                     |  |  |

| Volume resistivity, @+25℃              | 1.0x10 <sup>-15</sup>          |  |  |

| [ohm-cm]                               | 1.0x10                         |  |  |

| Usual Temperature Range [℃]            | -72 ~ +225                     |  |  |

10<sup>6</sup> °K이며, 구리 재질의 히트싱크 전도판의 열 팽창율은 17 x 10<sup>6</sup> °K이다. FPGA 리드와 히트싱크 구리판을 고정하는 접착물질은 약 6배정도 차이의 열팽창율을 가진 이 두 물질의 수축 및 팽창에 대한 응력을 흡수할 수 있어야 한다.

또한 열진공 등 우주환경에 적합한 탈가스 (Outgassing) 특성을 가지고 있어야 한다. FPGA 리드와 히트싱크를 고정한 폴리머(DIS-A-PASTE 2310-PMF)의 특성은 Table 2와 같다.

#### 2.2.4 히트싱크 브래킷

FPGA에서 발생한 열을 효율적으로 전달시키기 위하여, 3장의 전도판은 브래킷에 고정되고, 브래킷은 DSP 보드의 위성체 장착면과 가장 가까운 하우징 몸체에 고정된다. 전도판과 브래킷의 고정은 FPGA 리드와 전도판을 고정한 동일폴리머를 사용하였다. 브래킷은 일반적인 위성전장박스 재질인 Al6061-T651을 사용하였다.

### 2.3 열진공시험

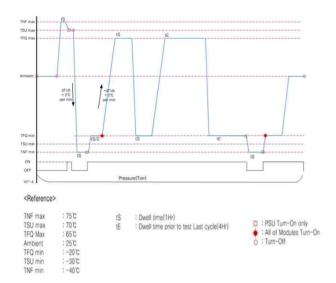

## 2.3.1 열진공 시험 온도 규격

디지털신호처리기의 우주인증레벨 열진공 시험은 10주기로 정의되어 있으나, 장비의 동작 안정성 및 설계마진 확인을 위한 3주기 시험을 선진행하였으며, 추후 정식 열진공시험을 수행할계획이다. 사전 수행한 열진공시험 온도규격 및프로파일은 Fig. 6과 같다.

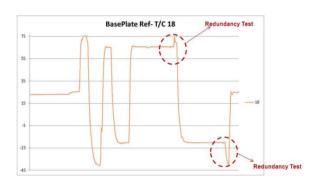

# 2.3.2 열진공 시험 수행

온도 측정용 서모커플(Thermocouple)은 디지털신호처리기 외부 표면에 18개, 내부 인쇄회로 기판 및 부품 표면에 38개를 부착하였다. 본 논

Fig. 6. Thermal Vacuum Test Profile

Fig. 7. Temperature Variation of Thermal Vacuum Test

문에서 주요 관심사인 FPGA의 온도 측정은 서 모커플의 수량 제한으로 인하여 높은 해석 온도 를 가진 FPGA1에만 부착하여 수행하였다.

열진공 시험은 인증레벨(Qualification Level)인 저장온도  $-40^{\circ}$ ~+75 $^{\circ}$ , 저온전원시험온도  $-30^{\circ}$ , 동작온도  $-20^{\circ}$ ~+65 $^{\circ}$ 의 범위에서 수행되었으며, 시험중 진공도는  $1X10^{\circ}$  torr 이하로 유지되었다.

Figure 7는 열진공 시험 중 디지털신호처리기 장착면의 온도 변화이다.

# 2.3.3 열진공 시험 결과

디지털신호처리기의 열진공 시험 중 고온은 인증레벨인 +65℃로 수행되었고, 이 때 FPGA리드 상단부분의 히트싱크에 부착된 서모커플의온도는 +82.6℃로 측정 되었다. 주위온도가 실제우주에서의 사용 온도(Acceptance level temperature)인 +60℃로 변경되었을 때, 부품의온도가 선형적으로 변화한다고 가정하면, 궤도상에서의 히트싱크 상단의 온도는 최대 +77.6℃으로 유추할 수 있다.

Table 3. Temperature of FPGA Lid

| Temp. of<br>Heat Sink<br>[℃] | FPGA Power<br>Dissipation<br>[W] | Rc−h<br>[°C/W] | Temp. of<br>FPGA Lid<br>[℃] |  |

|------------------------------|----------------------------------|----------------|-----------------------------|--|

| +77.6                        | 9.6                              | 0.2            | +79.5                       |  |

Rc-h: resistance between FPGA lid to the top of heat sink

Table 4. Junction Temperature of FPGA with Heat Sink from Thermal Vacuum Test

| Part  | Power<br>Dissi.<br>[W] | T₀<br>[℃] | Rj-c<br>[℃/W] | Tj<br>[℃] | Tjmax<br>[°C] | Tj-derated | Margin<br>[℃] |

|-------|------------------------|-----------|---------------|-----------|---------------|------------|---------------|

| FPGA1 | 9.6                    | +79.5     | 0.1           | +80.5     | +125.0        | +85.0      | +4.5          |

T<sub>c</sub>: temperature of FPGA lid

$R_{i-c}$ : resistance between FPGA lid to junction

T<sub>j</sub>: junction temperature

T<sub>jmax</sub>: allowable max. junction temperature

T<sub>j-derated</sub>: derated-junction temperature,

referenced from ECSS-Q-ST-30-11

#### 2.3.4 FPGA 접합온도

히트싱크 상단과 FPGA 리드 사이의 열전달은 전도판, 전도판 사이의 연납 및 폴리머로 구성되 며, 총 열저항(Rc-h)은 약 0.2℃/W이다. FPGA 리 드 부분의 온도는 Table 3과 같이 계산되어 진 다

Table 4에서 보이는 바와 같이 FPGA의 접합 온도(Tj)는 +80.5℃로 계산되어 지며, 부하경감 요 구조건(Tj-derated)인 +85℃에 대하여 약 +4.5℃이상 의 마진을 확보하였다.

#### Ⅲ. 결 론

정지궤도급 차세대 통신위성에 탑재될 디지털 신호처리기의 열해석 결과 디지털 고속통신을 위 하여 사용된 FPGA의 접합온도가 과도하게 상 승하였으며, 이러한 문제는 장비의 수명과 신뢰 도 저하의 주요 원인이 될 수 있다.

지상제품과 달리 우주환경에서는 대부분 전도에 의해서 전자부품의 열제어가 이루어지며, 높은 전력소모율을 가지고 있는 FGPA와 같은 전자부품은 기존 인쇄회로기판으로의 열전도만으로는 부하경감 요구조건을 만족하기 어렵다.

접합부와 FPGA 리드 사이의 열저항( $R_{j-c}$ )이 접합부와 인쇄회로기판 사이의 열저항( $R_{j-b}$ )보다 작기 때문에, FPGA 리드를 통한 열전도가 훨씬 효

율적이다.

10W급의 전력소모량을 가지고 있는 FPGA의 열제어를 위해서 별도의 히트싱크를 제작하였으 며, 열진공시험 결과 부품 부하경감 온도 마진을 충분히 확보하였다.

디지털 고속통신에 필요한 높은 성능의 FPGA는 우주의 열적환경 특성상 적용의 제약이 있었으나, 본 논문에서 제시된 열제어 방법을 통하여정지궤도 통신위성에 적용 가능함을 확인하였다.

## References

1) Jin-Han Park, Hyeon-Seok Seo, Yeoung-Keun Jang, "A Study on Heat Load Mitigation for High Power Dissipation Equipment of KOMPSAT-2", KSAS *Journal*, No. 30, Vol. 3, pp. 77~88, 2002.

- 2) Michael Pecht, Handbook of Electronic Package Design, Marcel Dekker , Inc., New York, 1991.

- 3) Min-Young Kang, Jin-Han Park, Yeoung-Keun Jang, Hwa-Seok Oh "A Study on Thermal Modeling Method of Satellite Equipment", KSAS *Journal*, No. 29, Vol. 7, pp. 127~136, 2001.

- 4) Frank P. Incropera, David P. DeWitt, Fundamentals of Heat and Mass Transfer, John Wiley and sons, 1996

- 5) UG520, Virtex-5QV FPGA Packaging and Pinout Specification, Xilinx Inc.

- 6) ECSS-Q-ST-30-11, Derating EEE components, ESA Requirements and Standards Division

- 7) Technical Data & Information of DIS-A-PASTE 2310-PMF, Aptek Laboratories, Inc.