# **Current-Steered Active Balun with Phase Correction**

Ji An Park, Ho Jeong Jin, and Choon Sik Cho

Abstract—An active balun using current steering for phase correction is presented. The proposed active balun is constructed with two different unit balun structures based on current steering to reduce phase and amplitude errors. This type of topology can be compared with the conventional phase and amplitude correction techniques which do not incorporate the current steering. Designed and fabricated active balun in 0.18 μm CMOS process operates over 0.95 - 1.45 GHz band, showing input reflection coefficient under -15 dB, phase error of 11° and gain error of 0.5 dB. Gain is measured to be 0.3 dB maximum and power consumption of 7.2 mW is measured.

Index Terms—Active balun, current steering, phase correction technique, phase imbalance, gain imbalance

#### I. Introduction

In wireless communication systems a number of circuits are designed using differential structure because of less even-order distortion and common-mode noise. However since antenna usually takes single port, balun is indispensable for conversion of single-ended signal to differential signal and vice versa. Baluns take two types in passive or active circuits. Passive baluns can be fabricated in on-chip for millimeter-wave systems, leading to signal attenuation [1]. To tackle this inherent weakness, active baluns have been paid considerable attentions [2-4].

Manuscript received Apr. 10, 2015; accepted Sep. 2, 2015 This research was supported by IDEC (IC Design Education Center). School of Electronics and Information Engineering, Korea Aerospace University, Goyang, Korea

E-mail: cscho@kau.ac.kr

Phase correction technique has been sometimes used for active baluns, where inevitable phase imbalance can be alleviated by adjusting the phase of balanced output signals adequately [5]. The conventional active baluns capitalize opposite frequency-vs-phase responses of two different amplifiers which can be mainly made up of common source and common gate configurations. Due to inherent different phase response between these two configurations, it is quite difficult to obtain exactly same amplitude and opposite phase characteristics using these amplifier configurations for constituting excellent active baluns in terms of low amplitude and phase errors.

In this work, we devise an active balun using current steering to provide pliable gain and phase adjustment based on two different unit balun structures, leading to low phase and gain errors. Design philosophy and fabricated results are presented along with simulation and layout in 0.18 µm CMOS technology.

#### II. THE PROPOSED ACTIVE BALUN

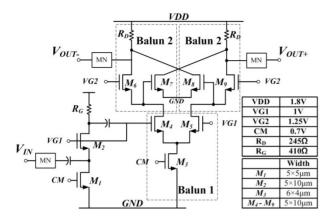

The fundamental principle of active baluns uses the characteristic of MOSFET amplifiers which can provide opposite phase responses for common-source and common-gate configurations [6-9]. The proposed active balun comprised of two different unit circuits is drawn in Fig. 1, where M<sub>1</sub> and M<sub>2</sub> are initially devised for wide input matching circuit using common-gate configuration. M<sub>3</sub> - M<sub>5</sub> construct a unit circuit described as balun 1 in Figs. 1 and 2. M<sub>6</sub> - M<sub>7</sub> and M<sub>8</sub> - M<sub>9</sub> pairs build the other unit circuits depicted in Figs. 1 and 2 as balun 2. The proposed active balun can be analyzed properly by cascoding these two unit circuits. Amplitude and phase imbalances at the balanced output always occur due to gain and phase mismatches of two unit circuits as

Fig. 1. Circuit of the proposed active balun.

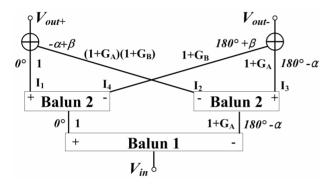

Fig. 2. Phase and amplitude imbalances of the proposed active balun.

## represented in Fig. 2.

The principle of phase correction to reduce phase imbalance is symbolized in Fig. 2 which is constituted with two unit circuits [5]. Two unit circuits provide unequal phase-vs-frequency response. The outputs of balun 1 result in phase difference of  $180^{\circ}$ - $\alpha$ , which means phase error of - $\alpha$ . Also the outputs of balun 2 yield phase difference of  $180^{\circ}$ + $\beta$  which means phase error of  $\beta$  where  $\alpha$  and  $\beta$  take positive numbers. The reason why negative phase error is used for balun 1 is because balun 1 should be designed for ensuring phase difference less than  $180^{\circ}$ . Phase difference greater than  $180^{\circ}$  corresponds to balun 2 as well. Phases of  $V_{out}$ + and  $V_{out}$ - without gain error can be expressed as in (1):

$$\angle V_{out} + = \frac{-\alpha + \beta}{2}$$

$$\angle V_{out} - = 180^{\circ} + \frac{-\alpha + \beta}{2}$$

(1)

Therefore the phase imbalance (i.e. phase error) between  $V_{out}^+$  and  $V_{out}^-$  becomes zero when gain

imbalance (i.e. gain error) is not considered.

To calculate the total phase imbalance between  $V_{out}^+$  and  $V_{out}^-$  considering gain imbalances as shown in Fig. 2, output signals of  $I_1$  -  $I_4$  are characterized with gain errors  $(G_A \text{ and } G_B)$  and phase errors  $(\alpha \text{ and } \beta)$  of unit circuits as described in (2) [5]:

$$I_{1} = \sin \omega t$$

$$I_{2} = (1 + G_{A})(1 + G_{B})\sin(\omega t - \alpha + \beta)$$

$$I_{3} = -(1 + G_{A})\sin(\omega t - \alpha)$$

$$I_{4} = -(1 + G_{B})\sin(\omega t + \beta)$$

(2)

Consequently the total phase error (PE) manifests itself in difference between phases of  $V_{out}^+$  and  $V_{out}^-$  which is calculated as vector summation of  $I_1$ ,  $I_2$  and  $I_3$ ,  $I_4$ , respectively, leading to (3) [5]:

$$PE = \left| \angle V_{out+} - \angle V_{out-} \right| - 180^{\circ}$$

$$= \tan^{-1} \left[ \frac{G_A - G_B}{2 + G_A + G_B} \cdot \tan \left( \frac{-\alpha - \beta}{2} \right) \right]$$

$$- \tan^{-1} \left[ \frac{G_A + G_B + G_A G_B}{2 + G_A + G_B + G_A G_B} \cdot \tan \left( \frac{-\alpha + \beta}{2} \right) \right]$$

(3)

where if G<sub>A</sub> and G<sub>B</sub> approach 0, phase error goes to 0.

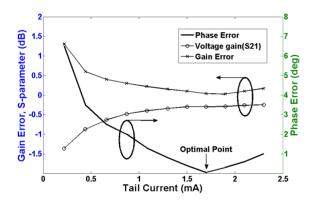

To correct phase imbalance in [5], FETs in balun 1 (M5 and M6 in [5]) must be designed in the same DC conditions and the voltage gains of M5 and M6 in [5] should be maintained to be exactly 0 dB, which is not easy. In order to overcome this limit, we propose the current-steering architecture for balun 1 which can be easily designed and provides the optimum point for gain and phase errors as shown in Fig. 4.

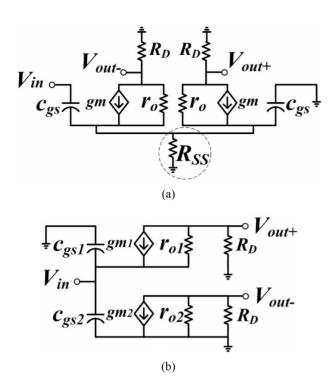

Equivalent circuit for balun 1 in Fig. 1 can be represented as shown in Fig. 3(a), where  $G_A$  is derived as in (4).  $G_A$  goes to 0 when tail current acts as an ideal current source (i.e.  $R_{SS} = \infty$ ). However,  $R_{SS}$  is finite due to short channel effect, thus gain error of balun 1 cannot be avoided. Maintaining voltage gain,  $R_{SS}$  should be obtained as large as possible for balun 1.

$$G_{A} = \left| \frac{R_{D} + r_{O}}{1 + g_{m} r_{O}} \left[ \frac{1 + \left( \frac{1}{R_{SS}} + j\omega C_{gs} + \frac{1 + g_{m} r_{O}}{R_{D} + r_{O}} \right) \frac{g_{m} r_{O}}{j\omega C_{gs}}}{r_{O} + R_{D} + \frac{g_{m} r_{O}}{j\omega C_{gs}}} \right] \right| - 1$$

$$(4)$$

**Fig. 3.** Equivalent circuit for the proposed circuit (a) balun 1, (b) balun 2.

Fig. 4. Simulated results with tail current analysis.

where for  $G_A = 0$ ,  $R_{SS}$  should be infinity. Similarly, equivalent circuit for balun 2 is drawn as shown in Fig. 3(b) where both transistors do not constitute DC symmetry unlike balun 1.  $G_B$  is expressed as in (5) where transconductance difference contributes to gain error.

$$G_B = \frac{g_{m1}(R_D \parallel r_{O1})}{g_{m2}(R_D \parallel r_{O2}) + \frac{R_D}{r_{O2} + R_D}} - 1 \cong \frac{g_{m1}}{g_{m2}} - 1 \quad (5)$$

Since two unit circuits need different design approaches, it is necessary to find out an optimal design

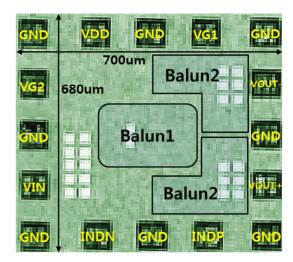

Fig. 5. Micro-photograph of the fabricated active balun.

where tail current plays a critical role in reducing  $G_A$  and  $G_B$ , and then  $P_E$  as deduced in (3)-(5). (3)-(5) are computed based on the parasitics of FET, these are valid as long as the operating frequency is lower than the unit gain frequency ( $f_T$ ) of FET. Steering the tail current, the proposed balun is simulated, providing phase error, gain error and voltage gain as illustrated in Fig. 4. It reveals that phase and gain errors can be optimized around tail current of 1.7 mA or 1.8 mA.

Since  $G_A$  in balun 1 is unavoidable, minimizing  $G_B$  of balun 2 with maintaining the voltage gain of balun 1 ensures reduction of phase error of the whole circuit. From overall analysis, the proposed circuit performs design optimization by adjusting the tail current. Furthermore, phase correction is performed using symmetry of balun 2 and configuration of balun 1 allows a design freedom. For a design procedure, the input matching stage ( $M_1$  and  $M_2$ ) is firstly designed, next balun 1 and balun 2 are individually devised, and finally tail current is adjusted together with optimizing balun 1 and balun 2. The whole biasing and transistor dimensions are shown right below in Fig. 1.

### III. MEASUREMENT RESULTS

The designed active balun is fabricated in 1P6M 0.18  $\mu$ m standard CMOS technology as shown in Fig. 5. The chip area including pads takes 700  $\mu$ m x 680  $\mu$ m excluding the input and output matching networks.

Parasitic capacitances and resistances are extracted and used for post-layout simulation. Die chip was bond-

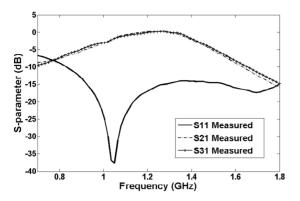

Fig. 6. Measured S-parameters.

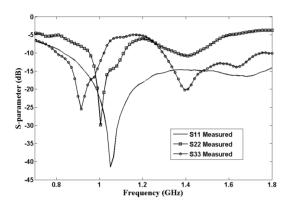

Fig. 7. Measured matching performances.

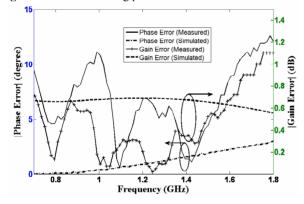

Fig. 8. Measured output phase and gain errors.

wired in a PC board to perform experiments. S-parameter measurements are shown in Figs. 6 and 7, where  $S_{21}$  and  $S_{31}$  show 0.3 dB maximum at 1.2 GHz. Bandwidth in terms of  $S_{21}$  and  $S_{31}$  is measured to be 0.5 GHz (0.95 - 1.45 GHz) where measured  $S_{11}$  is maintained under - 15 dB. Also, output reflection coefficients,  $S_{22}$  and  $S_{33}$ , are less than -6 dB as shown in Fig. 7. Fig. 8 shows phase and gain errors at the balanced output port of the designed balun, where simulation shows  $2^{\circ}$  and 0.7 dB

Table 1. Comparison of Active baluns

|           | BW<br>(GHz) | GE<br>(dB) | PE (°) | Gain<br>(dB) | P <sub>DC</sub> (mW) | Area<br>(mm²) |

|-----------|-------------|------------|--------|--------------|----------------------|---------------|

| [2]       | 2-40        | 0.5        | -      | -1~1         | 40                   | 0.56          |

| [3]       | DC-21       | 1.2        | 5      | 1.4~4.3      | 177                  | 0.562         |

| [5]       | 60.4-66.6   | 1.7        | 6.8    | 17.6*        | 19                   | 0.275         |

| [6]       | 0.2-5.2     | 0.7        | 2      | 13~15.6      | 21                   | -             |

| [10]      | 1-2         | 1          | 2      | 9.3          | 9                    | N/A           |

| [11]      | 0-8         | 2.7        | 4      | N/A          | 1.44                 | N/A           |

| This work | 0.95-1.45   | 0.5        | 11     | -3~0.3       | 7.2                  | 0.476         |

\* includes LNA

maximum, and measurement shows 11° and 0.5 dB maximum. Primary cause for deviation of phase error between simulation and measurement stems from parasitic series inductances of bonded wire used for connecting the die chip to a PC board which was not accurately included during simulation. Measured performances are compared with other previous works as summarized in Table 1 where the proposed active balun shows comparable results in terms of gain error, gain and power consumption in spite of a bit large phase error. Relatively low power consumption originates from low gain and optimized current steering for reducing gain and phase errors.

#### IV. CONCLUSION

An active balun using phase correction technique based on current steering is presented. The proposed architecture is devised efficiently to correct phase and gain errors compared with the conventional active baluns. Designed active balun shows bandwidth of 0.5 GHz where maximum phase error of 11° and maximum gain error of 0.5 dB in measurement as well as relatively low power consumption of 7.2 mW.

## REFERENCES

- [1] P. S. Wu, C.H. Tseng, M.F. Lei, T.W. Haung, and H. Wang, "Threedimensional X-band new transformer balun configuration using the multilayer ceramic technologies," *34th European Microwave Conf.*, pp. 385-388. 2004.

- [2] B. J. Huang, B. J. Huang, K. Y. Lin, and H. Wang, "A 2-40 GHz active balun using 0.13 μm CMOS process," *IEEE Microw. Wireless Compon. Lett.*,

- vol. 19, no. 3, pp. 164-166, Mar. 2009.

- [3] S. H. Weng, H. Y. Chang, and C. C. Chiong, "A DC-21 GHz low imbalance active balun using Darlington cell technique for high speed data communications," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 11, pp. 728-730, Nov. 2009.

- [4] B. Welch, K. T. Kornegay, H. M. Park, and J. Laskar, "A 20-GHz low-noise amplifier with active balun in a 0.25 μm SiGe BICMOS technology," *IEEE JSSC*, vol. 40, no. 10, pp. 141-144, Oct. 2005.

- [5] H. H. Chiang, F. C. Huang, C. S. Wang, and C. K. Wang, "A 90 nm CMOS V-band low-noise active balun with broadband phase-correction technique," *IEEE JSSC*, vol. 46, no. 11, pp. 2583-2591, Nov. 2011.

- [6] S. C. Blaakmeer, E. A. M. Klumperink, D. M. W. Leenaerts, and B. Nauta, "Wideband balun-LNA with simultaneous output balancing, noisecanceling and distortion-canceling," *IEEE JSSC*, vol. 43, no. 6, pp. 1341-1350, Jun. 2008.

- [7] D. Mastantuono and D. Manstretta, "A low-noise active balun with IM2 cancellation for multiband portable DVB-H receivers," *IEEE ISSCC*, pp. 216-217, 2009.

- [8] M. Y. Hsu, C. S.Wang, and C. K.Wang, "A low power high reliability dual-path noise-cancelling LNA for WSN applications," *IEEE CICC*, pp. 1-4, 2010.

- [9] C. S. Lee, M. G. Kim, J. J. Lee, K. E. Pyun, and H. M. Park, "A low noise amplifier for a multi-band and multi-mode handset," *IEEE RFIC Symp.*, pp. 47-50, 1998.

- [10] T. Hsu and C. Kuo, "Low power 8-GHz ultrawideband active balun," *Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems*, pp. 365-368, Jan. 2006.

- [11] D. H. Lee, J. Han, C. Park, and S. Hong, "A CMOS active balun using bond wire inductors and a gain boosting technique," *IEEE Microwave and Wireless Components Letters*, vol. 17, no. 9, pp. 676–678, Sep. 2007.

Front-end system.

Ji An Park received the B.S. degree in the Electronics, Telecommunication and Computer Engineering from Korea Aerospace University, Korea, in 2014, where he is currently studies for MS. His research interests include RFIC, Passive circuits, and

Ho Jeong Jin received the B.S. degree from the Department of Telecommunication Engineering, Korea Aerospace University, Goyang, Korea, in 2015. His research interests include CMOS Analog Circuit design and RF system.

Choon Sik Cho received his B.S. in Control and Instrumentation Engineering from Seoul National University in 1987, his M.S. in Electrical and Computer Engineering from the University of South Carolina in 1995, and his Ph.D. in Electrical and

Computer Engineering from the University of Colorado in 1998. From 1987 to 1993, he was with LG Electronics, working on communication systems. From 1999 to 2003, he was with Curitel, where he was principally involved with the development of mobile phones. He joined the School of Electronics and Information Engineering at Korea Aerospace University in 2004. His research interests include the design of RFIC/MMIC, millimeterwave ICs, analog circuits, imaging radars, bio sensors as well as wireless power transfer and energy harvesting.