# Process-Variation-Adaptive Charge Pump Circuit using NEM (Nano-Electro-Mechanical) Relays for Low Power Consumption and High Power Efficiency

Sangdon Byeon<sup>1</sup>, Sanghak Shin<sup>1</sup>, Jae-Sang Song<sup>1</sup>, Son Ngoc Truong<sup>1</sup>, Hyun-Sun Mo<sup>1</sup>, Seongsoo Lee<sup>2</sup>, and Kyeong-Sik Min<sup>1,\*</sup>

Abstract—For some low-frequency applications such as power-related circuits, NEM relays have been known to show better performance than MOSFETs. For example, in a step-down charge pump circuit, the NEM relays showed much smaller layout area and better energy efficiency than MOSFETs. However, severe process variations of NEM relays hinder them from being widely used in various low-frequency applications. To mitigate the process-variation problems of NEM relays, in this paper, a new NEMrelay charge pump circuit with the self-adjustment is proposed. By self-adjusting a pulse amplitude voltage according to process variations, the power consumption can be saved by 4.6%, compared to the conventional scheme without the self-adjustment. This power saving can also be helpful in improving the power efficiency of the proposed scheme. From the circuit simulation of NEM-relay charge pump circuit, the efficiency of the proposed scheme is improved better by 4.1% than the conventional.

*Index Terms*—Nano-electro-mechanical (NEM) relays, charge pump circuit, process-variation-adaptive, high power efficiency, low power consumption

#### I. INTRODUCTION

Nano-Electro-Mechanical (NEM) relays have an ideal sub-threshold behavior, where the 'off' leakage current is almost zero [2]. NEM relays are composed of 4 terminals like MOSFET devices. However, in NEM relays, the mechanical channel is actuated by electrostatic force, instead of the electrical channel [2-6]. When the channel is turned off in NEM relays, it is disconnected mechanically from the both source and drain. By doing so, the 'off' leakage current can be ideally zero that is a very big advantage of NEM relays over MOSFET devices suffering a large amount of 'off' leakage. The demerit of NEM relays is that its electrostatic actuation of mechanical channel causes much longer switching time than the electrical channel's fast switching time [3, 6]. Considering both the advantage and disadvantage of NEM relays, the NEM-relay circuits can be considered very suitable to applications that are energy-efficient and slow, such as power-related circuits [7, 8].

As one of low-frequency applications that can show better energy efficiency of NEM-relay circuits, a stepdown charge pump circuit was designed and analyzed [7]. Here, the NEM relays and MOSFETs were compared in terms of layout area, power consumption, and power efficiency, etc. [7]. From the analysis, it can obviously be comprehended that the step-down charge pump with NEM relays has smaller layout area by more than one order of magnitude and higher power efficiency by more than 10%, than the MOSFET-based version [7].

In spite of smaller area and higher efficiency of the

Manuscript received Apr. 29, 2015; accepted Jun. 11, 2015 The part of this work [12] was presented in Korean Conference on Semiconductors, Inchon, Korea, Feb. 2015.

<sup>&</sup>lt;sup>1</sup> School of Electrical Engineering, Kookmin University, Seoul, Korea.

<sup>2</sup> School of Electronic Engineering, Soongsil University, Seoul, Korea E-mail : mks@kookmin.ac.kr

NEM-relay circuits, process variations of mechanical channel can be a serious problem in spreading NEM-relay circuits to wider applications. Even a small amount of variations in mechanical channel's dimensions can result in significantly large distribution of electrical parameters of NEM relays [2, 10]. For example, a 10% variation in the air gap of mechanical channel can make the largest pull-in voltage 3.6 times larger than the smallest pull-in voltage. The large amount of variations in electrical parameters, such as pull-in voltage, introduces a big burden to the circuit design, because it is important to satisfy all the possible cases including the worst case.

To avoid the burden of circuit design that is introduced by process variations, a new NEM-relay circuit with the self-adjustment function according to process variations is proposed, in this paper [12]. By doing so, the unnecessary power consumption can be minimized and the power efficiency can be much improved than the conventional scheme without the self-adjustment.

### II. VERILOG-A MODEL AND PROCESS VARIATIONS OF NEM RELAYS

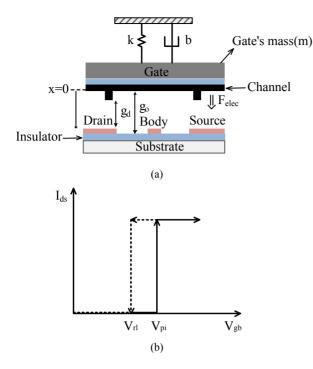

Fig. 1(a) shows the cross section of NEM relays that is composed of parallel-plate capacitor [2]. The capacitor has the movable gate electrode and the body, source, and drain electrodes that are fixed. The gate is mechanically controlled by a spring-like force and a damper-like force. The dynamic motion of the gate is calculated with the following equation [2].

$$F_{elec}(x) = mx'' + bx' + kx$$

(1)

Here x is the displacement of the movable gate electrode. m is the gate's mass and b is the damping factor. k is the spring coefficient.  $F_{elec}$  is an electrostatic force which is caused by a voltage applied between the gate and body electrodes.  $g_0$  is the actuator's gap between the gate and substrate.  $g_d$  is the dimple gap thickness.

The electrostatic force can be calculated with [1],

$$F_{elec}(\mathbf{x}) = \frac{\varepsilon_0 \times A_{ov} \times V_{gb}^2}{2 \times (\mathbf{g}_0 - \mathbf{x})^2}$$

(2)

Here  $A_{ov}$  is the overlap area between the gate and body electrodes,  $\varepsilon_0$  is the permittivity of free space, and  $V_{gb}$  is the voltage difference between the gate and body electrodes.

When a voltage applied between the gate and body electrodes is enough large to pull the gate to the body, the relay is turned on. The voltage needed to turn on the NEM relays is called the pull-in voltage,  $V_{pi}$ . It is expressed with [1]

$$V_{\rm pi} = \sqrt{\frac{8 \times k \times g_0^3}{27 \times \varepsilon_0 \times A_{ov}}} \tag{3}$$

To turn off the NEM relay, a voltage called the release voltage,  $V_{rl}$ , should be applied to detach the gate from the body. The release voltage is expressed by [1]:

$$V_{\rm rl} = \sqrt{\frac{2 \times (k \times g_d - F_A) \times (g_o - g_d)^2}{\varepsilon_0 \times A_{ov}}}$$

(4)

Here,  $F_A$  is the surface adhesion force. When  $V_{rl}$  is applied to the NEM relays, the conducting path between the drain and source is physically detached. Thereby, the current can't flow through the channel after detaching it.

Comparing  $V_{pi}$  and  $V_{rl}$  in Fig. 1(b) shows that  $V_{rl}$  is smaller than  $V_{pi}$ . This is because detaching the gate electrode from the body should overcome not only the electrostatic force, but also the surface adhesive force. This voltage difference between  $V_{pi}$  and  $V_{rl}$  causes hysteretic switching characteristic in Fig. 1(b).

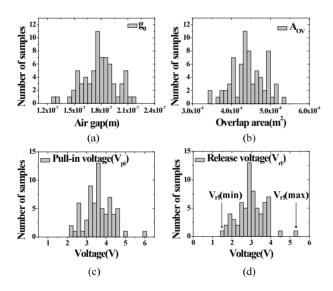

One important problem in NEM relays is the severe process variations. Especially, the geometrical dimensions such as g<sub>0</sub> and A<sub>ov</sub> are suffering large amount of variations that can affect the pull-in voltage and release voltage very much, illustrated by the simulation results shown in Fig. 2(a)-(d). Fig. 2(a) shows the statistical variation of  $g_{0}$ , where the average is  $1.8 \times 10^{-7}$  m and the standard deviation is given 10%. Similarly, Fig. 2(b) shows  $A_{ov}$ 's distribution with the average value of  $4.5 \times 10^{-4}$  m<sup>2</sup> and 10% variation. The variations of g<sub>0</sub> and  $A_{ov}$  can affect the both pull-in voltage and release voltage, as shown in Fig. 2(c) and (d), respectively. Here, the average values of  $V_{pi}$  and  $V_{rl}$  are 3.5 V and 2.9 V, respectively. V<sub>rl(min)</sub> is the smallest value among all the V<sub>rl</sub> values in Fig. 2(d). Similarly, V<sub>rl(max)</sub> is the largest

**Fig. 1.** (a) The cross section of NEM relays is composed of parallel-plate capacitor with the mass-spring-damper system [2], (b) The hysteretic swithcing characteristic of NEM relays shows different pull-in voltage and release voltage [7]

**Fig. 2.** (a) The statistical variation of  $g_0$  where the average value is  $1.8 \times 10^{-7}$  m and the standard deviation is given 10%, (b) The statistical variation of  $A_{ov}$ , where the average value is  $4.5 \times 10^{-4}$  m<sup>2</sup> and 10% variation is given, (c) The statistical variation of  $V_{pi}$  that are caused by the variations of  $g_0$  and  $A_{ov}$  in Fig. 2(a) and (b), respectively, (d) The statistical variation of  $V_{rl}$  that are caused by the variations of  $g_0$  and  $A_{ov}$  in Fig. 2(a) and (b), respectively.

value in the variation in Fig. 2(d). In Fig. 2(d),  $V_{rl(min)}$  and  $V_{rl(max)}$  are 1.55 V and 5.45 V, respectively.

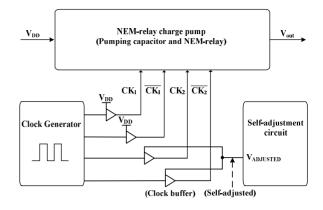

**Fig. 3.** The block diagram of the proposed NEM-relay charge pump circuit with the self-adjustment. The adjusting circuit can adjust the pulse amplitude of  $CK_2$  and  $/CK_2$  to minimize switching power consumption in controlling the relays

## III. THE PROPOSED NEM-RELAY CIRCUIT with The Self-adjustment according to Process Variations

As mentioned in the introduction part, the NEM-relay charge pump circuit can have smaller layout area and better power efficiency due to the advantage of mechanical channel of NEM relays over the electrical channel of the conventional MOSFETs. However, large process variations of NEM relays can hinder the NEMrelay circuits from being widely used in practical applications. To mitigate these process-variation-related problems of NEM relays, a simple self-adjustment circuit that can adjust the pulse amplitude voltage according to process variations is proposed in this paper.

Fig. 3 shows a block diagram of the NEM-relay charge pump circuit with the self-adjustment which can adjust the pulse amplitude of clock signals according to process variations. In Fig. 3, the switching power consumption of NEM-relay charge pump circuit can be minimized by the self-adjustment at a given process-variation condition.  $V_{DD}$  is the input supply voltage.  $V_{OUT}$  is the output voltage of NEM-relay pump circuit. CK<sub>1</sub> and /CK<sub>1</sub> are generated from the clock generator to drive the pumping capacitors. CK<sub>2</sub> and /CK<sub>2</sub> are to control the relays. In Fig. 3, the adjusting circuit can change the pulse amplitude of CK<sub>2</sub> and /CK<sub>2</sub> according to process variations to minimize the switching power loss in controlling the relays.

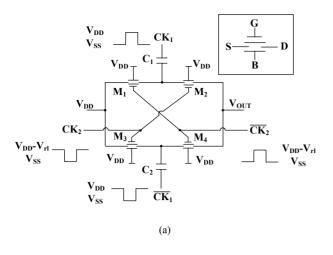

Fig. 4(a) shows the NEM-relay charge pump circuit.  $M_1$ ,  $M_2$ ,  $M_3$ , and  $M_4$  are NEM relays.  $C_1$  and  $C_2$  are

Fixed pulse amplitude

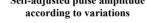

**Fig. 4.** (a) The NEM-relay charge pump circuit, (b) The conventional scheme, where the pulse amplitude of  $CK_2$  and  $/CK_2$  is fixed by  $V_{DD}$ - $V_{rl(min)}$  of the worst-case of  $V_{rl}$  variation, (c) The proposed self-adjustment scheme, where the pulse amplitude of  $CK_2$  and  $/CK_2$  is self-adjusted according to the process variation of  $V_{rl}$

pumping capacitors.  $CK_1$  and  $/CK_1$  are the true and inverted versions of clock signal for driving pumping capacitors.  $CK_2$  and  $/CK_2$  are the true and inverted versions of clock signal for controlling the NEM relays. The NEM-relay charge pump circuit can deliver the output voltage,  $V_{OUT}$ , as high as  $2V_{DD}$ . The NEM relay has 4 terminals which are the gate, source, drain, and body, as shown in the inset of Fig. 4(a). Here, the body electrode of NEM relay is applied by  $V_{DD}$ . If the gate electrode is applied by 0V, the NEM relay is turned on with  $|V_{gb}|=V_{DD}$ . If the gate electrode has a voltage of  $V_{DD}$ - $V_{rl}$ , the relay is turned off with  $|V_{gb}| \le V_{rl}$ . To explain the concept of self-adjustment of pulse amplitude of clock signals, let us go back to Fig. 2(c) and (d), where the pull-in and release voltages seem to suffer severe process variations. To turn off NEM relay,  $V_{gb}$ should be as small as  $V_{rl}$ . Considering the  $V_{rl}$  variation in Fig. 2(d),  $V_{gb}$  should be as small as  $V_{rl(min)}$ . In this worstcase scenario, the pulse amplitude of CK<sub>2</sub> and /CK<sub>2</sub> should be fixed by  $V_{DD}$ - $V_{rl(min)}$ , as shown in Fig. 4(b). This fixed amount of pulse amplitude as high as  $V_{DD}$ - $V_{rl(min)}$  can be a waste for the rest of  $V_{rl}$  values that are larger than  $V_{rl(min)}$ . Considering the case of  $V_{rl(max)}$ , the pulse amplitude can be as low as  $V_{DD}$ - $V_{rl(max)}$  to turn off NEM relays and, thereby more switching power can be saved.

The self-adjustment circuit can adjust the pulse amplitude of  $CK_2$  and  $/CK_2$  according to the  $V_{rl}$  variation, as shown in Fig. 4(c). For  $V_{rl(max)}$  in Fig. 2(d), the pulse amplitude can be lowered to  $V_{DD}$ - $V_{rl(max)}$ . For  $V_{rl(min)}$  in Fig. 2(d), the amplitude is decided as high as  $V_{DD}$ - $V_{rl(min)}$ . By adjusting the pulse amplitude according to the  $V_{rl}$  variation, the switching power consumption in the  $V_{rl}$  variation can be minimized.

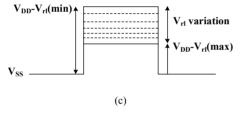

Fig. 5(a) is the self-adjustment circuit for adjusting the pulse amplitude of  $CK_2$  and  $/CK_2$ . M and  $M_2$  are NEM relays. I<sub>1</sub> is the constant current source.  $C_X$  is the charging capacitor. UG<sub>1</sub> is the unit gain buffer. The waveforms of important signals are shown in Fig. 5(b). At the initial time,  $V_X$  is discharged to 0V.  $V_Y$  is also 0V because  $M_1$  is turned on at the initial moment. At this time,  $M_2$  is turned on by  $V_Y=0V$ . As I<sub>1</sub> is accumulated on  $C_X$ ,  $V_X$  is increased higher. When  $V_X$  becomes high enough to release the gate from the body in  $M_1$ ,  $M_1$  becomes 'off'. At this time,  $V_Y$  becomes high to turn off  $M_2$ . By turning off  $M_2$ , the  $V_X$  voltage as high as  $V_{DD}-V_{rl}$ , at the releasing moment can be retained on  $C_X$  for long time. This  $V_{DD}-V_{rl}$  is delivered to the NEM-relay charge pump circuit by the unit gain buffer, UG<sub>1</sub>.

#### **IV. SIMULATION RESULTS**

The conventional and proposed schemes were compared in terms of power consumption and power efficiency as shown, in Fig. 6(a) and (b). The simulation was implemented through Cadence Spectre [13]. The NEM relays were modeled using Verilog-A and DONGBU HITEK 0.18-µm CMOS parameters were

**Fig. 5.** (a) The self-adjustment circuit for adjusting the pulse amplitude of  $CK_2$  and  $/CK_2$  according to the  $V_{rl}$  variation to minimize the switching power consumption, (b) The waveforms of  $V_X$ ,  $V_Y$ , and  $V_{ADJUSRED}$

used in the simulation. For the power consumption, the conventional scheme without the self-adjustment circuit consumes 571  $\mu$ W in Fig. 6(a). The proposed scheme with the self-adjustment circuit can reduce the power consumption from 571  $\mu$ W to 545  $\mu$ W in average in Fig. 6(a). The percentage power saving is improved by as much as 4.6% in the proposed scheme due to self-adjusting the pulse amplitude according to V<sub>rl</sub> variation. The power efficiency is compared in Fig. 6(b). The power efficiency of the conventional scheme is as low as 82.8%. Due to the self-adjustment, the efficiency of the proposed scheme can be improved by 86.9%.

The power overhead that is consumed by this selfadjust circuit in Fig. 5(a) is as small as 1.65% in the power consumption of NEM-relay charge pump circuit.

Fig. 6. (a) Power consumption of the conventional scheme without the self-adjustment and the proposed scheme with the self-adjustment, (b) Power efficiency of the conventional scheme without the self-adjustment and the proposed scheme with the self-adjustment

The area penalty of the self-adjustment circuit can be neglected, because most of layout area of the charge pump circuit is occupied by the pumping capacitors and pumping switches in Fig. 4(a). Comparing to the charge pump circuit with these large-area pumping capacitors and pumping switches, the self-adjustment circuit can be designed with the smaller-size devices and capacitors. In this paper, the pumping capacitors of  $C_1$  and  $C_2$  in Fig. 4(a) are assumed as large as 60pF, while  $C_X$  in Fig. 5(a) is as small as 1pF. It means that the area of the selfadjustment circuit can be as small as 1/60 of the charge pump circuit.

#### V. CONCLUSIONS

For some low-frequency applications such as powerrelated circuits, NEM relays have been known to show better performance than MOSFETs [7, 8]. For example, in step-down charge pump circuit, the NEM relays showed much smaller layout area and better energy efficiency than MOSFETs [7, 8]. However, severe process variations of NEM relays hinder them from being widely used in various low-frequency applications.

To mitigate the process-variation problems of NEM relays, the new NEM-relay charge pump circuit with the self-adjustment was proposed in this paper. By adjusting the pulse amplitude according to process variations, it was possible to save the power consumption by 4.6%, compared to the conventional scheme without the self-adjustment. This power saving could also be helpful in improving the power efficiency of the proposed scheme. From the circuit simulation of NEM-relay charge pump circuit, the efficiency of the proposed scheme was improved better by 4.1% than the conventional.

#### **ACKNOWLEDGMENTS**

The work was financially supported by NRF-2013K1A3A1A25038533, NRF-2013R1A1A2A10064812, the Ministry of Knowledge Economy(100039239), and BK Plus with the Educational Research Team for Creative Engineers on Material-Device-Circuit Co-Design (Grant No: 22A20130000042), funded by the National Research Foundation of Korea (NRF), and by Global Scholarship Program for Foreign Graduate Students at Kookmin Univ. The CAD tools were supported by IC Design Education Center (IDEC), Daejeon, Korea.

#### REFERENCES

- P. M. Zavaracky, S. Majumder, and N. E. McGruer, "Micromechanical switches fabricated using nickel surface micromachining," *J. Microelectromech. Syst.*, vol. 6, no. 1, pp. 3-9, Mar. 1997.

- [2] F. Chen, H. Kam, D. Markovi'c, T. K. Liu, V. Stojanovi'c, and E. Alon, "Integrated circuit design with NEM relays," *IEE/ACM International Conference on Computer-Aided Design*, vol. 46, pp. 750-757, Nov. 2008.

- K. Akarvardar, D. Elata, R. Parasa, G. C. Wan, K. Yoo, J. Provine, P. Peumans, R. T. Howe, and H.-S. P. Wong, "Design considerations for complementary nanoelectromechanical logic gates," *IEEE Inter-*

national Electron Devices Meeting(IEDM), pp. 299-302, Dec. 2007.

- [4] J. Jeon, R. Nathanael, V. Pott, and T. K. Liu, "Four-Terminal relay design for improved body effect," *IEEE Electron Device Letters*, vol. 31, no. 5, pp. 515-517, May 2010.

- [5] R. Nathanael, V. Pott, H. Kam, J. Jeon, and T. K. Liu, "4-Terminal relay technology for complementary logic," *IEEE International Electron Devices Meeting(IEDM)*, pp. 1-4, Dec. 2009.

- [6] M. Spencer, et al, "Demonstrationm of integrated Micro-Electro-Mechanical relay circuits for VLSI applications," *IEEE Journal of Solid State Circuits*, vol. 46, no. 1, pp. 308-320, Jan. 2011.

- [7] R. Venkatasubramanian, S. Manohar, and P. Balsara, "Ultra low power high efficiency charge pump design using NEM relays," *IEEE 54th International Midwest Symposium on Circuits and Systems(MWSCAS)*, pp. 1-4, Aug. 2011.

- [8] S. Manohar, R. Venkatasubramanian, and P. Balsara, "Hybrid NEMS-CMOS DC-DC converter for improved area and power efficiency," 25th International Conference on VLSI Design, pp. 221-226, Jan. 2012.

- [9] H. Fariborzi, F. Chen, R. Nathanael, I. Chen, L. Hutin, R. Lee, T. K. Liu, and V. Stojanovic, "Relays do not leak – CMOS does," ACM/EDAC/ IEEE Design Automation Conference(DAC), pp. 1-4, May 2013.

- [10] H. Dadgour, A. Cassell, and K. Banerjee, "Scaling and variability analysis of CNT-Based NEMS devices and circuits with implications for process design," *IEEE International Electron Devices Meeting(IEDM)*, pp. 1-4, Dec. 2008.

- [11] H. Kam, V. Pott, R. Nathanael, J. Jeon, E. Alon, and T. K. Liu, "Design and reliability of a Micro-Relay technology for Zero-Standby-Power digital logic application," *IEEE International Electron Devices Meeting(IEDM)*, pp. 1-4, Dec. 2009.

- [12] S. Byeon, S. Shin, J. Song, S. N. Truong, H. Mo, and K. Min, "Process-variation-adaptive and energy-efficiency NEM-relay charge pump circuit," *Korean Conference on Semiconductors, Inchon in Korea*, Feb. 2015.

- [13] Virtuoso Spectre Circuit Simulator User Guide, CADENCE, San Jose, CA, USA, 2004.

**Sangdon Byeon** received the B.S. and M.S. degrees in Electronic Engineering from Kookmin University, Seoul, Korea, in 2012 and 2014, respectively. His research interests include circuit design, power-management ICs, and the next-generation memories.

Sanghak Shin received the B.S. degrees in Electronic Engineering from Kookmin University, Seoul, Korea, in 2013. He is currently working toward the M.S. degree at Kookmin University, Seoul, Korea. His research interests include circuit design, memristor, and memristor-

based crossbar for neuromorphic computing systems.

Jae-Sang Song received the B.S. degrees in Electronic Engineering from Kookmin University, Seoul, Korea, in 2014. He is currently working toward the M.S. degree at Kookmin University, Seoul, Korea. His research interests include circuit design, memristor, and memristor-

based crossbar for neuromorphic computing systems.

**Son Ngoc Truong** received the B.S. and M.S. degrees in Electronic Engineering from The University of Technical Education Ho Chi Minh City, Vietnam, in 2006 and 2011, respectively. He is currently working toward the Ph.D degree at Kookmin University, Seoul, Korea. His research

interests include circuit design, memristor, and memristorbased crossbar for neuromorphic computing systems.

**Hyun-Sun Mo** received the B.S., M.S., and Ph.D degrees in Electronic Engineering from Kookmin University, Seoul, Korea, in 1993 and 2011, and 2014, respectively. In 1993, she joined Samsung Electronics Semiconductor Division of the development of the low power and high-speed

SRAM and Flash memory circuits. Her research interests include the design of analog circuits, power-management ICs, and the next-generation memories.

Seongsoo Lee received B.S, M.S, and Ph.D degrees in E.E. from Seoul National University, Korea in 1991, 1993, and 1998, respectively. In 1998-2000, he was a research associate in Institute of Industrial Science, University of Tokyo, Japan. In 2000-2002, he was a research

professor in Department of Electronic Engineering, Ewha Womans University, Korea. He joined School of Electronic Engineering at Soongsil University, Korea in 2002, where he is currently an associate professor. His research interests include low-power SoC, multimedia SoC, and battery management SoC.

**Kyeong-Sik Min** received the B.S. degree in Electronics and Computer Engineering from Korea University, Seoul, Korea, in 1991, and the M.S.E.E. and Ph. D. degrees in Electrical Engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejeon,

Korea, in 1993 and 1997, respectively. In 1997, he joined Hynix Semiconductor Inc., where he was engaged in the development of low-power and high-speed DRAM circuits. From 2001 to 2002, he was a research associate at University of Tokyo, Tokyo, Japan, where he designed low-leakage memories and low-leakage logic circuits. In September 2002, he joined the faculty of Kookmin University, Seoul, Korea, where he is currently a Professor in the School of Electrical Engineering. He was a visiting professor at University of California, Merced, from Aug. 2008 to July 2009. Prof. Min served on various technical program committees such as Asian Solid-State Circuits Conference (A-SSCC), International Design Conference (ISOCC), and Korean SoC Conference on Semiconductors (KCS). He and his students received IDEC CAD & Design Methodology Award (2011), IDEC Chip Design Contest Award (2011), and IDEC Chip Design Contest Award (2012). He is a member of Institute of Electrical and Electronics Engineers (IEEE), Institute of Electronics Engineers of Korea (IEEK), and Institute of Electronics, Information, and Communication Engineers (IEICE) in Japan. His research interests include low-power VLSI, memory design, and power IC design.