http://dx.doi.org/10.6113/TKPE.2016.21.1.58

# 임의 파형 발생기를 위한 단일 루프 전압 제어기 설계

김현식<sup>1</sup>, 지승준<sup>1</sup>, 설승기<sup>†</sup>

Design of the Single-loop Voltage Controller for Arbitrary Waveform Generator

Hyeon-Sik Kim<sup>1</sup>, Seung-Jun Chee<sup>1</sup>, and Seung-Ki Sul<sup>†</sup>

#### Abstract

This study presents a design method for a single-loop voltage controller that is suitable for an arbitrary waveform generator (AWG). The voltage control algorithm of AWG should ensure high dynamic performance and should attain sufficient robustness to disturbances such as inverter nonlinearity, sensor noise, and load current. By analyzing the power circuit of AWG, control limitation and control target are presented to improve the dynamic performance of AWG. The proposed voltage control algorithm is composed of a single-loop output voltage control, an inverter current feedback term to improve transient response, and a load current feedforward term to prevent voltage distortion. The guideline for setting control gain is presented based on output filter parameters and digital time delay. The performance of the proposed algorithm is proven by experimental results through comparison with the conventional algorithm.

**Key words:** AWG(Arbitrary Waveform Generator), Programmable power supply, Output voltage control, Single-loop PI voltage control

#### 1. 서 론

최근 전력전자 분야의 연구가 진행됨에 있어 원하는 전압 상황을 임의로 모의할 수 있는 임의 파형 발생기 (AWG, Arbitrary Waveform Generator)의 필요성이 증대되고 있다. 이러한 임의 파형 발생기는 개발 제품과 연결되어 여러 가지 전압 및 주파수 조건에서 개발 제품의 동작을 검증할 수 있는 전원 환경을 제공해주는 역할을 한다. 예를 들어, 교류 전동기 가변속 구동 시스템은 성능 평가를 위해 다양한 주파수 및 전압에서 동작 검증이 필요하다. 또한 몇몇 전기 장치의 경우 전력품질(power quality) 평가를 위해 계통의 다양한 상황에 대한 모의 실험이 필요하다. 이에 따라, 정전압 정주파수(CVCF, Constant Voltage Constant Frequency) 동작뿐만 아니라 주파수 변동(frequency variations), 순간 전압 강하(voltage sag), 순간 전압 상승(voltage swell),

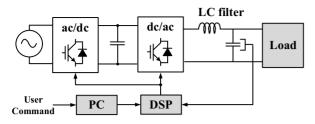

순시 정전(black out)과 같은 다양한 전압 상황을 모의할 수 있는 임의 파형 발생기는 개발 제품의 신뢰성 확보를 위해 성능 보증 시험에 필수적이라 할 수 있다<sup>[1-2]</sup>. 이러한 임의 파형 발생기는 일반적으로 그림 1과 같

이 구성된다. 이는 계통 측 ac-dc 컨버터, 부하 측 dc-ac 인버터와 LC 필터, DSP 기반의 제어기, 그리고 PC 기반의 사용자 인터페이스 시스템(user interface system)으로 구성된다. 이러한 구조에서 원하는 파형 합성은 부하 측 dc-ac 인버터와 LC 필터를 통해 이루어지게 된다. 실제 인버터 출력 전압은 PWM 파형 형태가되는데 LC 필터를 통해 PWM 스위칭 주파수 대역의고조파 성분을 감쇠하도록 한다. 이를 통해 원하는 전압파형이 LC 필터의 필터 캐패시터와 병렬로 연결된 부하로 전달되게 된다.

임의 파형 발생기는 고품질(high performance)의 출력 전압 특성을 가져야 한다. 이를 위해서 부하 변동에 강 인하고 빠르게 전압 지령을 추종할 수 있는 전압 제어 기를 필요로 한다. 특히 큰 용량의 출력을 필요로 하는 임의 파형 발생기의 경우, 스위칭 소자의 제약으로 인해 스위칭 주파수를 높이 올릴 수 없는 제한 조건이 존재 한다. 이러한 한계 내에서 제어 대역폭(bandwidth)을 최 대한 증대시킬 수 있는 전압 제어기는 고품질의 전압 합성을 위해 필수적이다. 또한 전압 제어기는 사용 환경 에 따라서 발생할 수 있는 각종 외란(disturbances)에

Paper number: TKPE-2016-21-1-8

Print ISSN: 1229–2214 Online ISSN: 2288–6281

<sup>†</sup> Corresponding author: sulsk@plaza.snu.ac.kr, Dept. of Electrical and Computer Eng., Seoul National University

Tel: +82-2-880-7251 Fax: +82-2-878-1452

<sup>&</sup>lt;sup>1</sup> Dept. of Electrical and Computer Eng., Seoul National Univ. Manuscript received Sep. 22, 2015; revised Oct. 25, 2015; accepted Dec. 30, 2015

<sup>-</sup> 본 논문은 2015년 전력전자학술대회 우수추천논문임

Fig. 1. Block diagram of an ordinary AWG.

강인한 제어기 형태를 갖추어야 한다.

따라서 본 논문에서는 3상 임의 파형 발생기 용도에 적합한 전압 제어기 설계 방법을 제안하고자 한다. 특히 3상 4선식 인버터 및 LC 필터로 구성된 시스템을 기반으로, 제어 대역폭을 최대화하기 위한 단일 루프 전압 제어기를 제안한다. 또한 과도 특성 개선 및 부하 전류 외란으로 인한 전압 왜곡 방지를 위해 전류 정보를 추가하여 전향 보상에 사용하도록 한다. 그리고 출력 파형의 동특성과 외란 제거 성능을 향상시키기 위한 최적제어 이득 선정 방법을 제시한다. 최종적으로 실험 세트를 통해 제안한 방식의 제어기 성능을 검증한다.

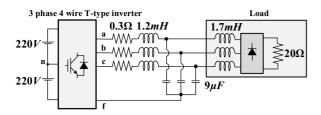

## 2. 전력 회로 구성

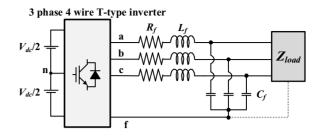

부하 측 시스템은 그림 2와 같이 3레벨(level) 4레그 (leg) T-type 인버터와 LC 필터로 구성된다. T-type 인버터는 2레벨 인버터에 비해 작은 필터의 적용 가능성 및 높은 운전 효율 특성으로 인해 주목받고 있다<sup>[3]</sup>. 2레벨 인버터로 구성된 임의 파형 발생기의 경우, 출력 전압에 존재하는 스위칭 주파수 대역의 고조파 성분의 충분한 감쇠를 위해 스위칭 주파수를 높이거나 LC 필터의 크기를 증대시켜야 한다. 하지만 T-type 인버터를 사용하게 되면, 2레벨 인버터에 비해 상대적으로 높은 효율및 작은 LC 필터로 인하여 작고 가벼운 전력회로를 설계할 수 있다.

임의 파형 발생기의 경우 부하의 형태와 무관하게 각상의 개별 전압 지령을 잘 추종할 수 있어야 한다. 하지만 주로 사용되는 3레그 토폴로지의 경우 부하 조건에따라 단상 부하들에 인가되는 전압이 달라질 수 있다. 이러한 각 상의 전압을 독립적으로 합성하지 못하는 문제를 해결하기 위해, 4레그 토폴로지가 제안되었다. 4레그 토폴로지는 반도체의 가격 감소 및 성능 증대로 인해 비용, 효율, 크기 측면에서 3레그 하프 브리지(half bridge) 또는 출력에  $\Delta$ -Y(Delta-Wye) 변압기를 사용하는 시스템에 비해 장점을 지니게 된다<sup>[4]</sup>. 여기서 추가적인 레그는 필터 캐패시터 하단 및 단상 부하들의 중성점과 연결되게 된다.

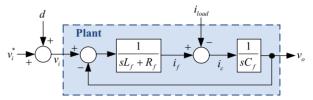

제안된 시스템에서 각 상의 전력 회로는 그림 3과 같이 모델링될 수 있다. 이 때,  $L_f$ 는 필터 인덕터,  $C_f$ 는 필터 캐패시터이며  $R_f$ 는 인버터와 필터 인덕터에 존재

Fig. 2. System configuration of the proposed AWG.

Fig. 3. Block diagram for the power stage of AWG.

하는 등가 직렬 저항을 의미한다. 입력 전압 지령은  $v_i^*$ , 인버터 비선형성(nonlinearity) 및 센서 측정 오차를 비롯한 입력 외란은 d, 부하 전류 외란은  $i_{load}$ 로 표시하면, 이러한 변수들이 출력 전압,  $v_o$ ,에 미치는 영향은 식 (1)의 전달함수를 통해 확인할 수 있다.

$$\begin{split} v_o(s) &= G_{vi}(s) v_i(s) + G_{vd}(s) d(s) + G_{iL}(s) i_{load}(s) \\ G_{vi}(s) &= \frac{1}{L_f C_f s^2 + R_f C_f s + 1}, \\ \\ &\stackrel{\text{T.}}{\text{T.}}, \ G_{vd}(s) &= \frac{1}{L_f C_f s^2 + R_f C_f s + 1}, \\ G_{iL}(s) &= -\frac{L_f s + R_f}{L_f C_f s^2 + R_f C_f s + 1}. \end{split}$$

입력 전압 지령에 따른 출력 전압 전달함수  $G_{vi}(s)$ 는 식 (2)와 같이 정리할 수 있다.

$$G_{vi}(s) = \frac{\omega_f^2}{s^2 + 2\zeta_f \omega_f s + \omega_f^2}$$

$$\text{Et}, \ \omega_f = \frac{1}{\sqrt{L_f C_f}}, \ \zeta_f = \frac{R_f}{2} \sqrt{\frac{C_f}{L_f}}.$$

$$(2)$$

### 3. 제어기 설계

# 3.1 제어기 설계 시 목표 조건

임의 파형 발생기의 동특성을 개선하고 입력 외란 및 부하 전류에 의한 외란을 제거하기 위하여 적절한 제어 기 설계가 필요하다. 임의 파형 발생기를 위한 이상적인 제어 목표는 식 (3), (4)와 같다.

$$\frac{v_o(s)}{v_o^*(s)} = 1. \tag{3}$$

$$\frac{v_o(s)}{d(s)} = \frac{v_o(s)}{i_{load}(s)} = 0. (4)$$

식 (3)에 따르면, 전 주파수 대역의 전압 지령을 모두 추종하는 것이 이상적이라고 볼 수 있다. 하지만, 실제 출력 전압은 LC 필터로 인하여 식 (2)와 같이 2차 저역 필터(low pass filter) 형태를 가지게 된다. 따라서 물리적으로 필터의 공진 주파수보다 높은 대역,  $\omega>\omega_f$  에서인버터 출력을 정확히 합성하기 위해서는 지령 전압보다 훨씬 큰 입력 전압을 합성해주어야 한다<sup>[5]</sup>. 따라서, 보다 현실적인 제어 목표로서 식 (5)와 같은 2차 응답형의 제어 목표를 설정할 수 있다.

직류단 전압의 물리적인 제약으로 인하여 비감쇠 자연 주파수(undamped natural frequency)  $\omega_c$ 는 필터 공진 주파수  $\omega_f$  이하로 선정하여야 한다. 이 때, 최대한의 동특성을 갖기 위해서는  $\omega_c$ 를  $\omega_f$ 와 동일하게 설정하는 것이 유리하다. 또한 LC 필터의 공진으로 인한 오버슈트 (overshoot)를 억제하기 위해서 감쇠계수  $\zeta_c$ 는 임계 감쇠(critically damped) 값인  $1/\sqrt{2}$  이상으로 설정하여야 한다. 단, 감쇠계수가 클 경우 높은 주파수 대역에서 출력 전압의 위상 지연(phase delay)이 증대되는 문제가발생하므로 감쇠계수는  $1/\sqrt{2}$  에서 1 사이로 설정하는 것이 적합하다.

### 3.2 전압 제어기 구성

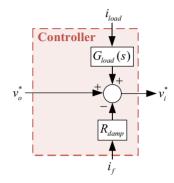

기존 여러 논문에서 그림 4와 같이 다양한 방법의 전압 제어기가 제시된 바 있다. 그림 4.(a)에 제시된 전압제어기는 하위 제어기로 전류 제어기를 사용하는 다중루프(multi-loop) 제어기<sup>[6]</sup>로서 전압 제어기의 제어 대역폭이 하위 전류 제어기의 제어 대역폭에 따라 제한되어동특성이 감소하는 문제가 발생한다. 이를 막기 위해 반복 처리 기법(iteration process)<sup>[7]</sup>, 극점-영점 상쇄 기법(pole-zero cancellation)<sup>[8]</sup>과 같은 다양한 제어기 이득선정 방안이 제시되었지만 이러한 방법 또한 마찬가지로 전압 제어기 대역폭을 필터 공진 주파수까지 올릴수는 없다.

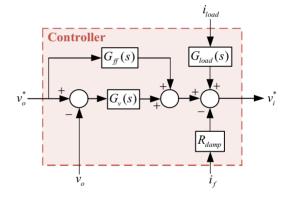

이를 개선하기 위해 그림 4.(b)와 같이 전압 지령에상태 변수를 궤환(feedback) 및 전향 보상(feedforward)하는 개루프(open-loop) 제어기가 제안되었다<sup>[5,9]</sup>. 이러한 개루프 제어기는 동특성이 향상되지만, 출력 전압을 궤환하여 보상하는 제어 루프가 없으므로 입력 외란에 대해 매우 취약하다. 따라서 센서 오차 및 인버터 비선형

(a) Multi-loop control proposed in [6]

(b) Open-loop control proposed in [9]

Fig. 4. Block diagram of the traditional control scheme.

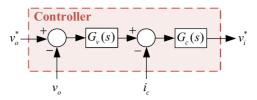

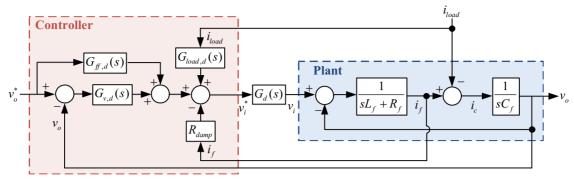

Fig. 5. Block diagram of the proposed control scheme.

성에 대한 세밀한 보상이 필요하다.

따라서 본 논문에서는 이러한 기존 제어기의 단점을 보완한 단일 루프 전압 제어기를 설계하고자 한다. 제안한 전압 제어기는 그림 5와 같은 형태를 지닌다. 입력외란 영향을 억제하고, 전압 제어기의 대역폭을 최대화하기 위하여 출력 전압  $v_o$ 를 궤환 보상한 단일 폐루프 (closed-loop) 형태의 전압 제어기를 사용한다. 또한 과도 특성 개선 및 부하 전류로 인한 전압 왜곡 방지를위해 상태 변수  $i_f$ ,  $i_{load}$ 를 궤환하여 전향 보상에 사용한다.

이는 가상 임피던스(virtual impedance) [10]를 이용한 폐루프 제어기를 개선한 형태로 볼 수 있다. 기존 가상 임피던스 관련 연구에서는 제어 대역폭을 최대화하기 위한 제어기 설계 및 이득 선정 방법에 대해서 고려하지 않았다. 따라서 본 논문에서는 임의 파형 발생기에 적합한 최적 이득 선정 방법에 대해서 추가적으로 논의하고자 한다.

Fig. 6. Block diagram of the proposed controller considering time delay.

## 4. 전압 제어기 이득 선정

## 4.1 부하 전압 제어기 이득 선정

$i_{load} = 0$ ,  $G_{ff}(s) = 0$ 으로 가정하면, 기준 전압에 대한 응답은 식 (6)과 같다.

$$\frac{v_o(s)}{v_o^*(s)} = \frac{K_p s + K_i}{L_f C_f s^3 + (R_f + R_{damp}) C_f s^2 + (1 + K_p) s + K_i}.$$

(6)

미분 제어기는 잡음(noise)에 민감하므로 전압 제어기  $G_v(s)$ 는 식 (7)과 같이 비례-적분(PI) 제어기 형태를 가지도록 한다. 식 (5)와 같이 2차 응답형의 제어 성능을 가지고자 할 경우,  $G_v(s)$ 의 비례-적분 이득 및 댐핑 이 득  $R_{down}$ 는 식 (8), (9)와 같이 정해진다.

$$G_v(s) = K_p + \frac{K_i}{s}. (7)$$

$$K_p = L_f C_f \omega_c^2, \quad K_i = \frac{\omega_c}{2\zeta}. \tag{8}$$

$$R_{damp} = \left(2\zeta_c\omega_cL_f + \frac{1}{2\zeta_c\omega_cC_f}\right) - R_f. \tag{9}$$

출력 LC 필터는 전압 제어 측면에서 시지연(time delay) 요소로 동작하므로 이러한 시지연을 미리 보상하기 위하여 전향 보상기  $G_{ff}(s)$ 를 추가하여 사용할 수있다. 식 (10)과 같은 제어 성능을 가지고자 할 경우  $G_{ff}(s)$ 는 식 (11)처럼 비례-미분(PD) 이득을 가져야 한다. 통상 전압 지령은 잡음을 포함하지 않으므로 지령에 대한 미분 제어기 적용은 큰 문제가 없다.

$$\frac{v_o(s)}{v_o^*(s)} = \frac{2\zeta_c \omega_c s + \omega_c^2}{s^2 + 2\zeta_c \omega_c s + \omega_c^2}.$$

(10)

$$G_{ff}(s) = 2\frac{\zeta_c}{\omega_c}(K_p s + K_i). \tag{11}$$

## 4.2 부하 전류 외란 제거 이득 선정

부하 전류가 흐르게 되면 필터 인덕터 및 능동 댐핑

저항의 전압 강하로 인해 출력 전압이 왜곡되게 된다. 부하 전류에 의한 출력 전압 변동을 막기 위해 전향 보상기  $G_{load}(s)$ 를 사용한다. 이를 통해 식 (12)의 부하 전류에 대한 출력 전압 전달 함수,  $v_o(s)/i_{load}(s)$ 가 0에 가깝도록 만들어줄 수 있다.

$$\frac{v_o(s)}{i_{load}(s)} = \frac{G_{load}(s) - (L_f s + (R_f + R_{damp}))}{L_f C_f s^2 + R_f C_f s + 1}.$$

(12)

$$G_{load}(s) = L_f s + (R_f + R_{damp}). \tag{13}$$

식 (12)에서 분자 항이 0이 되기 위한 제어기 이득은 식 (13)과 같이 설정된다. 측정한 부하 전류를 바로 미분하게 되면 위에서 언급한 잡음 문제로 제어기가 불안정해질 수 있으므로, 실제로는 대역 통과 필터(band pass filter)를 사용하여 미분기를 대체하도록 한다. 단,부하 전류 외란의 영향을 억제하기 위해 대역 통과 필터의 차단 주파수(cut-off frequency)는 가능한 높게 설정하는 것이 유리하다.

## 4.3 디지털 시지연을 고려한 이득 선정

실제 디지털 제어 시스템의 경우, 연산 시간 및 PWM 으로 인해 시지연이 존재한다. 이 때 연산 시간은 샘플링 순간으로부터 PWM 지령이 갱신되는 순간까지의 시간을 의미하며 이는 샘플링 주기  $T_{samp}$ 에 해당한다. 또한 PWM 시지연은 전압 지령이 한 샘플링 주기 동안일정하게 유지되는 것을 의미하므로 영차 홀드(zero order hold)로 모델링할 수 있다. 이러한 디지털 시지연은 식 (14)와 같이 근사하여 모델링할 수 있다.

$$G_d(s) = e^{-1.5T_{samp}s} \approx \frac{1}{1 + 1.5T_{samp}s}.$$

(14)

따라서 샘플링 주기가 클 경우, 그림 6과 같이 시지연을 모델링에 포함하여 각 제어기 이득을 선정하여야 한다. 이를 고려한 각 제어 이득은 식 (15), (16), (17)과 같다. 단, 미분기 사용 시 센서 잡음으로 인해 성능이저하될 수 있으므로 미분기 사용은 최소화하도록 한다.

Fig. 7. Experimental setup: Nonlinear load.

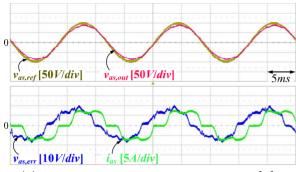

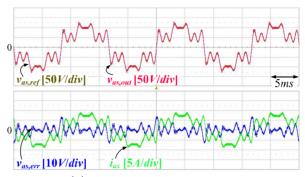

(a) Open-loop control algorithm proposed in [9]

(b) Proposed control algorithm

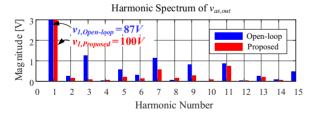

(c) FFT of a-phase output voltage,  $v_{as.out}$

Fig. 8. Experiment 1: Waveforms and harmonic spectrum of  $v_{as.out}$  under sine wave voltage reference.

$$G_{v,d}(s) = (K_p + 1.5 T_{samp} K_i) + \frac{K_i}{s}.$$

(15)

$$G_{ff,d}(s) = 2\frac{\zeta_c}{\omega_c}((K_p + 1.5T_{samp}K_i)s + K_i).$$

(16)

$$G_{load,d}(s) = (L_f + 1.5 \, T_{samp} R_f) s + (R_f + R_{damp}). \tag{17} \label{eq:load_def}$$

# 5. 실험 결과

부하를 포함한 실험 세트는 그림 7과 같이 구성하였

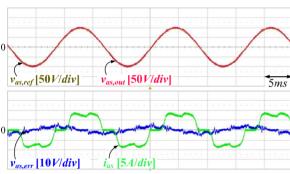

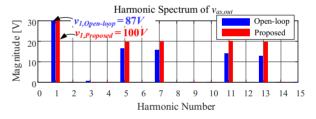

(a) Open-loop control algorithm proposed in [9]

(b) Proposed control algorithm

(c) FFT of a-phase output voltage,  $v_{as.out}$

Fig. 9. Experiment 2: Waveforms and harmonic spectrum of  $v_{as.out}$  under multiple harmonics voltage reference.

다. 또한 동등한 조건에서 제어기의 성능 비교를 위해 비감쇠 자연 주파수  $\omega_c$ 를 필터 차단 주파수  $\omega_f$ 로, 감쇠 계수  $\zeta_c$ 는 1로 동일하게 설정하였다. 스위칭 주파수는 20kHz, 데드 타임은  $2\mu$ s 이며, 비선형 부하 특성을 가지는 3상 다이오드 부하에 대해 실험을 수행하였다.

그림 8은 전압 지령이 60Hz, 100V 정현파일 때 각 전압 제어기의 성능을 보여준다. 이 때,  $v_{as,ref}$ 는 a상 전압 지령,  $v_{as,out}$ 은 a상 출력 전압,  $v_{as,err}$ 는 a상 전압 오차,  $i_{as}$ 는 a상 부하 전류를 나타낸다. 이 때 a상 전압 오차  $v_{as,err}$ 는 a상 전압 지령과 a상 출력 전압의 차이,  $v_{as,ref}-v_{as,out}$ 로 정의된다. 기존 개루프 제어기는 인버터 비선형성 및 센서 오차로 인해 그림 8.(a)와 같이 출력 전압에 큰 왜곡이 발생하는 것을 확인할 수 있다. 하지만, 제안된 페루프 제어기의 경우 그림 8.(b)와 같이 정상 상태에서 전압 지령을 잘 따라가는 것을 확인할 수 있다. 그림 8.(c)는 각 제어기의 a상 출력 전압을 FFT한 결과를 나타낸다. 기존 제어기의 경우 기본파 전압 크기

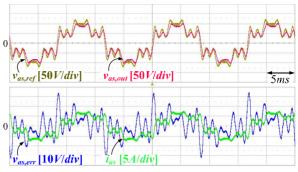

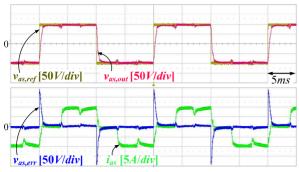

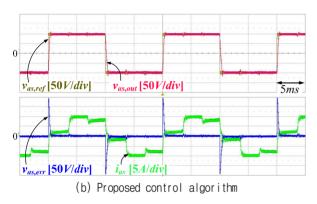

(a) Open-loop control algorithm proposed in [9]

Fig. 10. Experiment 3: Waveforms under square wave voltage reference.

가 정확히 합성되지 못할 뿐만 아니라, 인버터 비선형성을 비롯한 여러 외란에 의해 고조파가 발생하는 것을 확인할 수 있다. 그에 비해 제안된 제어기의 경우 기본 파 100V를 정확하게 합성하며 저차 고조파가 감쇄되는 것을 확인할 수 있다. 또한 제안된 제어기를 사용할 경우 40차 이하의 출력 전압 THD(Total Harmonics Distortion)가 2.7%에서 1.3%로 감소하는 것을 확인할수 있다.

그림 9는 기본파 전압 지령 60Hz, 100V와 더불어 5, 7, 11, 13 고조파를 각각 20V씩 동시에 합성할 때, 각전압 제어기의 성능을 보여준다. 그림 9.(a)의 기존 개루프 제어기의 파형과 달리, 제안된 폐루프 제어기의 파형의 경우 그림 9.(b)와 같이 출력 전압이 전압 지령을 잘추종하는 것을 확인할 수 있다. 그림 9.(c)는 각 제어기의 경우 기본파 전압이 정확하게 합성되지 못할 뿐만아니라, 주파수가 높아질수록 고조파 합성 능력이 감소하게 된다. 그에 비해 제안된 제어기의 경우 13 고조파까지 여전히 정확히 전압 지령을 합성하는 것을 확인할수 있다.

그림 10은 전압 지령이 50Hz, 100V 구형파(square wave)일 때 각 전압 제어 알고리즘의 성능을 보여준다. 이 때 인버터 비선형성으로 인한 영향을 최소화하기 위해 인버터 비선형 보상 함수를 추가하였다. 기존 개루프제어기는 그림 10.(a)와 같이 동일한 전압 지령을 인가

한 상태에서도 부하 전류에 따라 출력 전압이 변동하는 것을 볼 수 있다. 따라서 부하 전류 외란에 따라 전압 제어기의 성능이 크게 변동하여 구형파 전압 지령을 잘 따라가지 못한다. 이에 비해 제안된 제어기의 경우 폐루 프 형태로 구성되어 그림 10.(b)와 같이 부하 전류에 무 관하게 전압 지령을 잘 추종하는 것을 확인할 수 있다.

## 6. 결 론

본 논문에서는 3상 임의 파형 발생기를 위한 단일 루프 전압 제어기를 제안하였다. 제안된 제어기는 부하전류 및 인버터 비선형성과 같은 각종 외란에 강인하면서도 제어 대역폭을 LC 필터의 공진 주파수까지 늘릴수 있는 이점을 가진다. 또한 필터 파라미터 및 디지털시지연을 고려하여 제안된 제어기에 최적화된 제어 이득 선정 방법을 제시하였다. 최종적으로 실험을 통해 기존 전압 제어기에 비해 제안된 단일 루프 제어기가 높은 동특성 및 외란에 강인한 특성을 가지는 것을 확인할 수 있었다. 이러한 전압 제어기는 높은 전압 대역폭을 필요로 하는 다양한 응용 분야에 사용될 수 있을 것으로 기대된다.

### References

- [1] K. S. Low, "A DSP-based variable AC power source," IEEE Trans. Instrum. Meas., Vol. 47, No. 4, pp. 992 -996, 1998.

- [2] F. R. S. Vincenzi, L. Silva, L. C. G. De Freitas, M. A. A. Freitas, E. R. Fernandes, J. B. Vieira, and L. C. Freitas, "Programmable AC power source used to analyze electronic equipment performance in the electrical power system quality concept," in *Proc. IEEE APEC*, pp. 1931 1937, 2008.

- [3] M. Schweizer, I. Lizama, T. Friedli, and J. W. Kolar, "Comparison of the chip area usage of 2-level and 3-level voltage source converter topologies," in *Proc. IEEE IECON*, pp. 391-396, 2010.

- [4] R. Zhang, V. H. Prasad, D. Boroyevich, and F. C. Lee, "Three-dimensional space vector modulation for four-leg voltage-source converters," *IEEE Trans. Power Electron.*, Vol. 17, pp. 314–326, 2002.

- [5] H. Kim, S. J. Lee, and S. K. Sul, "Design of the feed forward controller in digital method to improve transient characteristics for dynamic voltage restorers," *The Trans. of the Korean Institute of Power Electronics*, Vol. 9, No. 3, pp. 275–284, 2004.

- [6] M. J. Newman, D. N. Zmood, and D. G. Holmes, "A comparative analysis of multiloop voltage regulation strategies for single and three-phase UPS systems," *IEEE Trans. Power Electron.*, Vol. 18, No. 5, pp. 1176–1185, Sep. 2003.

- [7] M. Vilathgamuwa, A. A. D. Ranjith Perera, and S. S. Choi, "Performance improvement of the dynamic voltage restorer with closed-loop load voltage and current-mode control," *IEEE Trans. Power Electron.*, Vol. 17, No. 5, pp. 824 834, Sep. 2002.

- [8] F. Liu, Y. Zhou, S. Duan, J. Yin, B. Liu, and F. Liu, "Parameter design of a two-current-loop controller used in a grid-connected inverter system with LCL filter," *IEEE Trans. Ind. Electron.*, Vol. 56, No. 11, pp. 4483 - 4491, Nov. 2009.

- [9] H. Kim and S. K. Sul, "Compensation voltage control in dynamic voltage restorers by use of feed forward and state feedback scheme," *IEEE Trans. Power Electron.*, Vol. 20, No. 5, pp. 1169–1177, Sep. 2005.

- [10] X. Wang, Y. W. Li, F. Blaabjerg, and P. C. Loh, "Virtual-impedance-based control for voltage-source and current-source converters," *IEEE Trans. Power Electron.*, Vol. 30, No. 12, pp. 7019 - 7037, Dec. 2015.

## 김현식(金炫植)

1988년 10월 18일생. 2013년 서울대 공대전기·정보공학부 졸업. 2013년~현재 동 대학원 전기·컴퓨터공학부 석박사과정.

## 지승준(池丞焌)

1980년 8월 15일생. 2003년 서울대 공대 전기공학부 졸업. 2005년 동 대학원 전기·컴퓨터 공학부 졸업(석사). 2005년~2011년 삼성전자 생산기술연구소 책임연구원. 2011년~현재 동 대학원 전기·컴퓨터 공학부 박사과정.

## 설승기(薛承基)

1958년 3월 25일생. 1980년 서울대 공대 전기공학과 졸업. 1983년 동 대학원 전기공학과 졸업(석사). 1986년 동 대학원 전기공학과 졸업(공박). 1986년~1988년 University of Wisconsin, Madison 연구원. 1988년~1990년

LG산전 책임연구원. 2003년~2004년 일본 Yaskawa Electric Corp. 상임연구고문. 1991년~현재 서울대 전기·정보공학부 교수. 2005년~2007년 서울대 공대 부학장. 2008년~2011년 기초 전력연구원 원장. 2011년 ICPE'11 General Chairman. 2012 년~2014년 당 학회 JPE Editor-in-Chief. 당 학회 명예회장.