# Trade-Off Strategies in Designing Capacitor Voltage Balancing Schemes for Modular Multilevel Converter HVDC

# Taesik Nam\*, Heejin Kim\*\*, Sangmin Kim\*\*, Gum Tae Son\*, Yong-Ho Chung\*, Jung-Wook Park\*\*, Chan-Ki Kim\*\*\* and Kyeon Hur<sup>†</sup>

**Abstract** – This paper focuses on the engineering trade-offs in designing capacitor voltage balancing schemes for modular multilevel converters (MMC) HVDC: regulation performance and switching loss. MMC is driven by the on/off switch operation of numerous submodules and the key design concern is balancing submodule capacitor voltages minimizing switching transition among submodules because it represents the voltage regulation performance and system loss. This paper first introduces the state-of-the-art MMC-HVDC submodule capacitor voltage balancing methods reported in the literatures and discusses the trade-offs in designing these methods for HVDC application. This paper further proposes a submodule capacitor balancing scheme exploiting a control signal to flexibly interchange between the on-state and the off-state submodules. The proposed scheme enables desired performance-based voltage regulation and avoids unnecessary switching transitions among submodules, consequently reducing the switching loss. The flexibility and controllability particularly fit in high-level MMC HVDC applications where the aforementioned design trade-offs become more crucial. Simulation studies for MMC HVDC are performed to demonstrate the validity and effectiveness of the proposed capacitor voltage balancing algorithm.

**Keywords**: Modular multilevel converter (MMC), High voltage direct current (HVDC), Capacitor voltage balancing

#### 1. Introduction

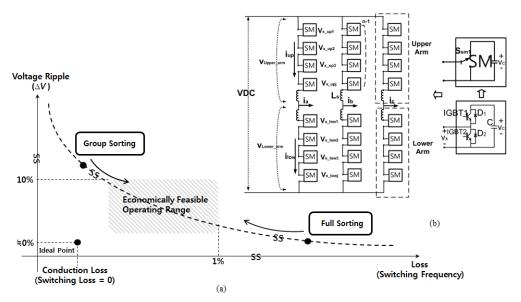

This paper investigates a crucial engineering trade-off in designing capacitor voltage balancing schemes for a modular multilevel converter (MMC) HVDC: voltage regulation performance and switching loss. The MMC has numerous stacks of identical converters called submodules [1-5]. For the half bridge configuration, a submodule has two switching devices implemented by antiparallel connections of a fully controllable insulated-gate bipolar transistor (IGBT) and capacitor to generate the output voltage [6] (See Fig. 1(b)). As the level of the MMC or the number of submodules increases to enable higher power transmission, the capacitor voltage balancing task becomes the primary technical challenge because the balancing scheme may adversely impact on system loss, device ratings as well as control performance, if not properly designed [7]. As conceptually illustrated in Fig. 1(a), there is a trade-off between voltage regulation performance and loss. The higher switching frequency generates the lower voltage ripple ( $\Delta V$ ) leading to better capacitor voltage

Received: November 22, 2014; Accepted: February 3, 2016

regulation for a given capacitance notwithstanding the higher switching loss. Large capacitance should allow for small voltage ripple and reduced loss due to reduced switching needs among submodules for the purpose of voltage balancing. It is worth noting that an ideal point in Fig. 1(a) provides the perfect voltage regulation and minimum loss comprising inherent conduction loss dominantly. However, the ideal point is prohibitively uneconomical for the high voltage applications because the ideal point can be achieved in extremely large submodule capacitance. The trade-off between voltage regulation and loss is balanced on the dotted line in practice. Ranking and switching all submodules by their capacitor voltages, often named 'Full Sorting' at every switching instant should provide the highest voltage regulation for the designed number of submodules and capacitance at the cost of highest switching loss. Thus, an operating point should be determined in technically and economically feasible operation range.

Because the capacitor voltage balancing should be the most basic yet critical functionality of the MMC, various balancing techniques of the capacitor voltage have been discussed in [1-18]. Reference [1] deals with two types of pulse width modulated MMC (PWM-MMC), focusing on their circuit configurations and voltage balancing control. Combining both averaging and balancing controls enables the PWM-MMC to achieve voltage balancing and the results are verified by simulation and experiment. In [2],

<sup>†</sup> Corresponding Author: Yonsei University, Korea. (khur@yonsei.ac.kr)

<sup>\*</sup> LSIS Co. Ltd, Korea

<sup>\*\*</sup> Dept. of Electrical and Electronic Engineering, Yonsei University, Korea

<sup>\*\*\*</sup> Korea Electric Power Research Institute Power System Research Laboratory, Korea

Fig. 1. (a) Engineering Trade-off in Designing MMC System. (b) MMC Topology

three capacitor voltage balancing strategies are proposed and investigated: 1) a slow-rate balancing strategy based on the conventional sorting method; 2) a hybrid balancing strategy that combines a predictive method with the conventional sorting method; and 3) a fundamental frequency balancing strategy. A computationally efficient voltage balancing algorithm without arm current measurements has been proposed [3]. The method reduces the number of the sensors and decreases the costs. A reduced switching frequency voltage balancing algorithm is developed for MMC, and a circulating currentsuppressing controller is proposed for the three-phase MMC in [6]. This voltage balancing algorithm reduces the average device switching frequency and distributes the energy equally among the submodule capacitors. The combination of Nearest Level Modulation (NLM) and optimized capacitor voltage balancing control using a maintaining factor reduces the switching frequency as well as the switching losses of semiconductors in [7]. Closed loop control for the submodule voltage balancing is introduced with Carrier Phase Shifted Pulse Width Modulation (CPSPWM) in [8] and [9]. The submodule capacitor voltage balancing with phase disposition PWM (PDPWM) for MMC is used in [10-13]. The submodule capacitor voltages within each arm are measured and sorted, and the number of submodules to be switched on/off is determined. These methods have to be executed at the equivalent switching frequency of one arm, posing a heavy computational burden as the number of submodules becomes increasing to a real high voltage system. The balancing methods in [14-16] are based on a sorting method and individual measurement of submodule capacitor voltages, selecting the process based on the direction of the arm current for charging/discharging the selected submodule. It is obvious, however that the heavy computational intensity may hamper their applications to

high voltage (or level) systems. It is also interesting to note methods of using extra switching devices and capacitors for the self-balancing of voltages among modules in [17] and the prediction of each capacitor voltage as a function of the arm current and the states of the submodule switches [18]. A reduced the switching frequency based on the full sorting are proposed [6, 7]. The methods help reduce the system loss as illustrated in Fig. 1(a) while possibly compromising the voltage regulation.

The voltage balancing performance, however, has been investigated and validated for MMC with a small number of levels using high switching frequency modulation schemes. Higher switching frequency allows for better regulation at the cost of higher loss, which becomes the critical constraint for a high voltage application requiring a large number of levels. Therefore, a modulation method should be designed to generate a waveform with a large number of levels with minimal switching frequency that still guarantees the desired balancing performance. This research develops an effective balancing scheme based on the Group Sorting where submodules are grouped and sorted by prior switching states (on or off) [19] with supplementary ad-hoc switchings. These 'ad-hoc' switchings are commanded to interchange the highest voltage capacitor with the lowest voltage capacitor based on the current direction in order to maintain the desired voltage regulation performance. The low switching frequency modulation such as NLM is set as a basis to minimize system loss and it changes the on/off state of submodules based on the current direction that overrides the charge and discharge condition of the submodule to keep the desired voltage regulation. As the qualifier, ad-hoc implies, the method can adjust the switching frequency and should bring significant benefits of system controllability and flexibility to comply with dynamically changing grid condition. The paper comprehensively addresses the design trade-offs encountered in designing the high-level MMC with desired low switching frequency modulation, and further presents the advantages of the proposed voltage balancing method with numerous simulation studies in terms of total harmonic distortion (THD), switching frequency and submodule voltage waveforms. Understanding of these trade-offs should be highly beneficial for system planners.

This paper is organized as follows: Section 2 presents theoretical background on the design trade-off between the desired voltage regulation and switching loss. Section 3 describes balancing schemes based on the namely, Full Sorting, Advanced Full Sorting, and Group Sorting methods for MMC in respect to the design trade-off followed by an effective capacitor voltage balancing control method proposed in Section 4. Section 5 demonstrates the validity and effectiveness of the proposed method through simulation studies for MMC, in particular for HVDC based on PSCAD/EMTDC. Finally, conclusions are provided in Section 6.

## 2. Design Trade-off between the Voltage Regulation and Switching Loss

This section briefly provides a theoretical overview on the switching frequency and its impacts on the converter loss and voltage regulation performance, i.e. voltage ripple.

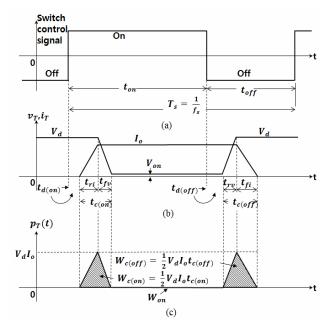

Semiconductor switching devices such as MOSFETs, and IGBTs inherently dissipate power during the switchings. Fig. 2 illustrates the switching characteristics of the generic

Fig. 2. Generic-switch switching characteristics: (a) switch waveforms; (b) voltage and current waveforms according to switch; (c) instantaneous switch power loss (adapted from [20]).

switching device and the switching loss due to voltage and current present simultaneously during the turn-on crossover interval  $t_{c(on)}$ , where

$$t_{c(on)} = t_{ri} + t_{fv} \tag{1}$$

and  $t_{c(off)}$ , where

$$t_{c(off)} = t_{rv} + t_{fi} \tag{2}$$

The energy dissipated in the switch during this turn-on and off transition can be approximated from Fig. 2(c) as

$$W_{c(on)} = \frac{1}{2} V_d I_o t_{c(on)} \tag{3}$$

$$W_{c(off)} = \frac{1}{2} V_d I_o t_{c(off)}$$

(4)

where any energy dissipation during the turn-on and turnoff delay interval  $t_{c(on)}$  and  $t_{c(off)}$  are ignored since they are much smaller than  $W_{c(on)}$  and  $W_{c(off)}$ . It should also be noted that there are  $f_s$  such turn-on and turn-off transitions per second. Hence, the average switching power loss  $P_s$  in the switch due to these transitions can be approximated from (3) and (4) as

$$P_{s} = \frac{1}{2} V_{d} I_{o} f_{s} (t_{c(on)} + t_{c(off)})$$

(5)

This fundamental relationship between the loss and the switching frequency surely indicates that the average switching loss can be controlled by the switching frequency [20].

Further, the dissipated energy by a submodule capacitor as its voltage drops from  $V_{peak}$  to  $V_{min}$  is expressed as follows [21]:

$$\frac{1}{2}C_{sm}V_{peak}^2 - \frac{1}{2}C_{sm}V_{min}^2 = P\,\Delta t$$

(6)

where  $C_{sm}$  is submodule capacitance and  $P\Delta t$  is energy consumed (based on the assumption of constant power at P) during that time interval. Eq. (6) can be described the voltage term by

$$V_{peak}^2 - V_{\min}^2 = \frac{2P\Delta t}{C_{sm}}$$

(7)

$$(V_{peak} - V_{\min})(V_{peak} + V_{\min}) = \frac{2P\Delta t}{C_{sm}}$$

(8)

$$(V_{peak} - V_{\min}) = \frac{2P\Delta t}{C_{sm}(V_{peak} + V_{\min})}$$

(9)

Small ripple approximation allows for the expression of voltage term on the right side as below:

Trade-Off Strategies in Designing Capacitor Voltage Balancing Schemes for Modular Multilevel Converter HVDC

$$V_{peak} + V_{\min} \approx 2V_{peak} \tag{10}$$

$\Delta t$  can also be expressed as  $\Delta t \approx T/2$ . Since *T* is  $1/f_s$ , Eq. (9) can further be arranged as in the following:

$$(V_{peak} - V_{min}) = V_{peak-to-peak-ripple} \approx \frac{P}{2f_s C_{sm} V_{peak}}$$

(11)

It is obvious that the lower the switching interval, the lower the  $V_{peak-to-peak-ripple}$  as concisely presented below:

$$f_s \propto \frac{1}{V_{peak-to-peak-ripple}}$$

(12)

Combining the observations above in (5) and (12), the relationship among frequency, voltage variation, and the loss can be summarized below:

$$f_s \propto \frac{P_s}{V_{peak-to-peak-ripple}}$$

(13)

#### 3. Capacitor Voltage Balancing Control

This section discusses three well reported methods for balancing the submodule capacitor voltage balancing control: Full Sorting, Advanced Full Sorting and Group Sorting. It then presents an effective balancing based on Group Sorting with a supplementary ad-hoc switching signal incorporating the design trade-off of voltage regulation and loss for each balancing method.

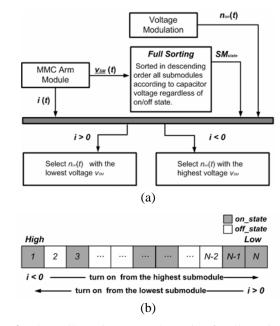

#### 3.1 Full sorting

Full Sorting may be the most basic but intuitive method for ranking all the measured voltages of the submodule capacitors at every switching instant and sequencing an order for turning on or off switches. The governing law states that the on-state submodules charge the corresponding capacitors for positive arm current and discharge the capacitors for negative arm current. The off-state submodules are bypassed regardless of the current direction. If the arm current is in the positive direction, then the on-state submodules in an upper or lower arm with the lowest voltages are selected to be turned on. The corresponding capacitor voltages then increase due to the charging process. If the arm current is negative, then the on-state submodules with the highest voltages are selected to be turned off and the corresponding capacitor voltages decrease. The balancing control using this Full Sorting scheme is shown in Fig. 3. In order to reduce the sensing cost, the current direction information can be derived from the voltage difference of two subsequently measured voltage samples [22].

Since it determines the on-state by checking the voltage

**Fig. 3.** The Full Sorting: (a) Schematic of Full Sorting; (b) Arrangement and operation of each submodule.

of each submodule capacitor at each sampling time, on/off switching of the submodule occurs frequently.

Therefore, voltage regulation of the capacitor performs best and harmonics of the generated voltage waveforms could be minimal; a method focusing on the improvement of voltage regulation performance represented on the yaxis in Fig. 1(a). However, the undesired high loss due to frequent switching is a critical constraint for high voltage applications as detailed with numerical data and graphs in Section 5.

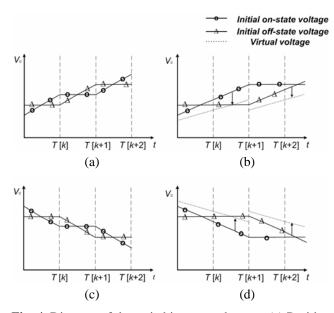

#### 3.2 Advanced full sorting

The Advanced Full Sorting optimizes the designing capacitor voltage balancing schemes by adjusting the measured submodule capacitor voltages before the next sorting process. At each sampling time, if the off-state (onstate) submodule capacitor voltage is smaller (greater) than the on-state (off-state) submodule capacitor voltage with the current direction, the submodule of the on/off state exchanges. Multiplying the actual capacitor voltage of the on-state submodule by a maintaining factor (greater than one) increases the likelihood of maintaining the present state and thus avoids the unnecessary switching [7] as illustrated in Fig. 4. The Advanced Full Sorting method may be understood as a way to move towards less loss on the x-axis of Fig. 1(a) while not compromising the voltage regulation too much; balancing a trade-off between the voltage regulation and the switching loss.

#### 3.3 Group sorting

In order to avoid successive switching of the same

Fig. 4. Diagram of the switching state changes: (a) Positive arm current without virtual voltage; (b) Positive arm current with virtual voltage; (c) Negative arm current without virtual voltage; (d) Negative arm current with virtual voltage.

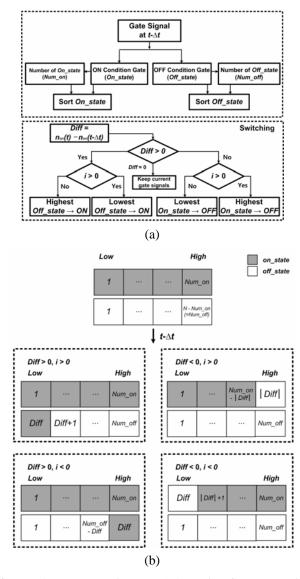

submodule, the previous gate signal of the submodule can be considered. The first step of the Group Sorting scheme is classification of the groups by the previous state (onstate and off-state) of the submodules at the switching instant. Each group is sorted independently by its submodule capacitor voltages. Also, the  $n_{on}(t)$ , which is the number of submodules, must be turned on at the current time step (See Fig. 3), and the arm current is then used to determine the individual gate signals at the current time step. As shown in Fig. 5, the number of difference on-state submodules in an arm (*Diff*) at the previous time step  $(t-\Delta t)$ and that of the current time step (t) is positive, one of the off-group submodules is commanded to be turned on. A submodule with the highest (lowest) voltage value in the off-group is selected to discharge (charge) the submodule when the arm current is flowing negative (positive). When the sign of the *Diff* is negative, one of the on-state group submodules has to be turned off. Depending on the arm current direction, either the highest or lowest submodule is selected. In order to deal with numerous Diff in a single time step, the above process is repeated for each Diff. This scheme produces equally distributed capacitor voltage and switching commutation, which increases the mechanical reliability of power devices and reduces the power losses for the installed device [23].

Group Sorting focuses on reducing the switching loss. By switching the highest or lowest submodule depending on the current direction at each sampling time, successive on/off switching of the same submodule occurs rarely. Therefore, the switching frequency of the submodule device and switching loss is the lowest compared with the

Fig. 5. The group sorting: (a) Schematic of group sorting [5]; (b) Arrangement and operation of each submodule.

above algorithms. However, the performance of the capacitor voltage can be compromised as detailed in Section 5.

## 4. Proposed AD-HOC Switching Method for Voltage Balancing

The aforementioned Group Sorting complements the disadvantages of the Full Sorting method and improves the converter efficiency remarkably. As discussed in the previous Section 3.3, by dividing into two groups from the gate signal at previous time step  $(t-\Delta t)$  and operating only the submodules in one group depending on *Diff*, all submodules can have one or less than one time state change denoted as *N* during the half period of the output waveform. Since the output waveform is synthesized by

switching in or out submodule capacitor, the output voltage step transition is mostly one submodule capacitor voltage in the steady-state operation. The submodule that maintains each on or off state at the current time step does not participate in the switching until state variation of the total switching number occurs, which may adversely impact on the capacitor voltage balancing. The proposed method is designed to overcome these weaknesses.

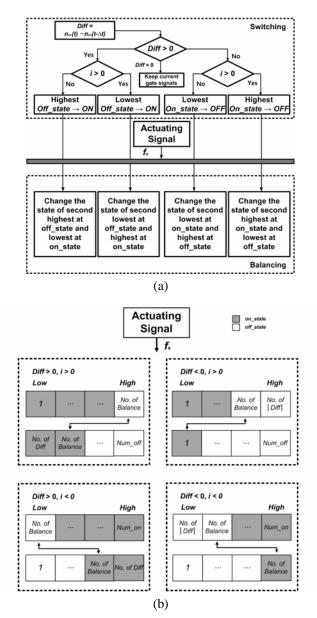

The balancing is improved by augmenting the switching of the submodules determined from the Group Sorting. Additional switching is fired by actuating a signal whose frequency is determined according to the external variable as distinct from firing due to N change. The frequency of the actuating signal in this paper is calculated as (14).

**Fig. 6.** Proposed balancing method: (a) Schematic of additional switching method; (b) Arrangement and operation of each submodule.

$$f_{as} = 2k \cdot N \cdot f_s \tag{14}$$

where  $f_{as}$  is the actuating signal frequency, k is the number of exchange submodules for balancing, N is the number of submodules in an arm and  $f_s$  is the system frequency.

The basic operating strategy is illustrated in Fig. 6 and is described as follows:

- Under positive *Diff* condition, the second lowest (second highest) module in off-state is turned on if the current direction is positive (negative) because the highest (lowest) module is already turned on. Then, in order to synchronize the number of on-state submodules with *N* change, the highest (lowest) submodule in on-state is turned off.

- Under negative *Diff* condition, the second highest (second lowest) module in on-state is turned on if the current direction is positive (negative) because the highest (lowest) module is already turned on. Then, in order to synchronize the number of off-state submodules with state variation, the lowest (highest) submodule in off-state is turned.

- In all cases, the number of on/off submodule for improving the voltage balance can be flexibly set or adjusted in either direction by an external command as needed.

Compared with the Group Sorting method, the proposed balancing algorithm may remarkably reduce the THD by reducing the voltage ripple. As described in [19], this method brings the desired computational efficiency for high voltage applications and flexibility in providing additional switching signal adaptive to the changing grid condition.

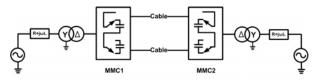

#### 5. Simulation Results

The performance of proposed capacitor voltage balancing method is evaluated for an MMC-HVDC using PSACD/ EMTDC. As depicted in Fig. 7, the HVDC transmission system benchmarked the Trans Bay Cable project [24] designed as a mono-polar structure with DC voltage of  $\pm$  200 kV and submodule capacitance of 4.5 mF [25], and number of submodules per arm of 200. The system is designed to transmit 400 MW from MMC 1 to MMC 2. The main circuit parameters are listed in Table 1. The NLM and desired system control functionalities (*P* control and  $V_{dc}$  control, etc.) are commonly implemented in the

Fig. 7. Schematic diagram of MMC-HVDC system.

| Items                                    | Values              | Comments                      |  |

|------------------------------------------|---------------------|-------------------------------|--|

| Active power <b>P</b>                    | 400 MW              | 1.0 pu                        |  |

| AC system voltage at rectifier $U_r$     | 230 kV              | L-L, rms                      |  |

| AC system voltage at inverter $U_i$      | 115 kV              | L-L, rms                      |  |

| Short Circuit Ratio (SCR) at the PCC     | 3.5                 |                               |  |

| Transformer ratio at rectifier $U_r/U_v$ | 230 kV/<br>180.5 kV | $Y_o / \Delta$                |  |

| Transformer ratio at inverter $U_i/U_v$  | 115 kV/<br>180.5 kV | Y <sub>o</sub> / Δ            |  |

| DC bus voltage $U_{dc}/2$                | 200 kV              | $U_{dc} = \pm 200 \text{ kV}$ |  |

| Number of submodules per Arm N           | 200                 |                               |  |

| submodule capacitance $C_o$              | 4.5 mF              |                               |  |

| Arm inductance <i>L<sub>o</sub></i>      | 15 mH               |                               |  |

| submodule capacitor voltage $U_c$        | 2 kV                |                               |  |

| Modulation index k                       | 0.75                |                               |  |

| Sampling frequency $f_s$                 | 10 kHz              |                               |  |

| DC cables                                | 88 km               |                               |  |

Table 1. Main Circuit Parameters of the Simulation System

simulation system. In order to evaluate the performance of the proposed capacitor voltage balancing scheme, the capacitor voltages of 20-submodules among the 200submodules in the upper arm of phase A are selected and compared with those of three conventional voltage balance methods.

For the convenience of presenting the results, Full Sorting, Advanced Full Sorting, Group Sorting and finally the proposed ad-hoc switching method are referred to be Methods I - IV, respectively in the following.

Figs. 8 and 9 illustrate the capacitor voltage waveforms and corresponding gate signals to the switching submodules. Fig. 8 compares the submodule capacitor voltages of the upper arm in phase-A during 6-cycles of period for four different balancing methods (Full Sorting, Advanced Full Sorting, Group Sorting and proposed Ad-hoc switching method are referred to Method I – IV in this section). Fig. 8(a) shows that the capacitor voltages become perfectly balanced with the Method I: the voltages performance should be the best among four different methods.

However, the switching loss is the highest compared with the others due to the higher average switching frequency. Fig. 8(b) is presented for the result of Method II with a switching frequency of 169 Hz. Fig. 8(b) shows that the capacitor voltages are well balanced, but the capacitor voltage ripple is larger than Method I because the average switching frequency is lower than Method I. Fig. 8(c) is the result employing the Method III. The switching frequency is calculated to be 50 Hz, which is the lowest among four methods. However, the submodule capacitor voltages are not well balanced and the peak-to-peak voltages are remarkable. In comparison with Fig. 8(a), this figure shows that the capacitor voltages become unstable and the magnitude of the capacitor ripple is very large because of the low switching frequency.

Fig. 8(d) illustrates the result of Method IV, similar to Fig. 8(b). This resulted in the same 169 Hz switching frequency as the Method II and the proposed ad-hoc

Fig. 8. Comparison of submodule capacitor voltage with each balancing method: (a) Method I; (b) Method II; (c) Method III; (d) Method IV.

Table 2. Characteristic of each Balancing Method

| Balancing<br>Method | $f_{sw}(\mathrm{HZ})$ | THD% of $v_{ac}$ | $P_{\scriptscriptstyle Loss}^{\scriptscriptstyle SW}$ % | $P_{\scriptscriptstyle Loss}^{cond}$ % | $P_{\scriptscriptstyle Loss}^{\scriptscriptstyle total}$ % |

|---------------------|-----------------------|------------------|---------------------------------------------------------|----------------------------------------|------------------------------------------------------------|

| Method I            | 9140                  | 0.25             | 8.11                                                    | 0.45                                   | 8.56                                                       |

| Method II           | 169                   | 1.03             | 0.15                                                    | 0.45                                   | 0.60                                                       |

| Method III          | 50                    | 1.59             | 0.04                                                    | 0.45                                   | 0.49                                                       |

| Method IV           | 169                   | 0.61             | 0.15                                                    | 0.45                                   | 0.60                                                       |

switching method successfully balances the capacitor voltages and the peak-to-peak capacitor voltage ripples are compared to Fig. 8(c). Fig. 9(a)-(d) compare the gate signals of one phase on the upper arm submodules under the four different modulation during 3-cycles to illustrate the switching operation or switching frequency mentioned above.

Table 2 summarizes the study results in terms of the switching frequency, THD, switching, conduction and total losses for mentioned voltage balancing methods. The estimated switching and conduction losses are calculated as the percentage of transferred active power based on the datasheet of 5SNA1200G330100 insulated-gate bipolar transistors (IGBTs) [26-28]. For accurate

Fig. 9. Gating signal of one switching device in submodule with each balancing method: (a) Method I; (b) Method II; (c) Method III; (d) Method IV.

comparison, we set the same switching frequency to the proposed ad-hoc switching method (Method IV) and the Advanced Full Sorting (Method II). As presented in Table 2, the same switching frequency leads to the same loss: Compare Methods II and IV. However, the THD of Method II is higher than that of the Method IV because the use of virtual voltage does not allow for uniformly distributed switchings. The Method IV is computationally efficient as mentioned in the previous Section 4.

### 6. Conclusions

This paper has presented a key design trade-off in designing capacitor voltage balancing schemes for MMC-HVDC: voltage regulation performance vs. converter switching loss. We have presented theoretical basis on these coupled attributes and further investigated the performance of three well-reported submodule capacitor voltage balancing methods (Full Sorting, Advanced Full Sorting and Group Sorting) from the perspective of design tradeoff. We have then proposed a new balancing scheme designed for balancing the design trade-off flexibly in operations as well.

The method allows for additional switching of the submodules adaptive to changing grid condition and reinforces the benefit (minimal loss) of using the Group Sorting while not compromising the voltage regulation performance. We have demonstrated the flexibility and effectiveness of the proposed balancing scheme through simulation studies for a practical system using PSCAD/ EMTDC with reference to the selected conventional schemes. The study presents that the proposed balancing method can significantly reduce the switching loss (as compared with the Full Sorting), THD (as compared with the Advanced Full Sorting and Group Sorting schemes), and submodule capacitor ripple (as compared with the Group Sorting). The flexibility built upon the high efficiency of the proposed method should help relieve the aforementioned design concerns and maximize the performance of the MMC-HVDC.

#### Acknowledgements

This work was supported by the National Research Foundation of Korea(NRF) grant funded by the Korea government (MSIP) (No.2010-0028509) and also supported by the Yonsei University Research Fund of 2015.

## References

- M. Hagiwara and H. Akagi, "Control and experiment of pulse width modulated modular multilevel converters," IEEE Trans. Power Electron., vol. 24, no. 7, pp. 1737-1746, Jul. 2009.

- [2] J. Qin, and M. Saeedifard, "Reduced Switching-Frequency Voltage-Balancing Strategies for Modular Multilevel HVDC Converters," IEEE Trans. Power Delivery, vol. 28, no. 4, pp. 2403-2410, Oct. 2013.

- [3] F. Deng, and Z. Chen, "A Control Method for Voltage Balancing in Modular Multilevel Converters," IEEE Trans. Power Electron., vol. 29, no. 1, pp. 66-76, Jan. 2014.

- [4] Kim, H.; Kim, S.; Chung, Y.; Yoo, D.; Kim, C.; Hur, K., "Operating Region of Modular Multilevel Converter for HVDC with Controlled Second-order Harmonic Circulating Current: Elaborating P-Q Capability," in Power Delivery, IEEE Transactions on (early access).

- [5] G. T. Son, H. J. Lee, T. S. Nam, Y. H. Chung, U. H. Lee, S. T. Baek, K. Hur, and J. W. Park, "Design and Control of a Modular Multilevel HVDC Converter with Redundant Power Modules for Non-Interruptible Energy Transfer," IEEE Trans. on power delivery, vol. 27, no. 3, pp. 1611-1619, July 2012.

- [6] Q. Tu, Z. Xu, and L. Xu, "Reduced switchingfrequency modulation and circulating current sup-

pression for modular multilevel converters," IEEE Trans. Power Del., vol. 26, no. 3, pp. 2009-2017, Jul. 2011.

- [7] M. Guan and Z. Xu, "Control and modulation strategies for modular multilevel converter based HVDC system," in Proc. 37th Annu. Conf. IEEE Ind. Electron. Soc., pp. 849-854, Nov. 2011.

- [8] M. Hagiwara, R. Maeda, and H. Akagi, "Control and analysis of the modular multilevel cascade converter based on double-star chopper cells (MMCC-DSCC)," IEEE Trans. Power Electron., vol. 26, no. 6, pp. 1649-1658, Jun. 2011.

- [9] H. Akagi, "Classification, terminology, and application of the modular multilevel cascade converter," IEEE Trans. Power Electron., vol. 26, no. 11, pp. 3119-3130, Nov. 2011.

- [10] K. Wang, Y. Li, Z. Zheng, and L. Xu, "Voltage balancing and fluctuation suppression methods of floating capacitors in a new modular multilevel converter," IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1943-1954, May 2013.

- [11] S. Rohner, S. Bernet, M. Hiller, and R. Sommer, "Modulation, losses and semiconductor requirements of modular multilevel converters," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2633-2642, Aug. 2010.

- [12] Z. Li, P. Wang, H. Zhu, Z. Chu, and Y. Li, "An improved pulse width modulation method for choppercell-based multilevel inverters," IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3472-3481, Aug. 2012.

- [13] J. Mei, B. Xiao, K. Shen, L. M. Tolbert, and J. Y. Zheng, "Modular multilevel inverter with new modulation method and its application to photovoltaic grid-connected generator," IEEE Trans. Power Electron., vol. 28, no. 11, pp. 5063-5073, Nov. 2013.

- M. Saeedifard and R. Iravani, "Dynamic performance of a modular multilevel back-to-back HVDC system," IEEE Trans. Power Del., vol. 25, no. 4, pp. 2903-2912, Oct. 2010.

- [15] F. Shengfang, Z. Kai, X. Jian, and X. Yaosuo, "An improved control system for modular multilevel converters featuring new modulation strategy and voltage balancing control," in Proc. IEEE Energy Convers. Congr. Expo., Sep. 15-19, 2013, pp. 4000-4007.

- [16] D. Siemaszko, "Fast Sorting Method for Balancing Capacitor Voltages in Modular Multilevel Converters," IEEE Trans. Power Electron., vol. 30, no. 11, pp. 463-470, Jan. 2015.

- [17] I. Kalle, T. Franz, N. Staffan, A. Antonios, H. Lennart, and N. Hans-Peter, "A submodule implementation for parallel connection of capacitors in modular multilevel converters," in Proc. 15th Eur. Conf. Power Electron. Appl., Sep. 2-6, 2013, pp. 1-10.

- [18] K. Ilves, L. Harnefors, S. Norrga, and H.-P. Nee, "Predictive sorting algorithm for modular multilevel converters minimizing the spread in the submodule

capacitor voltages," in Proc. IEEE Asia Downunder, Jun. 3-6, 2013, pp. 325-331.

- [19] G. T. Son, K. Hur, J. W. Park, S. T. Beak, U. H. Lee, and Y. H Chung, "Computationally Efficient Submodule Selection Scheme for Voltage Balancing Controller of Modular Multilevel Converter," in Proc. CIGRE Meeting 2012, Paris, pp. 1-8.

- [20] N. Mohan, T. M. Undeland, and W. P. Robbins, Power Electronics-Converters, Applications and Design, 3rd ed. New York: Wiley, 2003.

- [21] P. T. Krein, Elements of Power Electronics. New York, NY: Oxford Univ. Press, 1998.

- [22] R. Marquardt, and A. Lesnicar, "A new modular voltage source inverter topology," in Proc. Euro. Conf. Power Electron. Appl. (EPE), 2003, CD-ROM

- [23] U. N. Gnanarathna, A. M. Gole, and R. P. Jayasinghe, "Efficient modeling of modular multilevel HVDC converters (MMC) on electromagnetic transient simulation programs," IEEE Trans. Power Delivery, vol. 26, no. 1, pp.316-324. Jan. 2011.

- [24] S. Teeuwsen, "Modeling the Trans Bay Cable project as voltage-sourced converter with modular multilevel converter design," in Proc. IEEE Power Energy Soc. Annu. Meeting, pp. 1-8, Jul. 2011.

- [25] A. Lesnicar, J. Hildinger, and R. Marquardt, "Modulares stromrichterkonzept fr netzkupplungsanwendungen bei hohen spannungen," in Proc. ETG-Fachbericht, Bad Nauheim, Germany, vol. 88, pp. 155-161, Apr. 2002.

- [26] U. Drofenik and J. Kolar, "A general scheme for calculating switching and conduction-losses of power semiconductors in numerical circuit simulations of power electronic systems," Proc. Int. Power Electron. Conf., 2005

- [27] A. D. Rajapakse, A. M. Gole, and P. L. Wilson, "Electromagnetic transients simulation models for accurate representation of switching losses and thermal performance in power electronic systems," IEEE Trans. Power Electron., vol. 20, no. 1, pp. 319-327, Jan. 2005.

- [28] G. T. Son, S. H. Lee, and J. Park, "Power Loss Modeling of Individual IGBT and Advanced Voltage Balancing Scheme for MMC in VSC-HVDC System," J. Elect. Eng. Technol., vol. 9, no. 5, pp. 1471-1481, 2014.

Taesik Nam received his B.S. and Ph.D. degrees in electrical engineering from Yonsei University, Seoul, Korea in 2008 and 2015. Since 2015, he has been with LSIS Co. Ltd., Gyeonggi-do, Korea. Currently, he is the Associate Research Engineer of the HVDC System Research Team, LSIC. His research interests are high-voltage direct-current systems, static var compensation and multilevel voltage source converter.

**Heejin Kim** received the B.S. degree in electrical engineering from Yonsei University, Seoul, Korea, in 2010 and the Ph.D. degree in electrical engineering from Yonsei University, Seoul, Korea, in 2015. Currently, he is a Postdoctoral Fellow at the Yonsei University, Seoul, Korea. His research

interests include flexible AC transmission systems/high voltage direct current (FACTS/HVDC) and power electronics applications in power systems.

Sangmin Kim received the B.S. degree in Electrical Engineering from Yonsei University, Seoul, Korea, in 2013. He is currently working on the M.S. and Ph.D. combined degree in Yonsei University, Seoul, Korea. His research interests include high voltage direct current (HVDC) and modular

multilevel converter (MMC) control.

**Gum Tae Son** received the B.S. and Ph.D. degrees from the School of Electrical and Electronic Engineering, Yonsei University, Seoul, Korea, in 2007 and 2013 respectively. He is currently an Associate Research Engineer in the LSIS Co. Ltd., Gyeonggi-do, Korea. His research interests include

flexible ac transmission system, CSC high-voltage directcurrent system, VSC high-voltage direct-current system, wind-turbine generator system and modular multilevel systems design.

**Yong Ho Chung** received the master degree and Ph.D. for Electrical Engineering from the Korea Advanced Institute of Science and Technology (KAIST), Korea in 1985 and 1990, respectively. He was the visiting researcher at the University of Wisconsin-Madison in U.S.A. during 1994 to

1995. Since 1985, he is working for LSIS Co. Ltd., in Korea. Currently, he is the research fellow /V.P. and the head of HVDC research lab. His main research areas are Static Power Converter, UPS, Photovoltaic Inverter, Active Power Filter, Power Quality, Micro-grid System, Dynamic Voltage Restorer, FACTS and HVDC applications.

Jung-Wook Park was born in Seoul, Korea. He received the B.S. degree (summa cum laude) from the Department of Electrical Engineering, Yonsei University, Seoul, Korea, in 1999, and the M.S.E.C.E. and Ph.D. degrees from the School of Electrical and Computer Engineering, Georgia Institute of

Technology, Atlanta, USA in 2000 and 2003, respectively. He is currently an Associate Professor in the School of Electrical and Electronic Engineering, Yonsei University, Seoul, Korea. His current research interests are in power system dynamics, renewable energies based distributed generations, power control of electric vehicle, and optimization control algorithms.

**Chan-Ki Kim** obtained his M.Sc. and Ph.D. degrees in Electrical Engineering from Chung-Ang University, Korea in 1993 and 1996, respectively. Since 1996, he has been with KEPRI, the R&D center of KEPCO (Korea Electric Power Corporation). His research interests are HVDC and Power

Electronics; he developed the HVDC simulator, HVDC commissioning technology and HVDC control algorithms. He received the Technical Award from the Ministry of Science and Technology of the Korean Government and Excellent Paper Awards from KIEE in 2002, 2004 and 2014 respectively. He is a senior member of IEEE and KIEE.

**Kyeon Hur** received his B.S. and M.S. degrees in electrical engineering from Yonsei University, Seoul, Korea, in 1996 and 1998, respectively, and the Ph.D. degree in electrical and computer engineering from The University of Texas at Austin in 2007. He has rejoined Yonsei University since 2010 and leads

a smart-grid research group. His current research interests include FACTS/HVDC, PMU-based analysis and control, integration of variable generation and controllable load, and load modeling. He is an associate editor of Journal of Power Electronics and Journal of Electrical Engineering and Technology.