# A Study on SFCL with IGBT Based DC Circuit Breaker in Electric Power Grid

# SunHo Bae\*, Hongrae Kim\*\*, Jung-Wook Park\* and Soo Hyoung Lee<sup>†</sup>

Abstract – Recently, DC systems are considered as efficient electric power systems for renewable energy based clean power generators. This discloses several critical issues that are required to be considered before the installation of the DC systems. First of all, voltage/current switching stress, which is aggravated by large fault current, might damage DC circuit breakers. This problem can be simply solved by applying a superconducting fault current limiter (SFCL) as proposed in this study. It allows a simple use of insulated-gate bipolar transistors (IGBTs) as a DC circuit breaker. To evaluate the proposed resistive type SFCL application to the DC circuit breaker, a DC distribution system is composed of the practical line impedances from the real distribution system in Do-gok area, Korea. Also, to reflect the distributed generation (DG) effects, several DC-to-DC converters are applied. The locations and sizes of the DGs are optimally selected according to the results of previous studies on DG optimization. The performance of the resistive type SFCL applied DC circuit breaker is verified by a time-domain simulation based case study using the power systems computer aided design/electromagnetic transients including DC (PSCAD/EMTDC®).

**Keywords**: DC circuit breaker, DC distribution system, Insulated-gate bipolar transistor (IGBT), Non-zero-crossing switching, Superconducting fault current limiter (SFCL)

#### 1. Introduction

Recently electrical power systems are facing the huge challenge of providing sustainable living for the human being. As the part of the efforts for the sustainable living, many renewable energy based distributed generations (DGs) have been studied and substantiated by those in academia and industry. The renewable energy based DGs increase the number of DC components because they have at least one internal DC bus. For example, the photovoltaic (PV) intrinsically supplies DC power, and the wind-turbine output is rectified before being supplied to the electrical grid. Also, the DC load has increased rapidly and occupied a large portion of the entire load. Meanwhile, the advanced power electronics have contributed to the battery energy storage system (BESS) as well as to the DG and the DC load. The advancement of the BESS has also contributed to increase in DC buses by disseminating the uninterruptable power systems (UPSs). The increase of the DC buses has inspired many researchers, some of whom are interested in the high efficient DC power system [1-3].

Despite the beneficial effects of the DC power system, several technical issues should be considered before their installation. For example, a DC circuit breaker is

completely different from an AC circuit breaker. The AC circuit breaker opens at the zero-crossing current point to minimize the electrical stress. Unless the breaker opens at the zero-crossing current point, it will suffer from a huge induced voltage that is caused by the large fault current. In a DC system, however, there is no zero-crossing current point, and thus the electrical stress is intrinsically inevitable. Therefore, the circuit breaker probably suffers from the large induced voltage.

A superconducting fault current limiter (SFCL) can reduce the large fault current to a normal level. Based on that, a previous study applied the SFCL to a mechanical circuit breaker [4]. However, it is not an effective approach to install the SFCLs next to all the breakers considering the installation and management costs. This study focuses on minimizing the numbers of the insulated-gate bipolar transistors (IGBTs) by reducing the voltage across the mechanical breakers. The performances of the IGBTs have been verified by many converter applications. To analyze the SFCL and IGBT effects on the power system, the practical system is composed using the real distribution system data from Do-gok area, Korea.

### 2. Implementation of DC Distribution System

### 2.1 Distribution system

In the DC system, the maximum fault current is limited by the converter rating [5]. Therefore, the DC circuit

<sup>†</sup> Corresponding Author: Korea Electrotechnology Research Institute (KERI), Uiwang, Korea. (slee82@keri.re.kr)

School of Electrical and Electronic Engineering, Yonsei University, Seoul, Korea. ({bsunho, jungpark}@yonsei.ac.kr)

<sup>\*\*</sup> Dept. of Electronic Information Engineering, Soonchunhyang University, Ansan, Korea. (hongkim@sch.ac.kr)

Received: November 1, 2016; Accepted: July 3, 2017

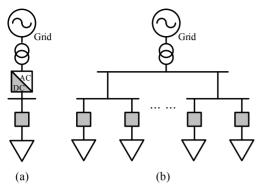

**Fig. 1.** (a) Single feeder DC distribution system, and (b) conventional AC distribution system

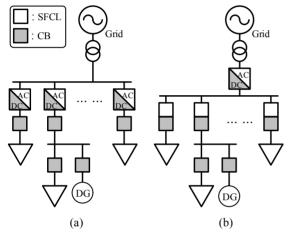

**Fig. 2.** DC distribution systems with (a) small decentralized converters, and (b) large centralized converter

breaker does not suffer from the huge fault current in a single feeder system of Fig. 1(a). However, the real AC distribution system is generally composed of several feeders that are connected in parallel to the substation as shown in Fig. 1(b). That is, the DC distribution system might have multiple feeders in parallel when it is implemented in real world. Therefore, the circuit breakers on each feeder might be damaged by the large fault current.

Based on the conventional system of Fig. 1(b), the DC distribution system can be implemented in two different ways as shown in Fig. 2. In the decentralized converter system of Fig. 2(a), a fault on a feeder does not spread to the other feeders, and the fault current is limited by the converter current rating. In the centralized converter system of Fig. 2(b), in contrast, the fault current becomes large unless there are SFCLs. Nevertheless, the centralized converter system is more realistic considering its high efficiency under normal condition [6]. Its fault current can be limited in the similar level as that of the decentralized converter system by installing the SFCLs on the feeders.

#### 2.2 Modeling of resistive type SFCL

The resistive type SFCL prevents an increase in the

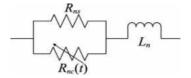

Fig. 3. The simple structure of a resistive type SFCL unit

short-circuit current due to its rapid current limiting ability. Despite multiple concepts for the designing of SFCLs have been conceived in previous studies, the resistive type SFCLs is commonly used for small size and low cost [7, 8].

The simple structure of the resistive (non-inductive winding) SFCL unit is shown in Fig. 3 [9]. A unit is composed of the stabilizer resistance of the n-th unit,  $R_{ns}$ , the superconducting resistance of the n-th unit,  $R_{nc}(t)$ , and the coil inductance of the n-th unit,  $L_n$ .  $R_{ns}$  and  $R_{nc}(t)$  have been connected in parallel. The subscript n denotes the number of connected units [9]. In the steady-state condition, the total composite resistance becomes zero regardless of the  $R_{ns}$  because the value of  $R_{nc}(t)$  is zero. However, the value of  $R_{nc}(t)$  becomes non-zero time-varying parameters due to the larger current than the critical current during a fault, depending on their unique characteristic.

The resistive type SFCL requires series and parallel arrange structure for high voltage and large current. The series connection of the resistive type SFCLs causes voltage balancing problems [10]. In this paper, it is assumed that the resistive type SFCLs connected in series are operated simultaneously in the quenching state. The value of total resistance ( $R_{SFCL}$ ) of the series connected resistive type SFCL during a fault depends on the total number of units in Fig. 3, which are connected in series [11]. The value of  $L_n$  is determined by the coils, which are wound to have low inductance. Therefore, the value of  $L_n$  is so small that its effect can be ignored. Then, the associated equation for  $R_{SFCL}$  can be expressed by (1) to describe its unique characteristic [9].

$$R_m = \sum (R_{ns} / / R_{nc,max})$$

$$R_{SFCL}(t) = R_m (1 - \exp(-t / T_{sc}))$$

(1)

where  $R_m$  is the maximum resistance of the series connected resistive type SFCL in the quenching state, and  $T_{sc}$  is the time constant of transition from the superconducting state to the normal state, which is assumed to be 10 ms.

## 2.3 DC circuit breaker

In current, the IGBT is the most common switching device for the voltage source converter. That is, the reliability and durability of the IGBT have been being verified continuously by the numerous converters that are installed in real power system. Considering the roles of the circuit breaker and the converter, the IGBTs in the circuit

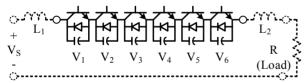

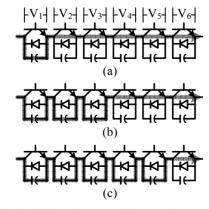

breaker operate sporadically comparing to the frequently operating IGBTs in the converter. Therefore, the IGBT is reliable and durable enough to be used for the circuit breaker role. There are many types of a topology for the DC circuit breaker using IGBTs [12-15]. In this study, the DC circuit breaker is designed with several high-voltage IGBTs, high-voltage diodes, and capacitors as shown in Fig. 4.

According to the high-voltage IGBT and diode module characteristics [16, 17], the maximum withstanding voltage is 6.5 kV. That is, the circuit breaker shown in Fig. 4 can withstand 39 kV if every capacitor is evenly charged.

In practice, however, the capacitors are not uniformly charged due to the physical differences among the capacitors or among the IGBTs. The circuit breaker operation is illustrated in Fig. 5 to consider the voltage unbalance that results from the physical differences of the IGBTs. In other words, the IGBTs are not open at the same time. Assume that the capacitors begin being charged in numerical order from  $V_1$  to  $V_6$ . Then,  $V_1$  becomes the highest voltage and dominantly affects the withstanding voltage of the circuit breaker. As the result, the circuit breaker withstanding voltage becomes lower than the arithmetic sum of the withstanding voltages of the IGBTs.

The circuit breaker can be damaged by the high voltage spike caused by the fast IGBT switching operation and the large line inductance. According to [16, 17], the highvoltage IGBT has 2 kHz of maximum PWM frequency. In other words, the switching period including the rising, falling, and dead times is only 500 microseconds. That is, the IGBT requires less than 250 microseconds (=half period) to separate the feeder. In the DC circuit breaker

Fig. 4. DC circuit breaker in simplified DC feeder

Fig. 5. DC circuit breaker operations and current flows: (a) during V<sub>1</sub> charging, (b) during V<sub>1</sub>-V<sub>3</sub> charging, and (c) during V<sub>1</sub>-V<sub>5</sub> charging

application, the fast switching time can cause serious electrical stress on the IGBT due to the line inductance. Assume that a fault is occurred between L<sub>2</sub> and R in Fig. 4 and the DC circuit breaker is composed without the capacitors. Then, the voltage across the circuit breaker, V<sub>CB</sub>  $(=V_1+V_2+V_3+V_4+V_5+V_6)$  is derived by (2) during the opening operation. Also, di is negative because the fault current is decreased.

$$V_{CB} = V_S - (L_1 + L_2) \frac{di}{dt}$$

(2)

where  $L_1$ ,  $L_2$ , and  $V_S$  are fixed and thus small di or large dtis required for small  $V_{CB}$ . Although the dt can be increased by using parallel capacitor, the capacitor size is limited considering the cost and the numerous circuit breakers in power system. Therefore, the di is also required to be decreased, and it can be effectively decreased if the fault current is reduced. As described in the previous section, the resistive type SFCL can reduce the fault current to the normal level. Therefore, V<sub>CB</sub> is determined by (3) in the resistive type SFCL applied system.

$$V_{CB} \cong V_{S} - (L_1 + L_2) \frac{(0 - I_{normal})}{t_{open}} = V_{S} + \frac{(L_1 + L_2)}{R_{SFCL}} \frac{V_{S}}{t_{open}}$$

(3)

where  $t_{\text{open}}$  is the circuit breaker opening time.

#### 3. Case Studies

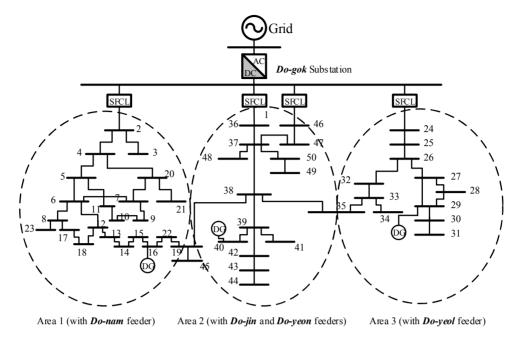

To investigate the resistive type SFCL effects, a practical DC distribution system is implemented by benchmarking the real distribution system in Do-gok area, Seoul Korea as shown in Fig. 6. The DG locations and sizes are optimally selected corresponding to the results of the previous studies [18, 19]. To simulate the most severe and realistic condition, the DGs are set as constant current sources. That is, the DGs are continuously supplying their maximum current regardless of the fault conditions. Also, four resistive type SFCLs are applied together with the maximum impedance of 380  $\Omega$  in the quenching state to investigate the resistive SFCL effects and the critical current is 1 kA. The circuit breaker is operated 20 ms later after a fault.

### 3.1 In case of fault near substation

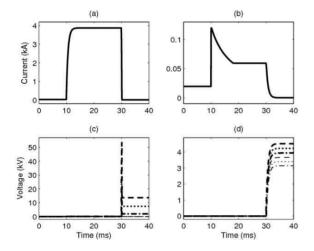

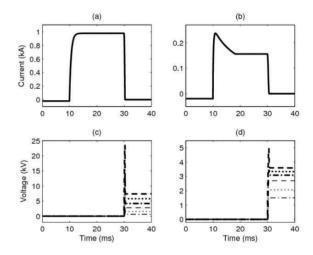

To analyze the SFCL effects on the fault near the substation, the ground fault is simulated with 0.01  $\Omega$  at the center of the line between buses 1 and 36. It is described in Fig. 7(a) that the fault current through the circuit breaker on bus 1 increases up to 3.88 kA without the SFCLs. In contrast, the maximum fault current is about 0.12 kA with the SFCLs as shown in Fig. 7(b). The large fault current causes voltage surge up to 54 kV as shown in Fig. 7(c) and

Fig. 6. Practical DC distribution system benchmarking real distribution system in Do-gok area, Seoul Korea

**Fig. 7.** Currents through circuit breaker on bus 1: (a) without SFCLs, (b) with SFCLs, and voltages across internal IGBTs (c) without SFCLs, (d) with SFCLs

It is described in Fig. 8(a) that the fault current through the circuit breaker on bus 36 increases up to 1 kA without the SFCLs. In contrast, the maximum fault current is about 0.24 kA with the SFCLs as shown in Fig. 8(b). The large fault current causes voltage surge up to 24 kV as shown in Fig. 8(c) and severely damages the IGBTs. The voltage surge is reduced to about 5 kV by the SFCLs as shown in Fig. 8(d).

#### 3.2 In case of fault at center of feeder

To see the SFCL effects on the fault at the center of the

**Fig. 8.** Currents through circuit breaker on bus 36: (a) without SFCLs, (b) with SFCLs, and voltages across internal IGBTs (c) without SFCLs, (d) with SFCLs

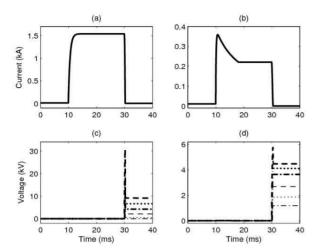

feeder, the fault is simulated at the center of the line between buses 38 and 39. As shown in Fig. 9(a), the fault current through the circuit breaker on bus 38 increases up to 1.6 kA without the SFCLs. In contrast, the maximum fault current is about 0.36 kA with the SFCLs as shown in Fig. 9(b). The large fault current causes the voltage surge up to 31 kV as shown in Fig. 9(c) and severely damages the IGBTs. The voltage surge is reduced to less than 6 kV by the SFCLs as shown in Fig. 9(d).

During normal operation, a current of 11 A flows from the bus 38 to the bus 39. That is, the sum of the loads on buses 39-44 is larger than the DG generation. In the fault condition, the current direction is changed and the fault current through the circuit breaker on bus 39 comes only

Fig. 9. Currents through circuit breaker on bus 38 (a) without SFCLs, (b) with SFCLs, and voltages across internal IGBTs (c) without SFCLs, (d) with **SFCLs**

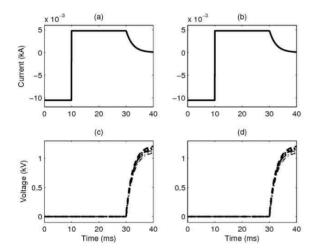

Fig. 10. Currents through circuit breaker on bus 39: (a) without SFCLs, (b) with SFCLs, and voltages across internal IGBTs (c) without SFCLs, (d) with **SFCLs**

from the DG on bus 40. The fault current is only 4.8 A because it is limited by the current rating of the DG and the load consumptions on buses 39-44. The SFCLs hardly affect the circuit breaker on bus 39 because that breaker does not inherently suffer from the voltage surge as shown in Fig. 10.

#### 3.3 In case of fault at end of feeder

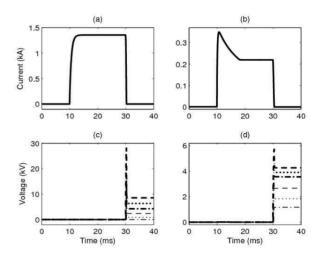

To see the SFCL effects on the fault at the end of the feeder, a fault is simulated at the bus 44. As shown in Fig. 11(a), the fault current through the circuit breaker on bus 44 increases up to 1.4 kA without the SFCLs. In contrast, the maximum fault current is about 0.35 kA with the SFCLs as shown in Fig. 11(b). The large fault current

Fig. 11. Currents through circuit breaker on bus 44: (a) without SFCLs, (b) with SFCLs, and voltages across internal IGBTs (c) without SFCLs, (d) with **SFCLs**

causes the voltage surge up to 28 kV as shown in Fig. 11(c) and severely damages the IGBTs. The voltage surge is reduced by the SFCLs to less than 6 kV as shown in Fig. 11(d).

#### 4. Conclusion

This study investigates the SFCL effects on the DC circuit breakers in the practical power system. The voltage surges across the DC circuit breakers are effectively reduced by a set of SFCLs near the substation. This study demonstrates the DC circuit breaker can be implemented using the IGBT instead of the mechanical device. These results are expected to contribute to the researches on the efficient DC power systems.

## Acknowledgement

This work was supported in part by the Power Generation & Electricity Delivery Core Technology Program (No. 20171220100330) and in part by the Human Resources Development program (No. 20174030201540) of the Korea Institute of Energy Technology Evaluation and Planning (KETEP) granted financial resources from the Ministry of Trade, Industry & Energy, Republic of Korea.

#### References

[1] D. Salomonsson and A. Sannino, "Low-Voltage DC Distribution System for Commercial Power Systems with Sensitive Electronic Loads," IEEE Trans. on

- Power Delivery, vol. 22, no. 3, pp. 1620-1627, Jul. 2007

- [2] A. Sannino, G. Postiglione, and M. H. J. Bollen, "Feasibility of a DC network for commercial facilities," *IEEE Trans. on Industry Applications*, vol. 39, no. 5, pp. 1499-1507, Sep. 2003.

- [3] H. Kakigano, Y. Miura, and T. Ise, "Low-Voltage Bipolar-Type DC Microgrid for Super High Quality Distribution," *IEEE Trans. on Power Electronics*, vol. 25, no. 12, pp. 3066-3075, Dec. 2010.

- [4] Y. Morishita, T. Ishikawa, I. Yamaguchi, S. Okabe, G. Ueta, and S. Yanabu, "Applications of DC Breakers and Concepts for Superconducting Fault-Current Limiter for a DC Distribution Network," *IEEE Trans. on Applied Superconductivity*, vol. 19, no. 4, Aug. 2009.

- [5] L. Varnado, M. Sheehan, Connecting to the Grid, A Guide to Distributed Generation Interconnection Issues, 6th ed., Interstate Renewable Energy Council (IREC) Connecting to the Grid Project, p. 27, 2009.

- [6] G. S. Seo, J. Baek, K. Choi, H. Bae, and B. Cho, "Modeling and Analysis of DC Distribution Systems," in proc. of IEEE 8th International Conference on Power Electronics and ECCE Asia, pp. 223-227, May 2011.

- [7] H. S. Ruiz, X. Zhang and T. A. Coombs, "Resistive-Type Superconducting Fault Current Limiters: Concepts, Materials, and Numerical Modeling," *IEEE Trans. on Applied Superconductivity*, vol. 25, no. 3, Jun. 2015.

- [8] D. Sharma and K. B. Sahay, "Basic concepts of superconducting fault current," *IEEE International* Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), no. 16673229, Jul. 2016.

- [9] W. J. Park, B. C. Sung, K. B. Song, and J. W. Park, "Parameter Optimization of SFCL With Wind-Turbine Generation System Based on Its Protective Coordination," *IEEE Trans. on Applied Superconductivity*, vol. 21, no. 3, Jun. 2011.

- [10] O. B. Hyun, S. D. Cha, H. R. Kim, H. S. Choi, and S. D. Hwang, "Shunt-Assisted Simultaneous Quenches in Series-Connected Resistive SFCL Components," *IEEE Trans. Ind. Electron.*, vol. 13, no. 2, pp. 2060-2063, Jun. 2003.

- [11] B. C. Sung, D. K. Park, J. W. Park, and T. K. Ko, "Study on a Series Resistive SFCL to Improve Power System Transient Stability: Modeling, Simulation, and Experimental Verification," *IEEE Trans. Ind. Electron.*, vol. 56, no. 7, pp. 2412-2419, Jul. 2009.

- [12] A. Mokhberdoran, A. Carvalho, H. Leite, and N. Silva, "A Review on HVDC Circuit Breakers," *in proc. of Renewable Power Generation Conf. (RPG 2014), 3rd*, pp. 1-6, Sep. 2014.

- [13] R. Derakhshanfar, T.U. Jonsson, U. Steiger, and M. Habert, "Hybrid HVDC breaker Technology and

- applications in point-to-point connections and DC grids," in proc. of CIGRE 2014, pp. 1-11, Aug. 2014.

- [14] M. Callavik, A. Blomberg, J. Häfner, and B. Jacobson, "The Hybrid HVDC Breaker An innovation breakthrough enabling reliable HVDC grids," *ABB Grid Systems, Technical Paper*, pp. 1-10, Nov. 2012.

- [15] C. Meyer, M. Kowal, and R. W. De Doncker, "Circuit breaker concepts for future high-power DC-applications," *in Proc. of 40th IEEE IAS Annu.Meet. Conf.*, vol. 2, pp. 860-866, Oct. 2005.

- [16] *High Voltage IGBT Modules (HV-IGBT)*, Mitsubishi Electric Inc., Available: http://www.hy-line.de/fileadmin/hy-line/power/hersteller/mitsubishi/dokumente/HV-Module\_hy.pdf

- [17] HVDC Light<sup>®</sup> It's time to connect, ABB Inc., Available: http://www05.abb.com/global/scot/scot221.nsf/veritydisplay/2742b98db321b5bfc1257b26003e78 35/\$file/Pow0038%20R7%20LR.pdf

- [18] S. H. Lee and J. W. Park, "Selection of Optimal Location and Size of Multiple Distributed Generations by Using Kalman Filter Algorithm," *IEEE Trans. on Power Systems*, vol. 24, no. 3, pp. 1393-1400, Aug. 2009.

- [19] S. H. Lee and J. W. Park, "Optimal Placement and Sizing of Multiple DGs in a Practical Distribution System by Considering Power Loss," *IEEE Trans. on Industry Applications*, vol. 49, no. 5, pp. 2262-2270, Sep. 2013.

**SunHo Bae** received the B.S. degree from the Department of Mechanical and Control Engineering, Handong University, Pohang, Korea, in 2010. He is currently working toward the Ph.D. degree in a combined M.S. and Ph.D. program at Yonsei University, Seoul, Korea. His research interests include

power control of electric vehicle, hardware implementation of grid-connected inverter with photovoltaic and energy storage devices, and energy management system for optimization of hybrid energy storage systems.

Hongrae Kim received his B.S. and M.S. degrees in electrical engineering from Yonsei University, Seoul, Korea, in 1986 and 1989, respectively. He received his Ph.D. degree in electrical engineering from Texas A&M University, College Station, Texas, U.S.A. in 1995. Currently he is a professor in

the Dept. of Electronic Information Engineering, Soon-chunhyang University, Asan, Korea.

Jung-Wook Park was born in Seoul, Korea. He received the B.S. degree (summa cum laude) from the Department of Electrical Engineering, Yonsei University, Seoul, Korea, in 1999, and the M.S.E.C.E. and Ph.D. degrees from the School of Electrical and Computer Engineering, Georgia Institute of Tech-

nology, Atlanta, USA in 2000 and 2003, respectively. He was a Post-doctoral Research Associate in the Department of Electrical and Computer Engineering, University of Wisconsin, Madison, USA during 2003-2004, and a Senior Research Engineer with LG Electronics Inc., Korea during 2004-2005. He is currently an Associate Professor in the School of Electrical and Electronic Engineering, Yonsei University, Seoul, Korea. He is now leading the National Leading Research Laboratory (NLRL) designated by Korea government to the subject of integrated optimal operation for smart grid. His current research interests are in power system dynamics, renewable energies based distributed generations, power control of electric vehicle, and optimization control algorithms. Prof. Park was the recipient of the Young Scientist Presidential Award in 2013 from the Korean Academy of Science and Technology (KAST), Korea.

Soo Hyoung Lee received the B.S. and Ph.D. degrees of electrical engineering from the School of Electrical and Electronic Engineering, Yonsei University, Seoul, Korea, in 2008 and 2012, respectively. He was a Post-doctoral Research Associate in the School of Electrical and Computer Engineering,

Georgia Institute of Technology, Atlanta, GA, USA during 2012-2014. He is currently a Senior Researcher in the Advanced Power Grid Research Division, Korea Electrotechnology Research Institute (KERI). He was the recipient of the Gold Prize Paper Award from the TMS (Telecommunication, Multimedia, and SOC) Institute of Technology and Second Prize Paper Award from the Yonsei Electric Power Research Center. His research interests are converter based microgrid, optimal coordination of distributed generation systems, converter control for distributed generation systems, and implementation of multi-level converters.