# Design and Fabrication of Test Equipment for mass production of Automatic Test Equipment(ATE)

Dong-Il Kim\*, Kyung-Jin Choi\*\*

## **Abstract**

In this paper, we proposed the test equipment that can perform separate performance tests to mass-produce the Automatic Test Equipment. Until now, the performance test of the ATE has been performed after it has been assembled perfectly. It is possible to perform the performance test only when the external device manufacturing and setting of measurement resources and the internal wiring work have been completed. So we have been studying test equipment that separately tested the switching devices that played a key role in the performance of the ATE. To build the test equipment, we reviewed the circuit card assemblies that make up the switching devices. We designed a test equipment that satisfies the performance test and apply the completed test equipment to the actual production process to analyze whether it was effective in improving the time and workability of the performance test. The test equipment has the advantage that it can be used universally in the mass production process of ATE with the same type of switching device.

▶ Keyword: Switching device, Automatic Test Equipment, Process Improvement

#### I. Introduction

군 야전에서 사용하는 자동시험장비(Automatic Test Equipment, ATE)는 신호공급용 계측자원을 이용하여 시험대 상품에 필요한 신호를 생성 및 공급하고, 시험대상품에서 출력되는 신호를 신호측정용 계측자원에 연결하여 측정 후 시험결과를 판단한다[1][2]. 자동으로 이러한 시험을 수행하려면 신호 종류가 상이한 다수의 시험대상과 ATE 사이에서 적절하게 연결을 제어해주는 기능이 필요하며 ATE에 탑재된 스위칭장치가 이러한 역할을 한다[3][4]. 스위칭장치는 모체기판(MB)를 기준으로 스위칭제어보드(Switching Control Board, SCB), 채널스위칭보드(Channel Switching Board, CSB), 디지털인터페이스보드(Digital Interface Board, DIB), 추가형인터페이스보드(Optional Interface Board, OIB), 전원변환모듈(AC/DC), 송풍팬(FAN)으로 구성된다. 이와 같은 구조의 스위칭장치는 최근 한화시스템에서 개발 또는 양산된 ATE에 공통적으로 적용

되었으며 향후에도 동일하게 적용할 예정이다.

시험대상품(Unit Under Test, UUT)을 시험하기 위해서 ATE는 기본적으로 자체진단 기능을 가지며 내장된 기능에 의한 BIT(Built-In Test)와 입출력 신호의 경로 확인을 통해 정상여부를 판단한다[5]. 자체진단을 수행하기 위한 핵심적인 기능은 대부분 스위칭장치에 탑재되어 있으며, 스위칭장치의 정상여부에 따라 자체진단 시험에 대한 신뢰성에 상당한 영향을 준다.

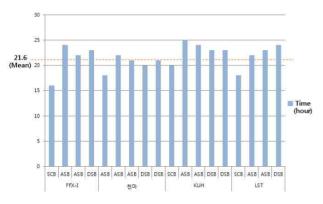

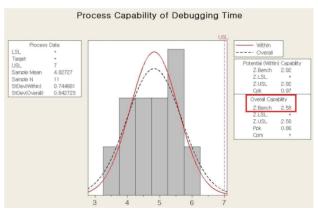

일반적으로 스위칭장치의 정상여부를 확인하기 위해서는 ATE에 탑재된 상태에서 자체진단 시험을 수행하여야 하며 반드시 모든 계측자원이 ATE에 구성되어 있어야하기 때문에 문제 해결을 위한 많은 제약사항이 있다. 이는 스위칭장치 검증에 대한 효율성을 떨어뜨리는 결과를 초래한다. Fig. 1은 양산이 완료된 정비장비 사업에서 스위칭장치를 검증하는데 소요된 시간을 그래프로 나타내었다. ATE본체에서 스위칭장치를 분해

<sup>•</sup> First Author: Dong-Il Kim, Corresponding Author: Kyung-Jin Choi

<sup>\*</sup>Dong-Il Kim (dongil1.kim@hanwha.com), Test Solution Part, Hanwha Systems Company

<sup>\*\*</sup>Kyung-Jin Choi (kj2008.choi@hanwha.com),Test Solution Part, Hanwha Systems Company

<sup>•</sup> Received: 2017. 06. 23, Revised: 2017. 06. 29, Accepted: 2017. 07. 19.

2

및 조립하는데 소요된 시간과 ATE본체를 포함한 고장배제에 소요된 시간이 전체 검증 시간의 상당부분을 차지하였다. ATE 양산 과정에서 별도 시험장비를 통한 스위칭장치의 검증시험은 일반적인 ATE 장착상태에서의 시험에 비해 반복성, 편의성, 시 간적 측면에서 상당한 이점을 제공하기 때문에 필수적이다.

Fig. 1. Debugging time of switching device

본 논문에서는 ATE 핵심 구성품인 스위칭장치를 검증하기 위한 시험장비의 설계 및 제작을 보였다. 스위칭장치를 구성하는 회로카드 조립체의 특징을 바탕으로 시험장비의 구성과 시험방안을 수립하였다. 시험장비를 설계 및 제작한 후, ATE 양산사업에 적용하였으며, 시험결과를 분석하여 시험장비의 효용성을 검증하였다.

#### II. Preliminaries

## 1. Unit Under Test

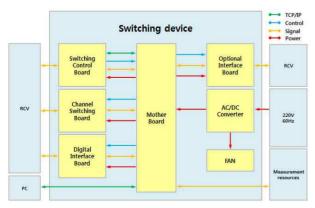

최근 ATE를 개발 또는 양산하는 사업에서 동일하게 적용되는 스위칭장치를 기준으로 시험대상품과 시험방안을 검토하였다. Fig. 2는 스위칭장치를 구성하는 내부 구성을 보여준다. SCB를 통해 전반적인 스위칭장치 제어기능을 수행하고, 각 보드의 외부 신호들은 리시버(RCV)를 통해 시험치구와 적절하게 연결된다.

Fig. 2. Switching device block diagram

스위칭장치의 성능에 영향을 주는 구성품은 SCB, CSB, DIB, OIB 이다. 각 보드는 회로카드 조립체 형태로 스위칭장치의 지정된 슬롯에 장착되어 요구되는 경로를 제공하고 필요로하는 디지털 신호를 생성한다. 대부분의 스위칭장치 불량은 회로카드 조립체에서 발생하며 개별 보드의 성능검증을 통해 문제해결이 가능하다. 따라서 4종(SCB, CSB, DIB, OIB)의 회로카드 조립체에 대한 보드 단위 시험이 가능하도록 시험장비가설계 되어야 한다.

#### 2. Test method of UUT

회로카드 조립체 특성에 따른 시험항목을 Table 1에 나타내었다. SCB는 제어PC로 통신을 통해 직접 제어가 가능하고, CSB, DIB, OIB는 SCB를 통해 제어가 가능한 구조로 되어있다.

Table 1. Test items by circuit card assembly

| Circuit card assembly         | Test items                      |  |

|-------------------------------|---------------------------------|--|

|                               | TCP/IP Test                     |  |

|                               | CPLD Test                       |  |

| Switching Control Board (SCB) | DMM Measure Matrix Test         |  |

| Board (GGB)                   | Relay Control Test              |  |

|                               | Measurement resources Path Test |  |

|                               | Highway Contact Relay Test      |  |

| Channel Switchng Board (CSB)  | Switch channel Short Test       |  |

| Board (OOB)                   | Channel continuity Test         |  |

|                               | FPGA function Test              |  |

| Digital Interface Board (DIB) | Channel Write & Read Test       |  |

| (818)                         | Channel Loopback Test           |  |

| Optional Interface            | Ring signal ON/OFF Test         |  |

| Board (OIB)                   | Termination resistance Test     |  |

SCB는 기본적으로 제어PC를 통해 TCP/IP 통신 상태를 점검하고 정의된 명령에 의해 내부 로직에 대한 자체진단(BIT) 기능을 수행한다. 외부 리시버(RCV)와 연결되는 릴레이와 계측자원 경로는 디지털멀티미터를 이용한 측정값으로 정상여부를 확인한다. CSB는 4개의 Highway와 96개의 채널이 스위치와 릴레이를 통하여 연결 또는 분리되는 구조를 가진다. SCB와연결된 로컬버스 신호를 통해 CSB를 제어하여 4\*96채널의내외부 경로에 대한 디지털멀티미터의 측정값으로 정상여부를확인한다. DIB는 SCB의 제어를 통해 필요한 디지털 신호를 FPGA에 다운로드하는 기능과 방향설정이 가능한 96채널의 디지털 입출력 신호로 설계되어있다. 기본적인 Configuration 파일을 FPGA에 다운로드하여 채널마다 Write 및 Read 기능을

점검하고 외부 리시버(RCV)로 연결되는 경로는 채널간 루 프백을 통해 이상유무를 점검한다. OIB는 SCB의 제어를 통해 전용신호인 링신호를 생성하고 출력한다. 디지털멀티미터로 OIB에서 ON/OFF 하는 링신호 출력값을 측정한다.

제어프로그램을 통해 모든 제어와 측정, 고장유무판단은 자동으

로 이루어지도록 설계하고, 스위칭장치를 구성하는 주요 회로카드 조립체의 성능 시험장비 명을 회로카드 시험기로 정한다.

# III. Test equipment design

본 장에서는 회로카드 시험기의 구성을 결정하고, 회로카드 조립체의 성능 시험을 만족하는 회로카드 시험기 본체, 제어프 로그램에 대한 설계 결과를 기술하다.

#### 1. Hardware structure

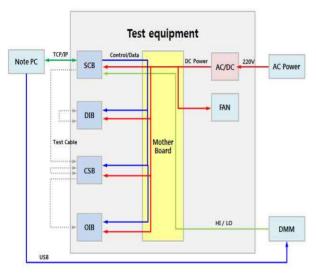

Fig. 3. Circuit card test equipment block diagram

제어프로그램 실행과 TCP/IP통신을 위해 상용 노트북을 선정하였다. 회로카드 조립체의 장착과 안정적인 직류 전원을 공급하고 통신 및 측정 포트를 제공하기 위한 회로카드 시험기본체를 설계하였다. 기존 스위칭장치의 기구적인 부분을 유지하되 불필요한 부분을 제거하고 사용자 편의성을 고려하여 시험이 가능하도록 설계하였다.

Table 2. Required reference circuit card assembly

| Unit under test | Required reference<br>Board | Explanation             |  |

|-----------------|-----------------------------|-------------------------|--|

| SCB             | CSB, DIB                    | External path Test      |  |

| CSB             | SCB                         | Control                 |  |

| DIB             | SCB                         | Control                 |  |

| OIB             | SCB, CSB                    | Control,<br>Output Test |  |

Fig. 4. Functional block diagram of mother board

회로카드 조립체의 정상적인 성능시험을 위해 Table 2와 같이 검증된 기준 회로카드 조립체를 본체에 포함하였다. 회로카드 시험기 본체에 포함된 기준 회로카드 조립체를 통해 시험 대상인 회로카드 조립체는 실제 운용과 동일한 조건에서 동작하여 모든 부분에 대한 성능시험이 가능하게 된다.

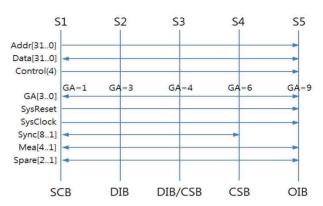

모체기판은 5개의 슬롯으로 구성하였다. 각 슬롯은 GA (Geographical Address) 신호를 통해 구분되고 지정된 회로카드 조립체가 장착된다. 스위칭장치에서 회로카드 조립체가 장착되는 슬롯의 GA신호를 적용하여 ATE 본체에서와 동일한 시험 조건을 갖도록 하였다. 외부 계측자원과 연결되는 모체기판경로에는 저항을 배치하여 측정이 가능하도록 설계하였다.

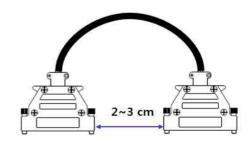

시험케이블은 기본적으로 노트북과 회로카드 시험기 본체간 통신연결과 회로카드 시험기의 전원공급 이외에 ATE본체에서 사용하는 자체진단 치구를 대체하는 역할을 한다. 자체진단 치구는 채널 루프백 시험을 위한 경로 제공, 스위칭장치와 리시버 (RCV)로 이어지는 경로에 대한 측정경로 등을 제공한다. 이러한 자체진단 치구는 시험케이블로 대체 가능하고 루프백 케이블, 회로카드 조립체간 연결 케이블 형태로 설계되었다. 케이블의 피복은 회로카드 조립체 상부에서의 연결 편의성을 고려하여 익스펜더 튜브를 적용하였다. 루프백 케이블은 DIB와 CSB에 공용으로 사용할 수 있도록 설계하였다. Table 3과 같이 DIB와 CSB 전면 커넥터의 신호를 분석하여 하나의 케이블로루프백 시험이 가능하도록 하였다.

외부 입출력 신호를 측정하는 디지털멀티미터는 휴대 및 이 동성을 고려해서 USB타입으로 전원 입력과 제어가 가능한 계 측기로 선정하였다. 회로카드 조립체에 펌웨어를 다운로딩하고

Fig. 5. Loopback test cable

Table 3. Pin map comparing DIB and CSB

| P1  | DIB   | CSB   | P2  | DIB   | CSB   |

|-----|-------|-------|-----|-------|-------|

| 1   | UCH1  | UCH32 | 1   | UCH49 | UCH65 |

| 2   | UCH2  | UCH30 | 2   | UCH50 | UCH67 |

| 3   | UCH3  | UCH29 | 3   | UCH51 | UCH68 |

| 4   | UCH4  | UCH27 | 4   | UCH52 | UCH70 |

| 5   | UCH5  | UCH25 | 5   | UCH53 | UCH71 |

| 6   | UCH6  | UCH48 | 6   | UCH54 | UCH88 |

| 7   | UCH7  | UCH47 | 7   | UCH55 | UCH87 |

| 8   | UCH8  | UCH46 | 8   | UCH56 | UCH86 |

| 9   | UCH9  | UCH45 | 9   | UCH57 | UCH85 |

| 10  | UCH10 | UCH44 | 10  | UCH58 | UCH84 |

| 11  | UCH11 | UCH43 | 11  | UCH59 | UCH83 |

| 12  | UCH12 | UCH42 | 12  | UCH60 | UCH82 |

| 13  | UCH13 | UCH41 | 13  | UCH61 | UCH81 |

| 14  | UCH14 | UCH9  | 14  | UCH62 | UCH49 |

| 15  | UCH15 | UCH10 | 15  | UCH63 | UCH50 |

| 16  | UCH16 | UCH11 | 16  | UCH64 | UCH51 |

| 17  | UCH17 | UCH12 | 17  | UCH65 | UCH52 |

| 18  | UCH18 | UCH13 | 18  | UCH66 | UCH53 |

| 19  | UCH19 | UCH14 | 19  | UCH67 | UCH54 |

| 20  | UCH20 | UCH15 | 20  | UCH68 | UCH55 |

| 21  | UCH21 | UCH16 | 21  | UCH69 | UCH56 |

| 43  | UCH22 | UCH31 | 43  | UCH70 | UCH66 |

| 45  | UCH23 | UCH28 | 45  | UCH71 | UCH69 |

| 47  | UCH24 | UCH26 | 47  | UCH72 | UCH72 |

| 57  | UCH45 | UCH21 | 57  | UCH93 | UCH76 |

| 59  | UCH46 | UCH22 | 59  | UCH94 | UCH75 |

| 61  | UCH47 | UCH23 | 61  | UCH95 | UCH74 |

| 63  | UCH48 | UCH24 | 63  | UCH96 | UCH73 |

| 85  | UCH25 | UCH40 | 85  | UCH73 | UCH96 |

| 86  | UCH26 | UCH39 | 86  | UCH74 | UCH95 |

| 87  | UCH27 | UCH38 | 87  | UCH75 | UCH94 |

| 88  | UCH28 | UCH37 | 88  | UCH76 | UCH93 |

| 89  | UCH29 | UCH36 | 89  | UCH77 | UCH92 |

| 90  | UCH30 | UCH35 | 90  | UCH78 | UCH91 |

| 91  | UCH31 | UCH34 | 91  | UCH79 | UCH90 |

| 92  | UCH32 | UCH33 | 92  | UCH80 | UCH89 |

| 93  | UCH33 | UCH17 | 93  | UCH81 | UCH80 |

| 94  | UCH34 | UCH18 | 94  | UCH82 | UCH79 |

| 95  | UCH35 | UCH19 | 95  | UCH83 | UCH78 |

| 96  | UCH36 | UCH20 | 96  | UCH84 | UCH77 |

| 97  | UCH37 | UCH1  | 97  | UCH85 | UCH57 |

| 98  | UCH38 | UCH2  | 98  | UCH86 | UCH58 |

| 99  | UCH39 | UCH3  | 99  | UCH87 | UCH59 |

| 100 | UCH40 | UCH4  | 100 | UCH88 | UCH60 |

| 101 | UCH41 | UCH5  | 101 | UCH89 | UCH61 |

| 102 | UCH42 | UCH6  | 102 | UCH90 | UCH62 |

| 103 | UCH43 | UCH7  | 103 | UCH91 | UCH63 |

| 104 | UCH44 | UCH8  | 104 | UCH92 | UCH64 |

보다 정밀한 측정을 위해 VME확장카드를 구성하여 회로카드 조립체의 부품 단위 고장배제도 가능하도록 하였다.

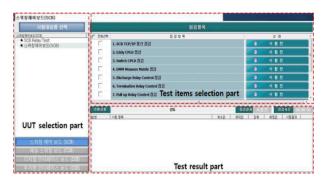

## 2. Control program design

제어 프로그램은 회로카드 시험기의 제어, 시험 수행, 시험

결과 확인을 위한 프로그램으로서 시험대상품 선택부, 점검항목 선택부, 시험결과부의 3구역으로 구분하였다. 시험대상품 선택부는 트리 형태의 목록에서 회로카드 조립체를 선택하고 현재 선택된 시험대상품을 표시하는 역할을 한다. 점검항목 선택부는 시험대상품 선택에 따른 점검항목을 나열하고, 전체 또는 개별 선택이 가능하도록 구현하였으며 항목별 시험결과를 한눈에 알 수 있도록 상태를 표시하였다. 시험 결과부는 시험항목에 대한 세부 시험항목과 측정결과에 따른 시험결과 확인이가능하도록 하였다.

Fig. 6. Control program

본 제어 프로그램은 회로카드 조립체의 전반적인 성능시험 이외에도 고장 빈도가 상대적으로 높은 릴레이에 대한 부품단위 시험이가능하도록 설계하였다. 기본적인 회로카드 조립체 단위 성능시험에서 릴레이와 관련된 불량이 발생한 경우 해당 릴레이에 대한 정보와 측정치를 팝업창을 통해 화면에 전시한다. 팝업된 정보를참고하여 회로카드 조립체를 VME확장카드에 장착 후 제어 프로그램을 통해 릴레이를 ON/OFF 동작시킨다. 디지털멀티미터로 릴레이 동작에 따른 접점 저항값을 측정하여 불량이 의심되는 릴레이에 대한 직접적인 시험이 가능하도록 하였다.

# 3. Implementation

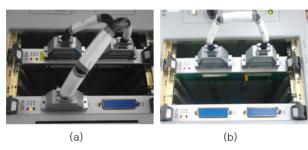

Fig. 7. External shape of Test equipment

설계 및 제작 완료된 회로카드 시험기의 형상은 Fig. 7과 같다. 회로카드 조립체를 상부에서 장착하는 슬롯 형태의 타입을 적용하고 LAN포트와 DMM포트를 모체기판과의 연결이 용이

하도록 하부에 배치하였다. 흡기구를 통해 회로카드 시험기 본 체 내부의 공기가 순환될 수 있도록 하였다. 상부 보호 및 오염 방지를 위해 상부 덮개를 적용하였다. 모체기판을 통해 회로카 드 조립체로 공급되는 5V, 12V, 15V, 48V DC전원의 상태 확 인을 위해 회로카드 시험기 본체 상부에 LED를 배치하였다.

기존 자체진단 치구를 대체하기 위한 시험케이블이 제작되 었고 연결 구성은 Fig. 8과 같다. Fig. 8의 (a)는 SCB에 포함되 어 있는 릴레이 동작 시험을 위한 시험케이블 구성이며 Fig. 8 의 (b)는 외부 리시버(RCV)로 연결되는 경로에 대한 루프백 시 험의 연결 구성이다. ATE본체에 장착된 상태에서 수행하는 자 체진단 시험과 동일한 수준의 성능 시험이 가능하였고, 시험 대 상인 회로카드 조립체 4종에 대해 Table 1에서 제시한 성능 시 험 항목을 모두 만족하는 결과를 확인할 수 있었다.

Fig. 8. (a) Relay Control Test (b) Loopback Test

회로카드 조립체를 구성하는 릴레이에 대한 부품 단위 시험 은 Fig. 9와 같이 직접적인 측정이 가능하다. 제어 프로그램의 시험 결과에 릴레이 동작 시험에 대한 불량이 발생하면 해당 릴레이의 번호와 측정 위치, 측정값이 자동으로 팝업 전시된다. 해당 회로카드 조립체를 VME 확장카드에 장착하고 제어 프로 그램에 불량 릴레이 정보를 입력하면 릴레이의 ON/OFF 동작 에 따라 디지털멀티미터를 활용한 직접적인 측정이 가능하다. 이와 같은 시험은 최초 제작된 회로카드 조립체의 납땜 불량 또는 소자 자체의 불량에 대한 고장배제를 가능하게 하며 회로 카드 조립체의 검증 시간을 단축시키는데 기여한다.

Fig. 9. Relay control test on VME expansion card

회로카드 시험기의 보관 및 이동 편의성을 확보하기 위해 Fig. 10과 같이 견고화 케이스를 적용하였다. 각 구성품의 크기 에 맞게 내부 폼을 설계하여 보관을 용이하게 하였다. 견고화 케이스 외부에 장착된 바퀴는 이동시 캐리어와 같은 타입으로 이동이 가능하여 회로카드 시험기에 대한 무게의 부담을 줄여 주는 역할을 한다.

Fig. 10. Rugged case for Test equipment

# IV. Results analysis

본 장에서는 회로카드 시험기를 ATE 제작 공정간 활용하여 스위칭장치에 장착되는 회로카드 조립체의 디버깅 시간을 측정 하고, 린6시그마 기법을 통해 회로카드 조립체들이 정해진 기 간 내에 검증이 완료되는 공정능력을 기존 사업과 비교 분석하 였다. 공정능력 분석을 통해 현재의 프로세스가 성과 기준을 얼 마나 만족하고 있는지 확인할 수 있다[6].

Table 4. Debugging time of Existing processes

| Project | UUT    | Debugging time<br>(hour) |

|---------|--------|--------------------------|

|         | SCB    | 16                       |

| FFX-I   | CSB #1 | 24                       |

| 1171    | CSB #2 | 22                       |

|         | DIB    | 23                       |

|         | CSB #1 | 18                       |

|         | CSB #2 | 22                       |

| 천마      | CSB #3 | 21                       |

|         | DIB #1 | 20                       |

|         | DIB #2 | 21                       |

| KUH     | SCB    | 20                       |

|         | CSB #1 | 25                       |

|         | CSB #2 | 24                       |

|         | DIB #1 | 23                       |

|         | DIB #2 | 23                       |

| LOT     | SCB    | 18                       |

|         | CSB #1 | 22                       |

| LST     | CSB #2 | 23                       |

|         | DIB    | 24                       |

| Table 5. Debugging time of Improved process |

|---------------------------------------------|

|---------------------------------------------|

| Project | UUT    | Debugging time<br>(hour) |

|---------|--------|--------------------------|

| TICN    | SCB #1 | 5.6                      |

|         | SCB #2 | 5.7                      |

|         | SCB #3 | 3.9                      |

|         | CSB #1 | 3.5                      |

|         | CSB #2 | 4.5                      |

|         | CSB #3 | 3.9                      |

|         | CSB #4 | 6.0                      |

|         | DIB #1 | 5.5                      |

|         | DIB #2 | 4.4                      |

|         | DIB #3 | 4.9                      |

|         | DIB #4 | 5.2                      |

기존 사업별로 규격화된 점검 프로그램이 있으며 저장된 자체진단 시험 이력을 확인하면 ATE에 탑재된 스위칭장치의 회로카드 조립체를 성능 검증하는데 걸린 시간을 확인 할 수 있다. 실제 장비 운용 시 저장되는 시험 이력이므로 조작이 어려워 측정 데이터로 신뢰성이 있다. 기존 사업에서 소요된 디버깅시간은 Table 4와 같이 정리할 수 있다.

회로카드 시험기를 2016년부터 양산되는 프로젝트의 ATE 양산 공정에 적용하여 스위칭장치를 구성하는 회로카드 조립체의 성능 검증을 완료하는데 소요되는 시간을 측정하였다. 측정방법은 회로카드 시험기의 점검 프로그램에서 저장되는 시험이력을 통해 회로카드 조립체를 정상 확인하는데 소요되는 시간을 확인하였고 Table 5와 같은 결과가 나타났다.

회로카드 조립체의 적기 검증 완료율을 구하는 식은 다음과 같다.

$$Y = e^{-DPU} = e^{-\frac{Defects}{Unit}}$$

(1)

여기서, Y는 하나의 제품이 합격할 확률(Yield) 값으로 회로카드 조립체를 목표로 하는 기간 내에 검증 완료하는 비율로 정의한다. DPU(Defects per Unit) 는 단위 당 발견된 결함 수를 의미한다[7]. Unit 은 총 제작되는 회로카드 조립체 수량을 적용하고 Defects 는 평균 디버깅 시간을 초과하는 회로카드 조립체 수량을 적용하였다. 회로카드 시험기가 적용된 공정의

Table 6. Test results for each process

| Variables         | Existing processes | Improved processes |

|-------------------|--------------------|--------------------|

| Target time(hour) | 22                 | 7                  |

| Unit              | 18                 | 11                 |

| Defects           | 11                 | 0                  |

시험 결과는 Table 6과 같이 나타났다. 기존 공정보다 짧은 목표 검증 기간임에도 불구하고 모든 회로카드 조립체를 적기 에 검증 완료할 수 있었다.

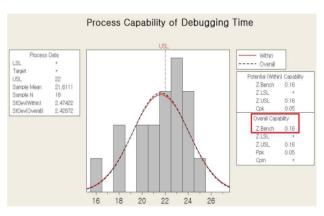

적기 검증 완료율 Y는 통계 분석 프로그램인 Minitab을 이용하여 장기 공정능력  $Z_{LT}(Z_{Bench})$ 으로 산출된다[8]. 프로

세스의 공정능력 $Z_{ST}$ 는 일반적으로 우리가 취하는 모든 Data 를 장기 Data로 가정하고 장기 공정능력 $Z_{LT}$ 와 공정의 장기 변동인  $Z_{shift}(1.5\sigma)$ 를 고려하여 아래와 같이 산출할 수 있다.

$$Z_{ST} = Z_{LT} + Z_{shift} \tag{2}$$

Fig. 11은 ATE본체에서 회로카드 조립체를 검증했던 기존 사업의 공정에 대한 공정능력 분석을 나타내고, Fig. 12는 회로 카드 시험기를 적용하여 진행된 사업에 대한 공정능력 분석을 나타낸다. 두 분석 결과를 비교하면 Table 7과 같이 나타낼 수

Fig. 11. Process capability analysis of existing processes

Fig. 12. Process capability analysis of improved processes

Table 7. Comparative analysis of process capability

| Processes          | $Z_{LT}$ | $Z_{ST}$ |

|--------------------|----------|----------|

| Existing processes | 0.16σ    | 1.66σ    |

| Improved processes | 2.58σ    | 4.08σ    |

|                    |          |          |

있으며,  $Z_{ST}$ 를 비교해보면 회로카드 시험기가 적용된 사업의 공정에서 상당히 개선된 공정능력 산출 결과를 보이는 것을 확인할 수 있다.

# V. Conclusions

자동시험장비의 핵심 구성품인 스위칭장치의 성능 검증을 위한 회로카드 시험기를 설계하고 제작하였다. 실제 양산 공정에 회로카드 시험기를 적용하여 스위칭장치를 구성하는 회로카드 조립체를 성능 검증하는데 소요되는 시간과 작업의 편의성을 개선하는데 기여를 하였다. 이것은 자동시험장비를 제작하는 전체 공정을 개선하는데 상당한 영향을 주었다. 개선된 공정에서 측정된 시험 결과를 토대로 린6시그마 기법에 의한 공정능력 분석을 수행하여 회로카드 시험기의 효용성을 입증하였다.

회로카드 시험기는 동일한 타입의 스위칭장치가 적용되는 모든 ATE의 양산 공정에서 범용으로 활용할 수 있는 장점이 있다. 또한 견고화케이스를 통해 보관 및 이동편의성이 확보되 어 있기 때문에 양산 공정뿐만 아니라 향후 야전에서 운용되는 ATE의 스위칭장치와 관련된 불량 발생 시 이동 정비가 가능하 다. 스위칭장치를 구성하는 회로카드 조립체에 대한 성능 시험 을 현장에서 수행함으로써 신속한 이동 정비를 지원하는데 중 요한 역할을 할 수 있다.

## **REFERENCES**

- [1] W. K. Kim, "Design and Implementation of the multi-function switching system for Automatic Test Equipment(ATE)," Journal of the Graduate School of Industry Kumoh National Institute of Technology, Dec. 2012.

- [2] Y. H. Yoon, K. U. Ku, J. J. Keum, U. H. Hwang, and S. Woo, "The Study on Improvement of ATE Reliability in Production Phase," The Institute of Electronics Engineers of Korea System and Control, Vol. 47, No. 6, pp. 19~26, Nov. 2010.

- [3] K. J. Choi, "The Study on The Production Testing Equipment for the Improvement of System Test Reliability in FCS," Journal of the Institute of Electronics and Information Engineers, Vol. 53, No. 11, pp. 139~147, Nov. 2016.

- [4] D. J. Kim, "Real-Time System Parallel Testing Techniques for Weapon System Error Verification," Journal of the Institute of Electronics and Information Engineers, Vol. 53, No. 11, pp. 130~138, Nov. 2016.

- [5] S. M. Lee, and Y. K. Kim, "The Study of PCB tester for improving productivity," Journal of Korea Institute of Information and Communication Engineering, Vol. 16, No. 12, pp. 2808–2814, Dec. 2012.

- [6] Y. K. Yang, S. I. Oh, K. S. Kang, "The study on the Process Capability Index for Continuously Improvement Quality

- Safety," Journal of the Korea Safety Management & Science, Vol. 8, No. 3, pp. 11-25, Jun. 2006.

- [7] J. G. Kim, I. H. Kim, H. M. Kim, "On the Six-sigma Approach in Dependability Management System IEC60300," Proceedings of the Safety Management and Science Conference, pp. 639-649, Nov. 2010.

- [8] S. H. Hong, H. M. Gwon, M. K. Lee, and S. B. Kim, "Basic Statistics and MINITAB Usage for Six Sigma," KOREAN STANDARDS ASSOCIATION, Mar. 2012.

#### Authors

Dong Il Kim received the B.S. degrees in Electrical and Electronic Engineering from Ulsan University, Korea, in 2010. Mr. Kim joined the Test Solution Part of Hanwha Systems, Korea, in 2010. He is currently a Engineer in the ILS

Research Center, Hanwha Systems. He is interested in Embedded Systems of Test Equipment.

Kyung Jin Choi received the B.S. degrees in Electronics Engineering from Yeungnam University, Korea, in 2009. Mr. Choi joined the Test Solution Part of Hanwha Systems, Korea, in 2009. He is currently a Senior Engineer in the

ILS Research Center, Hanwha Systems. He is interested in Embedded Systems of Test Equipment.