https://doi.org/10.6113/TKPE.2018.23.6.397

# 보조 회로를 활용한 ZCZVT 소프트 스위칭 플라이백 컨버터

주현승<sup>1</sup>, 최현칠<sup>†</sup>

### A Zero-Current-Zero-Voltage-Transition Flyback Converter using Auxiliary Circuit

Hyeon-Seung Ju<sup>1</sup> and Hyun-Chil Choi<sup>†</sup>

#### Abstract

In this study, a high-efficiency flyback converter that uses a soft-switching auxiliary circuit is proposed. The structure of the proposed converter adds an inductor, switch, diode, and capacitor to the conventional flyback converter. The switch in the auxiliary circuit and the main switch are turned on and off under soft-switching conditions. Therefore, the switching losses of the proposed flyback converter are considerably smaller than those of conventional flyback converters. The performance of the proposed flyback converter is validated by experiments on a 100 W single-output flyback converter prototype, and design guidelines are presented.

**Key words:** ZCT(Zero-Current-Transition), ZCZVT(Zero-Current-Zero-Voltage-Transition), Soft-switching, Flyback converter

#### 1. 서 론

최근 통신용, 산업용 및 가전기기 등에 대하여 효율이 높고 내구성이 강하며 소형화에 용이한 SMPS (Switched Mode Power Supply)가 고효율화 및 소형, 경령화, 노이즈 저감 등에 대하여 계속해서 발전하고 있다. 그 중에서 플라이백 컨버터는 산업용과 가정용으로 가장 많이 이용되는 절전형 SMPS이다. 플라이백 컨버터는 적은 수의 소자의 필요, 간단한 제어방식 또한 다출력 구성이 용이한 점이 있다.

플라이백 컨버터의 높은 전력 밀도를 위하여 고주파로 동작하는 것이 바람직 하지만 기존의 하드 스위칭 방식으로는 스위칭 손실로 인하여 컨버터의 효율을 떨어뜨릴 수 있다. 스위칭 손실을 줄이기 위한 방안으로 LLC 공진형 컨버터가 있다. 이 컨버터는 우수한 전력 변환 효율과 2차측 정류기의 낮은 전압 스트레스가 장점이다. 또 하나의 방식으로 공진 스위치를 펄스폭 변조 (PWM) 방식 컨버터에 삽입한 준-공진(Quasi-Resonant)

Fig. 1. Circuit of proposed ZCZVT flyback converter.

컨버터가 있다. 위의 방식들은 고주파 스위칭 시의 높은 스위칭 손실을 위한 방안이지만 소프트 스위칭을 유지 하기 위한 큰 순환 에너지가 필요 하다는 점 등이 문제 가 된다<sup>[1]-[3]</sup>.

최근에 연구되고 있는 천이형(Transition) 컨버터의 경우 위와 같은 문제점을 해결하고 있다. 컨버터의 동작은 유사 하지만 스위칭 전의 짧은 주기에 공진을 발생시켜 소프트 스위칭을 이루어지도록 하고 있다. 위와 같은 방식은 영전류 천이형(ZCT), 영전압 천이형(ZVT) 그리고 영전류-영전압 천이형(ZCZVT) 방식이 있다. 이들은 스위치나 다이오드의 높은 전압/전류 스트레스를 줄이고 순환 에너지가 적으며 일정한 주파수를 유지할수 있다는 장점이 있다. 천이형 컨버터의 형태는 기존의

Paper number: TKPE-2018-23-6-4

Print ISSN: 1229-2214 Online ISSN: 2288-6281

<sup>†</sup> Corresponding author: elecchc@inje.ac.kr, Dept. of Electronic Engineering Eng., Inje University

Tel: +82-55-320-3552 Fax: +82-55-333-3261

<sup>&</sup>lt;sup>1</sup> Dept. of Electronic & Telecommunication Engineering Eng., Inje University

Manuscript received Jul. 4, 2018; revised Jul. 11, 2018; accepted Jul. 27, 2018

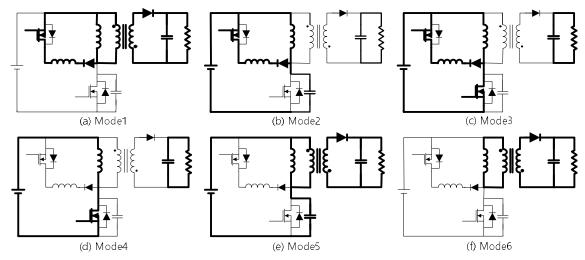

Fig. 2. Operation modes of the proposed flyback converter.

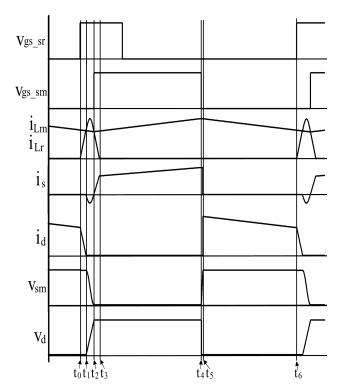

Fig. 3. Theoretical waveforms of proposed flyback converter.

PWM 컨버터에 보조회로를 추가한 형태로써, 보조 회로는 스위치와 수동소자로 이루어 져 있으며 보조회로는 스위치가 켜지는 직전에만 동작하여 주 스위치를 소프 트 스위칭 동작하게 한다<sup>[4]-[10]</sup>.

스위치의 턴-오프 순간에는 하드 스위칭하여 스위칭 손실을 야기하는 경우가 있다. 이 문제를 해결하기 위하여 플라이백 컨버터를 DCM(Discontinuous Current Mode)로 동작하여 턴-오프시 스위칭 손실을 최소화 하는 방법이 있다<sup>[4]</sup>. 하지만 위의 DCM 동작은 자화 인덕터에 흐르는 전류의 최댓값이 같은 부하일 때, CCM (Countinuous Current Mode)보다 훨씬 크다. 이러한 특징

은 트랜스포머가 포화될 수 있는 가능성이 높고, 소자의 정격값(Absolute Maximum Ratings)이 높아진다는 단점이 있다.

이러한 단점을 해결하기 위하여 본 논문에서는 기존의 플라이백 컨버터에 보조 회로를 추가하여 ZCZVT 공진형 플라이백 컨버터를 제안하였다. 위의 정상상태 동작은 CCM이며, 제안한 회로는 보조 회로의 동작이주 스위치의 턴-온, 턴-오프 이전의 짧은 구간에서 동작하여 주 스위치를 소프트 스위칭 하며, 보조 스위치 또한 턴-온, 턴-오프에 모두 소프트 스위칭하여 스위칭 손실과 EMI를 최소화 하였다.

## 2. 제안한 ZCZVT 플라이백 컨버터

### 2.1 제안한 회로의 구성

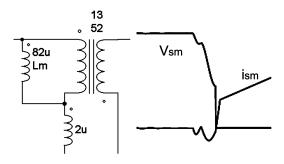

그림 1은 제안된 플라이백 회로도 이다. 회로의 구조 상으로 보아 기존의 플라이백 회로와 유사함을 알 수 있다. 단지 보조 인덕터  $L_r$ , 보조 스위치  $S_r$ , 보조 다이 오드  $D_r$ 이 추가된다는 점이 다르다. 공진 커패시터  $C_s$ 는 주 스위치  $S_m$ 과 병렬로 연결된 커패시터이다.

#### 2.2 동작원리

제안된 회로의 동작은 기존의 플라이백 컨버터와 동일하게 동작한다. 보조 스위치  $S_r$ 이 켜지면 보조 인덕터에 전류가 일정하게 상승하다가 자화 인덕턴스에 흐르는 전류  $i_{Lm}$ 와 같아지는 순간 보조 인덕터와 보조 커패시터가 공진을 시작한다. 이때 주 스위치에 흐르는 전류는 음의 값을 가지며 동시에 주 스위치의 전압이 빠르게 감소한다. 보조 인덕터 전류가 자화 인덕터의 전류보다 커졌다가 같아지는 순간 주 스위치의 전류와 전압이 인이 된다. 이때 주 스위치를 턴-온 시킨다.

주 스위치가 턴-온 되면 기존의 플라이백과 같은 동

작으로 자화 인덕터에 에너지를 저장한다. 또한 보조 인 덕터의 전류는 0으로 일정하게 감소하게 된다. 보조 인 덕터의 전류가 0이 될 때, 보조 스위치를 턴-오프 시킨다.

주 스위치가 턴-오프 순간에는 전류가 바로 주 스위치로 흐르지 않고 보조 커패시터로 흘러서 전압을 천천히 증가시킨다. 위의 동작 원리에 따라 주 스위치와 보조 스위치가 턴-온과 턴-오프 순간에 모두 소프트 스위칭 하므로 스위칭 손실이 최소화 되었다.

#### 2.3 동작모드

제안된 회로의 동작은 하나의 스위칭 동작에 6개의 동작 모드로 나누어진다. 각 동작별 전류의 흐름과 파형 은 각각 그림 2와 그림 3에 나타내었다. 회로의 동작을 파악하기에 앞서 다음과 같은 조건을 가정한다.

- 제안된 회로의 동작은 정상상태 동작이며 CCM (continuous conduction mode)으로 동작한다.

- 모든 스위치와 다이오드는 이상적이며 스위칭 시간 이나 역회복시간은 고려하지 않는다.

- 입력  $V_i$ 과 출력  $V_o$ 는 일정한 값을 가진다.

- 트랜스포머 권선 비는  $n=N_2/N_1$ 으로 나타나며 자화인덕턴스  $L_m$ 을 포함하고, 누설인덕턴스  $L_k$ 을 포함하지 않는다.

- 6개의 모드 중 모드 1, 2, 3에서 트랜스포머의 자화 인덕터에 흐르는 전류는 최소값 근처에 있으므로 같은 전류 크기라고 가정한다.

### 모드 1 $[t_0 \sim t_1]$ : $S_m$ off, $S_r$ on

$t_0$ 이전에는  $S_m$  off,  $S_r$  off이며, 기존의 플라이백 컨버터 동작 중 스위치가 꺼질 때 동작과 같다. 자화 인덕터의 전류  $i_{Lm}$ 은 최소값 $(I_{Lm}-\Delta i_{Lm}/2)$ 에 도달해 있다. 또한 보조스위치에 흐르는 전류는 0이다.

보조스위치가 영 전류 상태에서 켜지면 보조 인덕터 전류  $i_{Lr}$ 가 선형적으로 증가한다.

$$i_{Lr}(t) = \frac{V_o/n}{L_c} t \tag{1}$$

모드 1은 보조 인덕터 전류  $i_{Lr}$ 가 선형적으로 증가하여 자화 인덕터 전류  $i_{Lm}$ 와 같아졌을 때 종료된다. 모드 1의 시간은 다음과 같다.

$$t_1 - t_0 = L_r \frac{I_{Lm} - \Delta i_{Lm}/2}{V_o/n} \tag{2}$$

# 모드 2 $[t_1 \sim t_2]$ : $S_m$ off, $S_r$ on

보조 인덕터 전류  $i_{Lr}$ 가 선형적으로 증가하여 자화 인덕터 전류  $i_{Lm}$  보다 커지기 시작한다. 그리고 보조 인덕터  $L_r$ 과 보조 커패시터  $C_s$ 가 공진을 시작한다.  $i_{Lr}$  전류가  $i_{Lm}$  전류보다 커진 만큼  $C_s$ 로 흐르면서 주 스위치의 전압  $v_{sm}$ 을 감소시킨다. 위의 동작의 식은 다음과 같다.

$$i_{Lr}(t) + C_s \frac{dv_{sm}(t)}{dt} - (I_{Lm} - \Delta i_{Lm}/2) = 0 \qquad (3)$$

$$V_i - v_{sm}(t) + L_r \frac{di_{Lr}(t)}{dt} = 0 \tag{4} \label{eq:4}$$

또한  $v_{sm}(t)$ 와  $i_{Lr}(t)$ 에 관한 식으로 정리하면 다음과 같다

$$v_{sm}(t) = V_i + (V_o/n)\cos w_r t \tag{5}$$

$$\begin{split} i_{Lr}(t) &= \left(I_{Lm} - \Delta i_{Lm}/2\right) + \frac{V_o/n}{Z_r} sin\,w_r(t) \\ w_r &= \sqrt{\frac{1}{L_rC_s}}\;,\;\; Z_r = \sqrt{\frac{L_r}{C_s}} \end{split} \label{eq:ill}$$

전류  $i_{Lr}$ 이  $i_{Lm}$ 이상 상승했다가 다시  $i_{Lm}$ 을 만날 때, 주 스위치의 전류가 0이 된다. 이때 스위치를 켜서 영전류 스위칭이 되도록 한다.

모드 2의 시간은 전류  $i_{Lr}$ 이  $i_{Lm}$ 보다 상승했다가 다시 만나는 지점이므로 다음과 같은 식이 도출된다.

$$t_2 - t_1 = \pi \sqrt{L_r C_s} \tag{7}$$

### 모드 3 $[t_2 \sim t_3]$ : $S_m$ on, $S_r$ on

주 스위치가 영전류 상태에서 on이 되면 스위치의 전 압은 0으로 떨어지고 동시에 보조 스위치에 흐르는 전류는 0으로 선형적으로 감소하게 된다. 보조스위치가 0이 된 이후에 보조 스위치를 끄면 소프트 스위칭이 된다. 보조 인덕터에 흐르는 전류는 다음과 같다.

$$i_{Lr}(t) = (I_{Lm} - \Delta i_{Lm}/2) - \frac{V_i}{L_r}t$$

(8)

위의 식을 통하여 모드 3의 시간을 구하면 다음과 같다.

$$t_3 - t_2 = \frac{L_r}{V_i} (I_{Lm} - \Delta i_{Lm}/2) \tag{9}$$

### 모드 4 $[t_3 \sim t_4]$ : $S_m$ on, $S_r$ off

모드 4는 기존의 플라이백 회로가 스위치가 도통 되었을 때 동작과 같다. 트랜스포머의 1차 측 전압은 입력전압  $V_i$ 가 되고 자화 인덕터 전류  $i_{Lm}$ 은  $I_{Lm}+\Delta i_{Lm}/2$ 까지 증가한다.

### 모드 5 $[t_4 \sim t_5]$ : $S_m$ off, $S_r$ off

주 스위치가 꺼진 직후에 주 스위치에 흐르는 전류는 곧바로 주 스위치를 통과하지 않고 스위치와 병렬로 붙여진 커패시터  $C_s$ 로 먼저 흐르게 된다. 따라서 주 스위치의 전압도 일정하게 상승하게 되어  $V_i + V_o/n$ 까지 도달하게 된다. 따라서 주 스위치는 턴-오프때 소프트 스위칭을 하게 된다.

$$v_{sm}(t) = \frac{I_{Lm} + \Delta i_{Lm}/2}{C_s}t \tag{10}$$

주 스위치의 전압은 0부터  $V_i + V_o/n$ 까지 상승하므로 모드 5의 시간은 다음과 같다.

$$t_5 - t_4 = C_s \frac{V_i + V_o/n}{I_{Lm} + \Delta i_{Lm}/2} \eqno(11)$$

### 모드 6 $[t_5 \sim t_6]$ : $S_m$ off, $S_r$ off

이 구간의 동작은 기존의 플라이백 회로의 스위치가 꺼졌을 때 동작과 같다. 트랜스포머의 자화 인덕터의 에 너지가 출력 측으로 전달된다.

#### 2.4 전 압전달비

제안된 회로의 전압전달비는 voltage second balance 방식으로 유도 할 수 있다. 트랜스포머의 자화인덕턴스 에 대하여 이 방식을 적용하면 다음과 같다.

$$V_i DT = (1-D)\, T \frac{V_o}{n} + \frac{1}{2} (\,V_o/n + V_i) (t_{12} + t_{45}) \eqno(12)$$

위의 식을 다시 정리하면 전압전달 비는 다음과 같이 구해진다.

$$\frac{V_o}{V_i} = n \frac{D - \frac{1}{2} \left( \pi \sqrt{L_r C_s} + C_s \frac{V_i + V_o/n}{I_{Lm} + \Delta i_{Lm}/2} \right)}{1 - D + \frac{1}{2} \left( \pi \sqrt{L_r C_s} + C_s \frac{V_i + V_o/n}{I_{Lm} + \Delta i_{Lm}/2} \right)}$$

(13)

위의 결과로부터 모드 2와 모드 4를 제외하면 기존의 플라이백 컨버터와 전압전달비가 같다는 것을 알 수 있다.

#### 3. 각 소자 값 설계 방법

각 모드의 동작에서 알 수 있듯이 보조 스위치가 동작하는 구간을 제외하고는 나머지 동작은 기존의 플라이백 컨버터와 같다. 그래서 트랜스포머와 출력 커패시터  $C_o$ 의 설계는 기존 방식을 따라하면 된다.

$L_r$ 의 전류는 보조 스위치의 바디 다이오드에 대한  $t_{rr}$  (Reverse Recovery time)으로 결정된다. 또한 보조회로

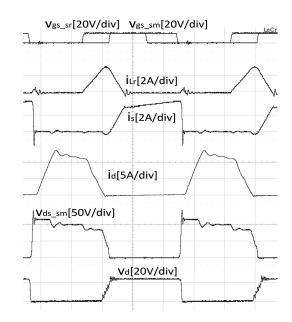

Fig. 4. Experimental result.

Fig. 5. Experimental results of main switch  $S_m$ .

에서의 전도 손실을 최소화하는 것이 설계 요점이다. 본 논문에서는 보조 스위치의 전류가 자화 인덕터 전류와 같아지는 시점(모드 1의 시간)이 바디 다이오드  $t_{rr}$ 의 2배로 설계한다.

$$L_r = \frac{2t_{rr} \cdot V_o/n}{I_{I_m} - \Delta i_{I_m}/2} \approx 8uH \tag{14}$$

$C_s$ 의 설계 방법은 다음과 같다. 모드 2에서  $C_s$ 와  $L_r$ 의 공진으로 인하여 주 스위치가 ZCZVT된다. 이때  $C_s$  값이 클수록 확실한 소프트 스위칭을 가능하게 하지만 너무 클 경우, 그만큼 보조회로의 전도 손실이 커진다. 위의 조건을 적절하게 고려하여 본 논문에서는  $i_{Lr}$ 의 최 대값이  $i_{Lm}$ 의 1.2배가 넘지 않도록 설계한다. 모드 2에서 전류  $i_{Lr}$ 의 최대 값은  $w_r = \pi/2$ 일 때 나타난다. 따라서  $C_s$ 값은 다음의 공식에 의해 설계된다.

$$C_s = L_r \bigg( \frac{0.2 \cdot \quad (I_{Lm} - \triangle i_{Lm}/2)}{V_o/n} \bigg)^2 \simeq 1nF \eqno(15)$$

트랜스포머의 설계 방법은 다음과 같다. 모드 2에서 전류  $i_s$ 가 0이 되는 시점에 주 스위치의 전압이 0이 되게 설계

Fig. 6. Effect of leakage inductance.

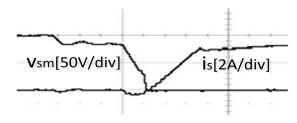

Fig. 7. Experimental results of main switch  $S_m$  when main switch turn-off.

한다. 이 조건은 트랜스포머의 턴 비가  $N_2/N_1 = V_o/V_i$ 이며 본 논문에서는  $N_1:N_2=52:13$ 로 설계하였다.

#### 4. 실험 결과 및 분석

본 논문에서는 제안한 컨버터를 증명하기 위하여 100W 컨버터를 제작하여 실험하였다. 입력전압 48V와 스위칭 주파수 200KHz에 대하여 출력전압이 12V가 되게 구성하였다. 보조 회로의  $L_r$ 과  $C_s$ 의 값은 각각 8uH, 1nF으로 설계하였다. 또한 트랜스포머의 자화 인덕터  $L_m=82uH$ 이며 1차측과 2차측의 권선 비는  $N_1:N_2=52:13$ 이다.

주 스위치와 보조 스위치로는 각각 IRF640과 IRF530을 사용하였으며 2차측 출력 다이오드와 보조 다이오드 로는 샤트키 다이오드를 선정하였다.

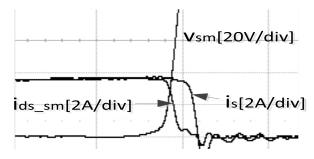

그림 4는 그림 3에 대한 실제 파형이다. 그림 3과 비교해 보았을 때, 이들 결과 파형으로부터 제안된 회로의 동작이 이론적인 동작과 일치함을 볼 수 있었다. 또한 보조 회로를 사용하여 주 스위치가 턴-온, 턴-오프 순간에 소프트 스위칭이 이루어짐을 알 수 있다.

그림 5는 주 스위치가 턴-온 순간에 스위치에 걸리는 전압 및 흐르는 전류 파형을 보여주고 있다. 위의 동작 원리와 같이 주 스위치의 전류가 0 이하로 내려갔다가 다시 0이 되는 순간 주 스위치를 켜서 소프트 스위칭 하는 것을 볼 수 있다. 또한 보조 회로에 사용된 8µH로

인하여 보조 다이오드의 전류 기울기가  $6A/\mu$ sec로 제한되므로 역회복 시간으로 인한 손실이 최소화 되었다.

Fig. 8. The competition of proposed converter and conventional converter.

한, 보조스위치가 개방될 때 또한 소프트 스위칭 하는 것을 위의 파형으로부터 알 수 있다.

그림 5에서 보조스위치가 켜질 때, 주 스위치의 전압이 약간 내려가는 것은 트랜스포머의 누설 인덕턴스가원인으로써 그림 6에서 시뮬레이션의 이상적인 트랜스포머에 누설 인덕턴스 소자를 추가로 삽입하여 시뮬레이션 한 결과 그림 7과 같이 보조 스위치가 켜지는 구간에 전압이 약간 하강 하는 것을 볼 수 있다. 누설 인덕턴스의 영향으로 주 스위치는 ZCZVT 조건을 만족시키지 못하지만 스위치가 켜지는 시점에 전류는 0이므로 ZCT 조건에서 소프트 스위칭을 한다.

제안한 회로의 장점으로 보조스위치의 턴-오프 소프트 스위칭 뿐만 아니라 주 스위치도 턴-오프 순간에 소프트 스위칭 하는 장점이 있다. 스위치가 꺼지는 순간전류는 보조 커패시터로 흐르며 스위치의 전압을 천천히 상승 시킨다. 이는 그림 7의 파형을 통하여 확인 할수 있다.

스위치가 꺼지는 순간 전류는 보조 커패시터로 대부분 흐르게 된다. 위의 그림 7와 같이 주 스위치의 전류와 전압이 겹치는 부분이 현저하게 낮아지고 이에 따라서 턴-오프 시에 스위치에서 발생하는 손실이 최소화된다.

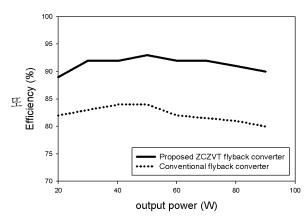

제안한 회로의 효율을 기존의 플라이백 컨버터와 비교하기 위하여 동일한 동작 주파수와 동일한 출력 전압을 가지고 출력 전류 값을 변화 시켜 효율을 측정하였다. 위의 결과를 그림 8에 나타내었다. 위의 결과를 통하여 제안된 회로가 기존의 플라이백 컨버터 보다 높은 효율을 가지는 것을 확인 할 수 있다. 부하가 커질수록스위치에서의 손실이 효율에 크게 영향을 미치는 것을 볼 수 있다. 또한 최대부하에서 효율이 낮은 것은 도선내부의 손실 부분이 증가하여 효율이 다소 떨어진다. 제안한 회로는 소프트 스위칭을 통하여 EMI를 줄이고 기존의 플라이백과 동일한 동작을 하므로 제어에 있어서도 용이하다.

#### 5. 결 론

본 논문에서는 기존의 PWM 방식과 공진형 컨버터의 단점을 해결하고 장점을 이용하여 ZCZVT 플라이백 컨버터를 설계하였다. 제안된 회로는 기존의 플라이백 컨버터에 보조회로가 추가된 형태이다. 주 스위치가 켜지기 직전의 짧은 시간 동안만 보조스위치가 동작함으로써 주 스위치가 소프트 스위칭 하도록 만든다. 이러한 동작 방식은 기존의 플라이백 컨버터와 동작 방식이 비슷하여 PWM 컨버터의 장점과 공진 방식의 이점을 모두 가지게 된다. 또한 보조 스위치의 턴 온, 턴 오프 시에소프트 스위칭하여 손실을 줄였으며, 주 스위치가 꺼지는 시점에도 소프트 스위칭하여 손실을 최소화 하였다.

본 논문에서는 제안한 회로의 동작원리와 설계 방식을 자세하게 기술하였다. 또한 설계 방법에 의하여 실제 컨버터를 만들고 실험을 통하여 제안된 회로의 유용성을 증명하였다.

#### References

- [1] K. H. Chen and T. J. Liang, "Design of quasi-resonant flyback converter control IC with DCM and CCM operation," in *IEEE Power Electronics Conference*, pp. 2750–2753, 2014.

- [2] J. S. Yoo, T. Ahn, G. Yu, J. Lee, and J. Lee, "A study on novel active clamp snubber applied DC-DC quasi resonant flyback converter to effectively reduce switch voltage surge," *IEEE Electrical Machines and Systems* (*ICEMS*), pp. 1–5, 2017.

- [3] W. A. Tabisz, P. M. Gradzki, and F. C. Y. Lee, "Zero-voltage-switched quasi-resonant buck and flyback converters-experimental results at 10 MHz," *IEEE Transactions on Power Electronics*, pp. 194-204, 1989.

- [4] N. Kasa, T. Iida, and A. K. S. Bhat, "Zero-voltage transition flyback inverter for small scale photovoltaic power system," in *Power Electronics Specialists Conference*, pp. 2098–2103, 2005.

- [5] Z. Li, X. Zhang, W. Qian, and H. Bai, "A novel zero-current-transition PWM DC-DC converter with coupled inductor," in *IEEE Power Electronics Conference*, pp. 1–4, 2016.

- [6] D. M. Bellur and M. K. Kazimierczuk, "Zero-current-transition two-switch flyback pulse-width modulated DC-DC converter," *IET Power Electronics*, pp. 288-295, 2011.

- [7] Y. C. Hsieh, M. R. Chen, and H. L. Cheng, "An interleaved flyback converter featured with zero-voltage transition," *IEEE Transactions on Power Electronics*, pp. 79–84, 2010.

- [8] K. Soltanzadeh, H. Khalilian, and M. Dehghani, "Analysis, design and implementation of a zero voltage switching two-switch CCM flyback converter," *IET Circuits*, *Devices & Systems*, pp. 20–28, 2016.

- [9] E. C. Lee and H. C. Choi, "A zero-current-transition syn chronous buck converter using auxiliary circuit with soft -switching," *The Transactions of The Korean Institute of Power Electronics*, Vol. 18, No. 4, pp. 359–366, Aug. 2013.

- [10] H. C. Choi, "A new soft-switched PWM boost converter with a lossless auxiliary circuit," *The Transactions of The Korean Institute of Power Electronics*, Vol. 11, No. 2, pp. 149–158, Apr. 2006.

### 주현승(朱賢勝)

1992년 8월 27일생. 2017년 인제대 전자공 학과 졸업. 2017년~현재 동 대학원 정보통 신공학과 석사과정.

### <u>최현칠(崔鉉七)</u>

1964년 5월 25일생. 1989년 경희대 전기공학과 졸업. 1991년 한국과학기술원 전기 및 전자공학과 졸업(석사). 1994년 한국과학기술원 전기 및 전자공학과 졸업(공박). 1994년 한국과학기술원 정보전자연구소 연구원.

1995년~1996년 대우전자 모니터 연구소 선임연구원. 1997년~ 현재 인제대 전자공학과 부교수.