ISSN: 1226-7244 (Print) ISSN: 2288-243X (Online) 논문번호 19-04-28

194

# PMOS가 삽입된 SCR 기반의 ESD 보호 회로에 관한 연구 A Study on SCR-Based ESD Protection Circuit with PMOS

곽 재 창\*

Jae-Chang Kwak\*\*

## **Abstract**

In this paper, the electrical characteristics of Gate grounded NMOS(GGNMOS), Lateral insulated gate bipolar transistor(LIGBT), Silicon Controlled Rectifier(SCR), and Proposed ESD protection device were compared and analyzed. First, the trigger voltage and holding voltage were verified by simulating the I-V characteristic curve for each device. After that, the robustness was confirmed by HBM 4k simulation for each device. As a result of HBM 4k simulation, the maximum temperature of the proposed ESD protection device is lower than that of GGNMOS and GGLIGBT and SCR, which means that the robustness is improved, which means that the ESD protection device is excellent in terms of reliability.

## 요 약

본 논문에서는 Gate grounded NMOS(GGNMOS)와 Gate grounded Lateral insulated gate bipolar transistor(GGLIGBT), Silicon Controlled Rectifier(SCR), 그리고 제안된 ESD 보호 소자에 대한 전기적 특성을 비교 및 분석하였다. 우선 각 소자에 대한 I-V 특성 곡선을 시뮬레이션 함으로써 트리거 전압과 홀딩 전압을 확인하였다. 그 후에 각 소자에 대한 HBM 4k 시뮬레이션을 통해서 감내 특성을 확인하였다. HBM 4k 시뮬레이션 결과, 제안된 ESD 보호소자의 최대 온도가 GGNMOS와 GGLIGBT와 SCR에 비해서 낮기 때문에 그만큼 감내 특성이 개선되었다고 할 수 있으며, 이는 신뢰성 측면에서 우수한 ESD 보호소자임을 의미한다.

Key words: SCR, GGNMOS, Trigger voltage, Holding voltage, Robustness

### 1. 서론

ESD(Electro Static Discharge)란 충전된 전하가 접촉에 의하여 전위가 낮은 물질로 이동하는 현상을 의미한다. 이를 디바이스 측면에서 고려할 경우대전된 기계나 인체가 반도체의 외부 핀과 접촉 했을 때, 고 전류 특성과 단시간 특성을 포함하기 때문에 IC내부의 반도체 소자와 금속 배선 등을 파괴

하고 회로의 오작동을 유발시켜 IC에 손상을 입힌다. 이러한 ESD에 의한 파괴는 전체 IC 불량률의 30%이상을 차지한다. 따라서 ESD 현상은 집적회로의 올바른 동작과 신뢰성 측면에서 반드시 고려해야 한다[1-2]. 또한, 반도체 공정에 대한 산업 기술이 점차 발전하면서 날이 갈수록 IC의 소형화와집적화가 이루어지고 있기 때문에 ESD 보호회로는 적은 공간을 차지할 필요성이 있다. 대표적인

E-mail: jckwak@skuniv.ac.kr, Tel: +82-2-940-7758

This research was supported by Seokyeong University in 2019.

Manuscript received Dec. 9, 2019; revised Dec. 20, 2019; accepted Dec. 27, 2019.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>\*</sup> Dept. of Computer Science, Seokyeong University

<sup>★</sup> Corresponding author

<sup>\*</sup> Acknowledgment

ESD 보호 소자로는 SCR과 GGNMOS가 있는데 SCR은 높은 전류 구동 능력과 면적대비 우수한 감내 특성이 있지만 내부회로가 낮은 전압을 사용하는 경우 적용이 어렵고 원하지 않게 턴-온 될 수 있고 GGNMOS는 제어와 제작이 쉬운 반면에, 열전도도가 낮은 산화막 부근에서 열화현상에 취약하고 LDD기술이 접합의 유효깊이를 감소시키며 Silicide기술이 성능을 저하시킨다는 문제점이 있다[3-4]. 본 논문에서는 ESD 보호 소자인 GGNMOS와 GGLIGBT와 SCR 그리고 제안된 ESD 보호 소자에 대한 전기적 특성을 비교하고 TCAD 시뮬레이터를 사용하여 이를 검증하였다.

## Ⅱ. 본론

## 1. GGNMOS(Gate Grounded NMOS)

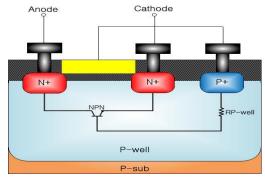

Fig. 1. Cross section view of a GGNMOS. 그림 1. GGNMOS의 단면도

그림 1은 GGNMOS의 단면도를 보여주고 있다. GGNMOS은 기존의 MOSFET 구조를 기반으로 만 들어진 ESD 보호소자로 제어와 제작이 쉽고 용이 하기 때문에 가장 빈번하게 쓰이고 있는 구조이다. GGNMOS의 구조는 Gate와 Source 및 Body를 Ground에 연결하고 Drain단만 입력 패드 부분에 연 결한 구조이다. GGNMOS의 동작원리는 Self bias 된 기생 NPN bipolar junction transistor(BJT)의 동 작으로 설명할 수 있고 Drain단에 ESD 전류가 인가 되면 Drain과 Body 사이의 Avalanche breakdown 에 의해서 Base 전류가 형성되고 Body의 전압을 상승시킨다. Body의 상승된 전압이 Body와 Source 사이에 존재하는 PN접합의 Built in potential보다 높아지면 접합은 Forward bias 되어서 Drain단으 로부터 인가된 ESD 전류를 Source로 내보내게 된 다. 기생 NPN BJT가 Hole 전류에 의해 Turn-on 되기 바로 직전의 지점을 Triggering point라고 하고 이 지점의 전류와 전압을 트리거 전류와 트리거 전압이라고 한다. 기생 NPN BJT가 작동하면 높은 전압을 더 이상 유지하지 못하고 전압이 감소하는 Negative resistance 구간을 형성하고 이때의 가장 낮은 전압을 홀딩전압이라고 부른다. 이후 기생 BJT를 통해서 ESD 전류가 너무 커지면 ESD 보호소자의 온도가 일부분 상승하면서 ESD 보호소자가 Thermal failure된다.

#### 2. GGLIGBT (Gate Grounded LIGBT)

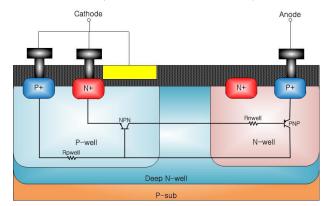

Fig. 2. Cross section view of a GGLIGBT. 그림 2. GGLIGBT의 단면도

그림 2는 GGLIGBT의 단면도를 보여주고 있다. GGLIGBT는 기존의 LIGBT의 N-well에 플로팅 N+ 확산영역을 포함하는 구조이다. 이러한 구조는 N-well보다 높게 도핑 된 플로팅 N+ 확산영역에 서 Avalanche breakdown 이후에 Electron-hole pair (EHP)가 발생하고 기생 PNP BJT의 Base에서의 Recombination이 증가하고 결과적으로 홀딩 전압 이 증가하게 되는 구조이다. GGLIGBT의 동작원 리는 다음과 같다. Anode단에 ESD 전류가 유입 되면 펀치스루가 발생하고 P-well과 Deep n-well 사이의 Reverse bias로 인한 공핍 층의 확산으로 Emitter쪽으로 전류가 형성된다. 이러한 진행 과정 동안 생성된 Electron과 Hole은 각각 Collector와 Emitter를 통해 빠져나가게 된다. 형성된 Hole 전 류는 P-well에서의 축적을 유도한다. P-well과 Emitter N+ 사이의 전위장벽을 넘어서게 되면, Pwell과 Emitter N+는 Forward bias 되고 Emitter N+, P-well, Deep n-well로 형성된 기생 NPN BJT가 동작하게 된다. 기생 BJT는 Collector P+, Deep n-well 및 P-well로 형성된 기생 PNP BJT

의 바이어스 전류를 제공하기 때문에 기생 BJT는 양극 Feedback을 통해 ESD 전류에 대한 방전경로를 형성한다.

#### 3. SCR (Silicon Controlled Rectifier)

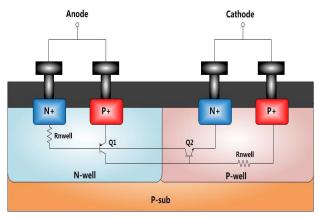

Fig. 3. Cross section view of a SCR. 그림 3. SCR의 단면도

그림 3은 SCR의 단면도를 보여주고 있다. SCR 은 높은 임피던스 상태에서 낮은 임피던스로 바뀌 는 성질 때문에 파워 소자 응용 분야에서 널리 쓰 이며 Lateral PNP BJT와 Lateral NPN BJT가 연 결된 PNPN 구조이다. 동작원리를 살펴보면 Anode 단으로 유입된 ESD 펄스에 의해서 N-well 전압이 상승하게 되고, N-well과 P-well은 Reverse bias가 걸리게 되면서 접합 간에 공핍층이 형성된다. 그리고 이 공핍층에 생성된 전계가 Avalanche breakdown을 일으키는 임계 값을 넘으면 N-well로 유입된 Hole 이 P-well로 유입된다. 유입된 Hole 전류는 P+ cathode로 흐르면서 Lateral PNP BJT(Q1)가 동 작을 하게 된다. 이 때, N-well로부터 유입된 Hole 전류가 상승하게 되어 P-well 영역의 일부가 N+ cathode 접합의 Built in potential보다 높아지면 Lateral NPN BJT(Q2)가 동작한다. 이 동작으로 인해서 N+ cathode로부터 유입된 Electron 전류는 다시 Q1의 Base 전류를 형성하여 Q1의 Collector 전류를 증가시킨다. 그리고 증가된 Q1의 Collector 전류는 Q2의 Base 전류로 작용하여 Q2의 Collector 전류를 증가시키는 Positive feedback 동작으로 ESD 펄스를 방전시킨다.

## 4. 제안된 ESD 보호 소자

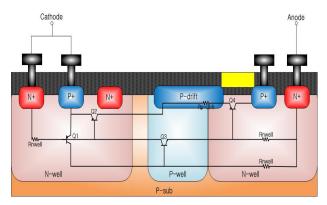

그림 4는 제안된 ESD 보호 소자의 단면도를 보

Fig. 4. Cross section view of a Proposed ESD protection device

그림 4. 제안된 ESD 보호소자의 단면도

여주고 있다. 이 보호 소자는 Latch-up 문제를 해 결하기 위해서 제안된 높은 홀딩 전압을 갖는 Advanced high holding voltage silicon controlled rectifier(AHHVSCR) 구조의 낮은 감내 특성 문제 를 보안하기 위한 보호 소자이다. 이 소자는 기생 BJT로 SCR의 구조를 나타내었고 좌측의 N-well 에 존재하는 P+ 확산영역과 N+ 확산영역은 Anode 단에 연결하여 우측의 N-well에 존재하는 N+ 확 산영역과 P+ 확산영역은 Cathode단에 연결한다. 뿐만 아니라, AHHVSCR과 다르게 Cathode단에 추가적으로 Gate와 Cathode단과 연결된 P+ 확산영 역을 추가함으로 인해서 PMOS를 형성하였다. 이 ESD 보호 소자의 동작원리는 다음과 같다. ESD 전류가 Anode 단을 통해 유입되면 Anode 단의 전 위가 증가하고 좌측에 존재하는 N-well과 N+ 확 산영역의 전위가 증가하게 된다. Reverse bias 상 태인 P-well과 N-well의 접합 사이의 전계가 임계 값을 넘어서게 되면, Avalanche breakdown이 일 어난다. Avalanche breakdown에 의해서 EHP가 생성되는데 이때, Hole 전류는 P-drift 확산영역을 통해서 우측의 N-well에 존재하는 P+ 확산영역으 로 이동하고 Electron 전류는 좌측의 N-well을 통 해서 N+ 확산영역으로 이동한다. Electron의 이동 으로 인해서 N-well의 전위가 Anode단과 연결되 어 있는 N-well과 P+ 확산영역 접합의 전위 장벽 보다 커져서 두 접합이 Forward bias되면 기생 BJT(Q1,Q2)가 Turn-on된다. Q1과 Q2가 Turn-on 될 때, N+ 플로팅 확산영역으로 인해서 증가한 Base 영역에 의핸 Recombination 비율의 증가는 기생 PNP BJT의 전류이득을 감소시키게 된다.

Turn-on된 Q1을 통하여 흐르는 전류는 P-well을 통하여 Cathode와 연결된 N+ 확산영역으로 흐르게 되고 Q2를 통하여 흐르는 전류는 P-drift 확산 영역으로 흐르게 된다. Q1과 Q2를 통해서 흐르는 전류에 의해서 Q3의 N-well과 P-well 접합이 Forward bias되면 Q3는 Turn-on 된다. 뿐만 아니라, Turn-on된 Q3를 통해서 흐르는 전류에 의해 Q4가 Turn-on된다[5-6].

## 5. 시뮬레이션 결과

본 논문에서는 제안된 보호 소자를 확인하기 위해서 T-CAD 시뮬레이터를 사용하였다.

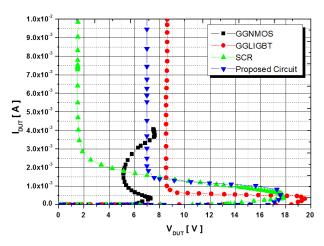

Fig. 5. I-V curve of GGNMOS and GGLIGBT and SCR and proposed ESD protection device.

그림 5. GGNMOSFET과 GGLIGBT와 SCR 그리고 제안된 ESD 보호 소자의 I-V 특성 곡선

Table 1. I-V curve of GGNMOS and GGLIGBT and SCR and proposed ESD protection device.

표 1. GGNMOS와 GGLIGBT와 SCR 그리고 제안된 ESD 보호 소자의 I-V 특성 곡선

| Structure        | Trigger Voltage | Holding Voltage |

|------------------|-----------------|-----------------|

| GGNMOS           | 7.5 V           | 5 V             |

| GGLIGBT          | 19.4 V          | 8.5 V           |

| SCR              | 17.8 V          | 1.5 V           |

| Proposed Circuit | 17.9 V          | 6.9 V           |

그림 5와 표 1은 GGNMOS와 GGLIGBT와 SCR 그리고 제안된 ESD 보호 소자의 I-V 특성의 시뮬 레이션 결과이다. 각 소자의 트리거 전압은 7.5V, 19.4V, 17.8V, 17.9V이고 홀딩 전압은 5V, 8.5V, 1.5V, 6.9V이다. 이 결과로 미루어 보았을 때, GGNMOS의 트리거 전압이 다른 세 소자의 트리거 전압보다 낮기 때문에 GGNMOS에 비해서 다른 세 소자는 보다 더 높은 전압에서 적용이 가능하다고 할 수 있다.

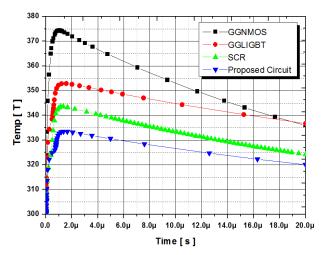

Fig. 6. HBM 4k Simulation of GGNMOSFET and GGLIGBT and PMOS inserted Circuit.

그림 6. GGNMOSFET과 GGLIGBT 그리고 PMOS가 삽입된 구조의 HBM 4k 시뮬레이션

Table 2. HBM 4k Simulation of GGNMOS and GGLIGBT and SCR and proposed ESD protection device.

표 2. GGNMOS와 GGLIGBT와 SCR 그리고 제안된 ESD 보호 소자의 HBM 4k 시뮬레이션

| Structure        | Peak Temperature |

|------------------|------------------|

| GGNMOS           | 374.3 K          |

| GGLIGBT          | 352.9 K          |

| SCR              | 343.5 K          |

| Proposed Circuit | 333.4 K          |

그림 6과 표 2는 GGNMOS와 GGLIGBT와 SCR 그리고 제안된 ESD 보호 소자의 HBM 4k 시뮬레이션 결과이다. 각 소자의 최대 온도는 374.3K, 352.9K, 343.5K, 333.4K이다. 이는 HBM 4k를 인가한 후에 시간의 변화에 따른 클램핑 전압과 ESD 전류가 방전할 때의 회로 격자의 온도 상승에 따른 그래프이다. 즉, 제안된 ESD 보호 소자의 최대온도는 333.4K로 다른 세 소자에 비해서 훨씬 낮은 온도에서 ESD 전류를 방전한다는 의미이다. 따라서 제안된 ESD 보호소자의 구조가 다른 세 구조에 비해서 감내 특성이 향상되었다.

## Ⅲ. 결론

본 논문에서는 GGNMOS과 GGLIGBT와 SCR 그리고 제안된 ESD 보호 소자의 전기적 특성을 비 교 및 분석하였다. GGNMOS의 트리거 전압이 제 안된 ESD 보호 소자보다 현저하게 낮기 때문에 제 안된 ESD 보호 소자는 고전압용 어플리케이션에 적용이 가능하다. 그리고 홀딩전압을 보면, 제안된 ESD 보호 소자가 6.9V로 SCR과 GGNMOS에 비 해서 높기 때문에 상대적으로 높은 래치업 면역을 가진다. 물론, GGLIGBT에 비해서 다소 떨어지는 홀딩 전압을 가졌지만, 각 소자의 최대온도를 비교 하였을 때, 제안된 ESD 보호 소자의 최대온도가 333.4K로 가장 낮기 때문에 다른 세 소자에 비해서 뛰어난 감내 특성을 가진다. 우수한 감내 특성은 신뢰성 방면에서 뛰어나다는 것을 의미 하는데 이 는 일정한 조건에서 ESD 보호 소자의 목적인 ESD 전류 방전을 적절하게 수행할 수 있는지에 관한 것 이기 때문에 가장 중요한 측면이라고 할 수 있다. 따라서 제안된 ESD 보호 소자는 다른 세 소자보다 향상된 ESD 보호 소자이다.

## References

[1] S. Tiwari, T. Undeland, S. Basu, and W. Robbins, "Silicon carbide power transistors, characterization for smart grid applications," in *Power Electronics and Motion Control Conference* (*EPE/PEMC*), 15th International, pp.LS6d.2-1-LS6d.2-8, 2012.

DOI: 10.1109/EPEPEMC.2012.6397497

[2] R. Kaplar, M. J. Marinella, S. DasGupta, M. A. Smith, S. Atcitty, M. Sun, and T. Palacios, "Characterization and reliability of sic-and ganbased power transistors for renewable energy applications," 2012 IEEE Energytech, pp.1 - 6, 2012.

DOI: 10.1109/EnergyTech.2012.6304627

[3] Y. Wang, X. Jin, L. Yang, Q. Jiang, and H. Yuan, "Robust dualdirection SCR with low trigger voltage, tunable holding voltage for high-voltage ESD protection," *Microelectron Rel.*, vol.55, no.3-4, pp.520-526, 2015.

DOI: 10.1016/j.microrel.2014.12.006

[4] S. Luo, J. A. Salcedo, J.-J. Hajjar, Y. Zhou, and J. J. Liou, "ESD protection device with dual-polarity conduction and high blocking voltage realized in CMOS process," *IEEE Electron Device Lett.*, vol.35, no.4, pp.437-439, 2014.

DOI: 10.1109/LED.2014.2305634

[5] B. B. Song, K. I. Do and Y. S. Koo, "SCR-Based ESD Protection Using a Penta-Well for 5V Applications," *Journal of the Electron Devices Society*, pp.691-695, 2018.

[5] Mergens M et al. "High holding current SCRs (HHI-SCR) for ESD protection and latchup immune IC operation," *proceedings of EOS/ESD symposium*, pp.10–17, 2002.

## **BIOGRAPHY**

#### Jae Chang Kwak (Member)

1983 BA in Yonsei Univ. 1989 MS in Univ. of Iowa 1993 PhD in Univ. of Iowa 1995~present Professor at Dept. of Computer Science, Seo Kyeong Univ.

<Research Interest> Network Traffic Control, QoS, Realtime Scheduling, Embedded System