# Three-Dimensional Selective Oxidation Fin Channel MOSFET Based on Bulk Silicon Wafer

Young-Kyun Cho<sup>1</sup>, Jae-Won Nam<sup>2\*</sup>

<sup>1</sup>Assistant Professor, Division of Electrical, Electronic and Control Engineering, Kongju National University <sup>2</sup>Assistant Professor, Department of Electronic Engineering, SeoulTech

# 벌크 실리콘 기판을 이용한 삼차원 선택적 산화 방식의 핀 채널 MOSFET

## 조영균<sup>1</sup>, 남재원<sup>2\*</sup>

### <sup>1</sup>공주대학교, 전기전자제어공학부 조교수, <sup>2</sup>서울과학기술대학교 전재T미디어공학과 조교수

**Abstract** A fin channel with a fin width of 20 nm and a gradually increased source/drain extension regions are fabricated on a bulk silicon wafer by using a three-dimensional selective oxidation. The detailed process steps to fabricate the proposed fin channel are explained. We are demonstrating their preliminary characteristics and properties compared with those of the conventional fin field effect transistor device (FinFET) and the bulk FinFET device via three-dimensional device simulation. Compared to control devices, the three-dimensional selective oxidation fin channel MOSFET shows a higher linear transconductance, larger drive current, and lower series resistance with nearly the same scaling-down characteristics.

Key Words : SoxFET, FinFET, Bulk FinFET, Raised Source/Drain, Series resistance, Recess channel

**요 약** 본 삼차원 선택적 산화를 이용하여 20 nm 수준의 핀 폭과 점진적으로 증가된 소스/드레인 확장 영역을 갖는 핀 채널을 벌크 실리콘 기판에 제작하였다. 제안된 기법을 이용하여 삼차원 소자를 제작하기 위한 공정기법 및 단계를 상세히 설명하였다. 삼차원 소자 시뮬레이션을 통해, 제안된 소자의 주요 특징과 특성을 기존 FinFET 및 벌크 FinFET 소자와 비교하였다. 제안된 삼차원 선택적 산화 방식의 핀 채널 MOSFET는 기존의 소자들과 비교하여 더 큰 구동 전류, 더 높은 선형 트랜스컨덕턴스, 더 낮은 직렬 저항을 가지며, 거의 유사한 수준의 소형화 특성을 보이는 것을 확인하였다.

주제어: SoxFET, FinFET, 벌크 FinFET, 상승 소스/드레인, 직렬저항, Recess 채널

## 1. Introduction

The multiple gate metal oxide semiconductor field effect transistor (MOSFET) is widely recognized as promising candidates for ultimate scaling of MOSFETs to the shortest channel length[1-3]. Among the multiple gate devices, the fin field effect transistor device (FinFET) is in the spotlight for its simple process, which is compatible with the conventional planar process[4]. FinFETs have been fabricated on silicon on insulator (SOI) substrates to overcome the problems associated with the

\*This study was supported by the Research Program funded by the SeoulTech(Seoul National University of Science and Technology). \*This article is extended and excerpted from the conference paper presented at International Microprocesses and Nanotechnology Conference

\*Corresponding Author : Jae-Won Nam (jaewon.nam@seoultech.ac.kr) Received September 9, 2021 Revised October

Accepted November 20, 2021

Revised October 20, 2021 Published November 28, 2021 short channel effect. However, FinFETs built on SOI wafers suffer from heat dissipation issues and floating body problems[5,6]. In addition, it is still expensive adapting the SOI wafers.

Recently, the FinFET fabricated on bulk Si substrates is known to solve these problems[7]. The bulk FinFET has advantages over the conventional SOI FinFET, but it still remains issues. One of the major challenges in making Si FinFET is to make small and controllable fin width to suppress of short channel effects. Ashing and trimming technology[8], spacer lithography technology[9] and e-beam lithography technology[10] have been produced, but the plasma damage is occurred on the sidewall of the fin channel during reactive ion etching process. The other problem is enabling high drive current capability by reducing the source/drain (S/D) parasitic series resistance. Selective epitaxial re-growth process[11,12] has been proposed to thicken the fin outside of the gate region, but it needs well-formed sidewall spacers which isolate the fin from the gate.

In this paper, we propose the selective oxidation fin channel MOSFET (SoxFET) based on a bulk Si wafer to vield extremely narrow fin structure and reduced parasitic series resistance using the simple recess-channel technology over a 0.5 µm CMOS process[13,14]. This article is extended and excerpted from the conference paper presented at[15]. The proposed process is more robust and much simpler than other techniques for the same purpose using selective epitaxial re-growth process. The detailed fabrication procedure is explained to form a proposed device. Finally, the electrical characteristics of the SoxFET are compared with those of the bulk FinFET and the conventional FinFET using three- dimensional device simulation.

### 2. Experimental Implementation

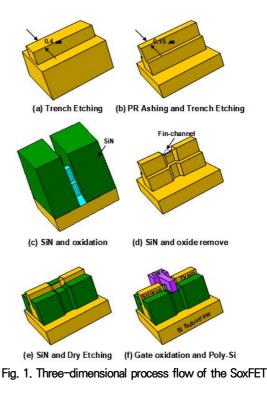

The device structure and the schematic process flow of the proposed SoxFET are shown in Fig. 1. In the implementation of the SoxFET, it is important to achieve controllable dimensions for the fin width because it alleviates short channel effects and governs off-state leakage current. The critical process steps for fin channel formation of the SoxFET are explained as follows. As the starting material, a (100) p-type silicon wafer was used. photoresist was coated and 0.5 um А design-ruled i-line photolithography steps were taken to define the active region. Trenchs were etched with a width of 400 nm and depth of 250 nm (Fig. 1(a)). The 400 nm silicon film was shrunken to 150 nm by photoresist ashing and dry etching (Fig. 1(b)). The above process steps are not required if the state-of-the-art design rule lithography becomes possible. These processes were performed solely for nanoscale

fin channel fabrication with the conventional micro-meter order lithography technology. The remaining 150 nm width silicon pattern serves as a starting material to oxidation during the subsequent thermal process. A thermal oxide with a thickness 10 nm was grown; a 300 nm SiN layer was deposited. Through sufficient over-etching, the SiN was fully removed from the center of the active pattern. Next, the thermal oxide layer was grown for 35 min at 950 °C in O2 to make a thinned fin-channel. Unlike the silicon oxide layer, the SiN does not allow oxygen to permeate. Therefore, a thermal oxide layer was created at only a portion where the gap was produced, i.e., the portion of the channel and S/D extension regions (Fig. 1(c)). After the oxidation barriers composed of SiN were removed, the thermal oxide was also removed by wet etching. The shape of the fin channel resembling a bird's beak is shown in Fig. 1 (d). Owing to the three-dimensional selective oxidation, it is possible to fabricate the raised S/D structure without epitaxial growth or layer deposition which has gradually increased connection regions from the channel to S/D regions. These thickened S/D regions help to improve overall parasitic series resistances.

A thermal oxide of 10 nm thickness was grown and a SiN layer of 250 nm thickness was deposited. With dry etching, the removal of SiN layer was stopped in the middle of the silicon sidewall by about 80 nm below the silicon top surface. A 10 nm buffer oxide, which had been underneath the SiN layer, was etched in a diluted HF solution. A 150 nm thick tetraethyl orthosilicate (TEOS) and a 150 nm poly-Si were deposited for scanning electron microscope (SEM) image.

#### 3. Results and Discussions

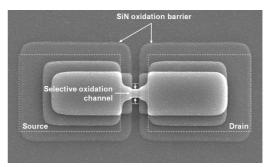

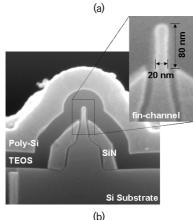

A top down SEM image of the selective oxidation test pattern taken after the center

oxidation layer removing and a cross-sectional SEM image of the silicon fin channel across the gate taken after the SiN layer removing are shown in Fig. 2 (a) and (b), respectively. Because of the three-dimensional selective oxidation, gradually increased extension regions from the channel to S/D regions were fabricated which advantageous to decrease parasitic are resistance and the top corners of the fin channel were rounded which are helpful to suppress possible leakage along the top corners. The width  $(W_{fin})$  and height  $(H_{fin})$  of the fin channel are 20 nm and 80 nm, respectively. An extremely small fin width and height beyond the lithographic limit is obtained with threedimensional selective oxidation technology.

Fig. 2. (a) Top down SEM image of the test pattern taken after the center oxidation layer removing, (b) Cross-sectional SEM image of the SoxFET's fin structure after SiN layer dry etching

Electrical characteristics of the SoxFET, the bulk FinFET [7] and the conventional FinFET [3]. as illustrated in Fig. 1 (f) are simulated using the Device3D Atlas software package from Silvaco. Schematic diagrams of side view and cross sectional plane of the three devices are described in Fig. 3.  $W_{fin}$  and  $H_{fin}$  of the fin channel are 20 nm and 80 nm, respectively, while the gate oxide thickness  $(T_{ox})$  is 2 nm. For the conventional FinFET device, the buriedoxide thickness is 150 nm, and the oxide hard mask thickness is 40 nm. To avoid adverse effects associated with heavy doping, the boron concentration in the channel (NA) is uniform and equal to  $1 \times 10^{16}$ /cm<sup>3</sup>. S/D extension region and n+ S/D regions doping (ND) profile is set as Gaussian with peak concentration of 2x10<sup>19</sup> /cm<sup>3</sup>. The lateral doping abruptness was 1 nm /dec, and the gate direct overlap length was 3 nm. The junction depth  $(X_j)$  is defined from the top surface of the fin and here the junction depth is 80 nm. The work function of the n<sup>+</sup> poly-Si gate ( $\Phi_M$ ) is chosen as 4.17 eV. All the device parameters included positions and shapes of S/D contacts of the SoxFET are equivalent to those of the bulk FinFET and the FinFET unless otherwise stated for the purpose of comparative analysis.

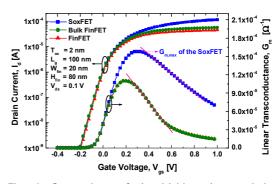

The Id-Vgs characteristic and the linear transconductance (G<sub>m</sub>) of the SoxFET are compared with those of control devices in Fig. 4. The gate length (Lg) of devices is fixed at 100 nm. The on-state current (Ion) of the proposed device is 117  $\mu$ A at V<sub>gs</sub>=1.0V and V<sub>ds</sub>=0.1 V, which is 2.04 and 2.58 times larger than those of the bulk FinFET and the conventional FinFET, respectively. These improvements in the performances are because of the raised S/D structure of the SoxFET, which reduces the parasitic series resistance at S/D extension regions. In other words, the on-state current is mainly affected by the series resistance introduced at extension regions. The maximum linear transconductance (G<sub>m,max</sub>) of the SoxFET shows 1.44 times larger than control devices at  $V_{ds}$ =0.1 V. As the gate bias increases, the proposed structure shows a lower degradation in G<sub>m</sub> compared to those of control devices which is also due to the lower S/D parasitic series resistance.

Fig. 4. Comparison of the Id–Vgs characteristic and linear transconductance characteristic of the SoxFET, bulk FinFET and FinFET

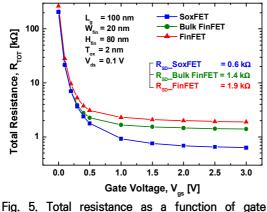

voltage for three devices

The on-state current and transconductance improvement should be attributed to the reduction in the S/D resistance. As a result, we extracted the total parasitic resistance at the channel and S/D regions by use of following method. The total resistance of a MOSFET R<sub>TOT</sub> is calculated by the sum of the channel resistance  $R_{CH}$  and parasitic S/D resistance  $R_{SD}$ , which is also expressed as  $V_{ds}/I_{s}[16]$ . At low  $V_{ds}$ and infinitely large  $V_{gs}$ ,  $R_{CH}$  diminishes and  $R_{TOT}$ becomes equal to R<sub>SD</sub>. The total resistance has been extracted as a function of  $V_{gs}$  and is plotted in Fig. 5. It can be seen from Fig. 5 that for high V<sub>gs</sub> values, R<sub>TOT</sub> becomes constant, and is taken as  $R_{SD}$ . The parasitic S/D resistance is significantly improved for SoxFET (0.6 k $\Omega$ ), compared to conventional FinFET (1.9 k $\Omega$ ) and bulk FinFET (1.4 k $\Omega$ ). The parasitic S/D resistance has been extracted from R<sub>TOT</sub>-V<sub>gs</sub> curve at  $V_{gs}$ =5 V, and  $V_{ds}$ =0.1 V. By selfconstructed raised S/D structure of the SoxFET, the parasitic S/D resistance can be reduced, resulting in improved transconductance and drive current. Nevertheless, parasitic capacitances between the S/D and the gate are inherent in the SoxFET. This is expected to adversely the device speed and impact power consumption. There is a tradeoff between series resistance and gate parasitic capacitances.

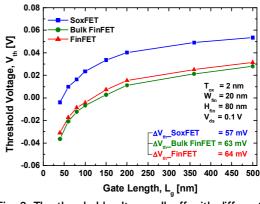

Fig. 6. The threshold voltage roll-off with different structures and different gate length

In Fig. 6, the threshold voltage of SoxFET according to the channel length is compared with those of the bulk FinFET and conventional FinFET. The threshold voltage roll-off is defined as the threshold voltage (V<sub>th</sub>) which is determined as the intersection between  $V_{gs}$  axis and extrapolated linear region of Id-Vgs curve measured at  $V_{ds}$ =0.1 V at any gate length while the silicon substrates are kept grounded at all times. Note that threshold voltages are relatively low compared to other fin channel structures because channel doping to adjust the threshold voltage was not performed. It can be seen that Vth rolloff is minimized by the use of the proposed structure, but other devices show an excellent behavior as well. The self-constructed raised S/D structure of the SoxFET plays a very important role in suppressing V<sub>th</sub> roll-off originating from drain potential extension into the source region. For the planar structure, the potential is strongly perturbed by the drain voltage and the potential barrier is removed in the channel region, in contrast to the raised S/D structure for which the potential barrier is only slightly affected in the drain region. Thus, the effects of the raised S/D structure of the SoxFET reduce the charge sharing in the channel, increase V<sub>th</sub>, and alleviate V<sub>th</sub> roll- off. Similar results were reported by Waite et al.[17] and Huang et al.[18] on transistor with raised S/D.

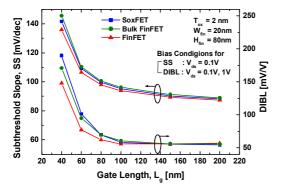

Fig. 7. The subthreshold slope and drain induced barrier lowering characteristic of the SoxFET compared with those of the bulk FinFET and FinFET

Fig. 7 shows the subthreshold slope (SS) and the drain induced barrier lowering (DIBL) comparisons dependence on the gate length. The SS was evaluated from the maximum slope in the  $I_d$ - $V_{gs}$  characteristics at  $V_{ds}$ =0.1 V and DIBL was evaluated as the gate voltage shift between  $V_{ds}$ =0.1 V and  $V_{ds}$ =1.0 V curves at  $I_d$ =10<sup>-8</sup> A. It can be observed that the SS and DIBL are minimized by the use of the conventional FinFET, but the SoxFET shows an excellent behavior as well. According to the current industry criterion for high performance applications, SS under 100 mV/dec and DIBL must be kept below 100 mV/V. Under these criteria, we can establish a guideline for minimum gate length to avoid short channel effects. In the case of the SoxFET with H<sub>fin</sub>=80 nm,  $W_{fin}$ =20 nm,  $N_A$ =1x10<sup>16</sup>/cm<sup>3</sup>, and  $N_D$ =  $2x10^{19}$ /cm<sup>3</sup> the minimum gate length decreased to 80 nm. In Table I, the electrical characteristics of the three devices are summarized.

### 4. Conclusion

A 20 nm thick fin channel and gradually increased S/D extension region are fabricated on a bulk silicon wafer using a three-dimensional selective oxidation. While verifying the DC characteristics of the SoxFET, the proposed device revealed larger on-current and linear transconductance. We believe that they are responsible for the improved on S/D parasitic resistance, while maintaining the threshold voltage roll-off, SS and DIBL. Therefore, a device geometry of the SoxFET is shown to be a promising solution for minimizing the parasitic S/D resistance of narrow fin devices. Based on simulation and measurement results, if additional device processes are developed along with the formation of the fin structure, it can contribute to the filed of low-cost and high-integration nm-scale CMOS devices in the near future.

Table 1. Summarized electrical characteristics of the SoxFET, bulk FinFET and FinFET.

|                          | SoxFET                | Bulk FinFET          | FinFET               |

|--------------------------|-----------------------|----------------------|----------------------|

| I <sub>on</sub> (µA)     | 117                   | 57.1                 | 45.4                 |

| $G_{m,max}(\Omega^{-1})$ | 1.58x10 <sup>-4</sup> | 1.1×10 <sup>-4</sup> | 1.1x10 <sup>-4</sup> |

| $R_{SD}(k \Omega)$       | 0.6                   | 1.4                  | 1.9                  |

| V <sub>th</sub> (V)      | 0.024                 | -0.007               | -0.004               |

| SS(mV/dec)               | 95.25                 | 96.28                | 93.90                |

| DIBL(mV/V)               | 58.23                 | 60.76                | 55.70                |

The device parameters are: H<sub>fin</sub>=80 nm, W<sub>fin</sub> =20 nm, T<sub>ex</sub>=2 nm, L<sub>g</sub>=100 nm, X<sub>j</sub>=80 nm, N<sub>4</sub>=1x10<sup>16</sup>/cm<sup>3</sup>, N<sub>D</sub>=2x10<sup>19</sup> /cm<sup>3</sup>, and  $\phi_{M}$ =4.17 eV.

#### REFERENCES

- P. Cadareanu, J. Romero-Gonzalez & P. E. Gaillardon. (2021). Parasitic Capacitance Analysis of Three-Independent-Gate Field-Effect Transistors, *IEEE Journal of the Electron Devices Society*, 9, 400-408. DOI : 10.1109/JEDS.2021.3070475

- [2] S. Nanda & R. S. Dhar. (2021). Implementation and Characterization of 14 nm Trigate HOI n-FinFET using Strained Silicon channel with reduced area on chip, 6th International Conference for Convergence in Technology, 1-4. DOI : 10.1109/I2CT51068.2021.9417877

- [3] A. Kumar, P. S. T. N. Srinivas & P. K. Tiwari. (2019). An Insight Into Self-Heating Effects and Its Implications on Hot Carrier Degradation for Silicon-Nanotube-Based Double Gate-All-Around (DGAA) MOSFETs, *IEEE J. Electron Dev. Society*, 7, 1100-1108. DOI : 10.1109/JEDS.2019.2947604

- Y. K. Choi et al. (2001). Sub-20nm CMOS FinFET Technologies, *Int. Electron Dev. Meeting*, 421-424.

DOI : 10.1109/IEDM.2001.979526

- C. T. Chuang, P. F. Lu & C. J. Anderson. (1998). SOI for Digital CMOS VLSI: Design Considerations and Advances, *Proc. IEEE, 86(4),* 689-720. DOI: 10.1109/5.663545

- [6] A. Gupta, R. A. Vega, T. B. Hook & A. Dixit. (2020). Impact of Hot-Carrier Degradation on Drain-Induced Barrier Lowering in Multifin SOI n-Channel FinFETs With Self-Heating. *IEEE Trans. Electron Dev.*, 67(5), 2208-2212. DOI : 10.1109/TED.2020.2977734

- [7] T. S. Park, H. J. Cho, J. D. Choe, D. Park, E. Yoon & J. H. Lee. (2004). Threshold Voltage Behavior of Body-Tied FinFET (OMEGA MOSFET) with Respect to Ion Implantation Conditions, *Jpn. J. Appl. Phys.,* 43(4B), 2180-2184. DOI: 10.1143/JJAP.43.2180

- [8] K. Asano, Y. K. Choi, T. J. King & C. Hu. (2001). Patterning Sub-30-nm MOSFET Gate with I-Line Lithography, *IEEE Trans. Electron Dev., 48(5)*, 1004-1006. DOI: 10.1109/16.918251

- Y. K. Choi, T. J. King & C. Hu. (2002). A Spacer Patterning Technology for Nanoscale CMOS, *IEEE Trans. Electron Dev., 49(3),* 436-441.

DOI: 10.1109/16.987114

- [10] J. Kedzierski, P. Xuan, E. Anderson, J. Bokor, T. J. King & C. Hu. (2000). Complementary silicide source/drain thin-body MOSFETs for the 20nm gate length regime, *Int. Electron Dev. Meeting*, 57–61. DOI : 10.1109/IEDM.2000.904258

- [11] Y. K. Choi, D. Ha, T. J. King & C. Hu. (2001). Nanoscale Ultrathin Body PMOSFETs With Raised Selective Germanium Source/Drain, *IEEE Electron Dev. Lett.*, 22(9), 447-448. DOI: 10.1109/55.944335

- [12] C. H. Park, M. H. Oh, H. S. Kang & H. K. Kang. (2004). A 15 nm Ultra-thin Body SOI CMOS Device with Double Raised Source/Drain for 90 nm Analog Applications, *ETRI Journal*, 26(6), 575-582. DOI: 10.4218/etrij.04.0104.0074

- [13] O. Faynot & B. Giffard. (1994). High Performance Ultrathin SOI MOSFET's Obtained by Localized Oxidation, *IEEE Electron Dev. Lett.*, 15(5), 175-177. DOI: 10.1109/55.291595

- [14] M. Chan, F. Assaderaghi, S. A. Parke, C. Hu & P. K. Ko. (1994). Recessed-Channel Structure for Fabricating Ultrathin SOI MOSFET with Low Series Resistance, *IEEE Electron Dev. Lett.*, 15(1), 22-24. DOI : 10.1109/55.289474

- [15] Y. K. Cho, T. Roh & J. Kim. (2005). SoxFET: Three-Dimensional Selective Oxidation Channel

MOSFET, Int. Microprocesses and Nanotechnology Conference, 266-267. DOI: 10.1109/IMNC.2005.203840

- [16] Y. Taur & T. H. Ning. (1998). CMOS DEVICE DESIGN: Fundamentals of Modern VLSI Devices : Cambridge Univ. Press.

DOI : 10.1017/CBO9781139195065

- [17] A. M. Waite et. al. (2005). Raised source/ drains for 50 nm MOSFETs using a silane/dichlorosilane mixture for selective epitaxy, *Solid-State Electronics*, 49, 529-534. DOI : 10.1016/j.sse.2005.01.019

- [18] H. J. Huang, K. M. Chen, C. Y. Chang, L. P. Chen, G. W. Huang & T. Y. Huang (2000). Reduction of Source/Drain Series Resistance and Its Impact on Device Performance for PMOS Transistors with Raised Si1-xGex Source/Drain, *IEEE Electron Dev. Lett.*, 21(9), 448-450. DOI : 10.1109/55.863107

### 조 영 균(Young-Kyun Cho)

[정회원]

- 2001년 2월 : 아주대학교 전자공학 부(공학사)

- · 2003년 2월 : 포항공과대학교 전자 컴퓨터공학부(공학석사)

- · 2019년 2월 : 충남대학교 전자전파 정보통신공학과(공학박사)

- · 2003년 2월 ~ 2020년 9월 : 한국전자통신연구원 책임연구원

- · 2020년 9월 ~ 현재 : 공주대학교 조교수

- ·관심분야 : 반도체 소자, 이날로그 집적회로, 안테나, RF 시스템 · E-Mail : ykcho@kongju.ac.kr

- [정회원]

- · 2006년 6월: KAIST 정보통신학부 (공학사)

- · 2008년 2월: KAIST IT공학부 (공학석사)

2019년 2월 : Univ. of Southern California 전자공학과(공학 석사 및 박사)

· 2008년 2월 ~ 2012년 6월 : 한국전자통신연구원 연구원

- · 2019년 9월 ~ 2020년 7월 : Intel Corp. 아날로그엔지니어

- · 2020년 9월 ~ 현재 : 서울과학기술대학교 조교수

- · 관심분야 : 반도체 소자, 아날로그 집적회로, 혼성신호 처리 시스템, 초고속 유선통신 송수신기, mmWave

- · E-Mail : jaewon.nam@seoultech.ac.kr