http://dx.doi.org/10.17703/JCCT.2023.9.5.517

JCCT 2023-9-63

# 레이다용 Phased RF Sub-Array MIMO 알고리즘 실시간 구혀

# Real-time Implementation of Phased RF Sub-Array MIMO Algorithm for Radar

김완식\*. 여환용\*\*

# Wansik Kim\*, Hwanyong Yeo\*\*

요 약 기존의 레이다는 RF Sub-Arrav 방식의 레이다 알고리즘을 적용하여 개발되어 왔고, 최근 차량용 레이다용으 로 Full 디지털 방식의 Multiple-Input Multiple-Output (MIMO) 레이다 알고리즘을 적용하여 구현되고 있다. 본 논문에서는 미확보 기술인 RF Sub-Array 방식의 하드웨어에 Phased MIMO 방식을 적용한 레이다 알고리즘을 실시간 가능하도록 구현 및 검증하였다. RF Sub-Array 방식의 Phased MIMO 알고리즘 기술 확보 차원에서 FPGA 기반의 실시간 신호처리를 위한 하드웨어 구조를 제시하고 이에 대한 설계 및 시뮬레이션을 통하여 성능을 먼저 예측하였으며, 이를 통하여 FPGA 기반의 광대역 MIMO FMCW 레이더의 디지털 송수신 신호처리 하드웨어 를 개발하였고 최종적으로 RF Sub-Array 방식의 Phased MIMO 레이다 알고리즘을 실시간 구현 및 검증하였다. 이를 바탕으로 향후 테라헤르츠 대역 레이다 등에 필요한 핵심 기술 확보 및 응용할 수 있을 것으로 판단된다.

주요어: Phased RF Sub-Array MIMO 알고리즘, 실시간, D-대역, FMCW, 테라헤르츠 대역 레이다

Abstract Existing radars have been developed by applying RF sub-array algorithms, and recently, fully digital Multiple-Input Multiple-Output (MIMO) radar algorithms have been implemented for vehicle radars. In this paper, the radar algorithm applying the Phased MIMO method to the hardware of the RF sub-array method, which is an unsecured technology, was implemented and verified in real time. In order to secure RF sub-array Phased MIMO algorithm technology, a hardware structure for FPGA-based real-time signal processing was presented, and performance was first predicted through design and simulation. Through this, the digital signal of FPGA-based broadband MIMO FMCW radar The processing hardware was developed, and the Phased MIMO radar algorithm of the RF sub-Array method was finally implemented and verified in real time. Based on this, it is judged that it will be possible to secure and apply core technologies necessary for terahertz band radar in the future.

Key words: Phased RF Sub-Array, phased MIMO Algorithm, Real-Time, FMCW, Terahertz-band Radar

\*\*정회원, LIG넥스원 수석연구원

접수일: 2023년 7월 15일, 수정완료일: 2023년 8월 25일

게재확정일: 2023년 9월 5일

Received: July 15, 2023 / Revised: August 25, 2023 Accepted: September 5, 2023 \*Corresponding Author: wansik.kim2@lignex1.com Microwave & Antenna R&D, LIGNex1, Korea

<sup>\*</sup>정회원, LIG넥스원 수석연구원 (제1저자, 교신저자) (초고주파기술개발단)

## 1. 서 론

차량용 레이더는 유럽을 선두로 W-대역의 밀리미 터파를 활용하고 있으며, 이제는 밀리미터파 센서의 구 현 방안 중 가격과 성능 면에서 많은 대안을 간구하고 준비되고 있다.[1][2][3] 현재 일부 MMIC 칩 제작 업체 에서 다채널 단일 칩을 공급하기는 하지만, 방산분야에 는 공급이 제한적이므로 송수신기에 적합한 MMIC 칩 의 확보가 어려운 한계가 있으므로 국내에서는 FMCW 레이더에 적용을 위하여 방산분야에서 확보하기 어려 운 W-대역 MMIC 칩을 개발한바 있으며 이 칩들을 적 용하여 W-대역의 다채널 송수신기를 개발하고 전이구 조 특성을 분석하여 시험된 전기적 특성을 비교 제시한 바 있고 이를 바탕으로 100 GHz 이하에서 차량용으로 레이다를 개발한 경험을 보유하고 있다.[4][5][6][7][8] 100 GHz 이상의 테라헤르츠에서는 기술 개발이 진전되 지 않고 있는 현실로 인하여 고분해능, 광대역 그리고 소형 체계에 장착이 불가능하다. 따라서 테라헤르츠 주 파수에서 기반 기술 확보가 필수적이며 광대역을 기반 으로 레이다와 통신에 사용 가능한 기술 개발을 통하여 테라헤르츠 레이다 등에 필요한 핵심 기술 확보 및 응 용할 수 있도록 한다.[9][10][11][12][13] 관련 기술 분야 의 확보 차원에서 광대역 MIMO 방식 FMCW 레이더 의 디지털 송수신 신호처리 하드웨어를 개발하였는데 MIMO 방식 FMCW 레이더는 여러 대역에 광대역 FMCW 신호를 동시에 송신 및 수신 가능한 구조이다. 또한 FMCW 신호는 대역폭이 각각 100 MHz이고, 전 체 대역폭은 약 300 MHz이므로 ADC의 sampling 속도 는 최소 800 Msps이상이어야 한다. FPGA를 이용한다 고 하더라도 800 Msps 이상의 ADC data를 처리하기 위해서는 병렬 신호처리 등 구조 개발이 필요하다.

본 연구에서는 FPGA 기반의 실시간 신호처리를 위한 하드웨어 구조를 제시하고 이에 대한 설계 및 시뮬레이션을 통하여 성능을 예측하였다. 이를 통하여 1 Gsps 이상을 지원하는 DAC 및 ADC와 함께 FPGA 기반의 광대역 Phased MIMO 방식 FMCW 레이더의 디지털 송수신 신호처리 하드웨어를 개발하고 MIMO 방식 FMCW 레이더는 여러 대역에 광대역 FMCW 신호를 동시에 송신 및 수신하는 구조에 대한 RF Sub-Array 방식의 Phased MIMO 레이다 알고리즘을 실시간 구현하였다. 최종적으로 미확보 기술인 RF

Sub-Array 방식의 하드웨어에 Phased MIMO 방식을 적용한 레이다 알고리즘을 실시간 가능하도록 구현 및 검증하였으며 이를 바탕으로 향후 테라헤르츠 대역 레이다 등에 필요한 핵심 기술 확보 및 응용할 수 있을 것으로 판단된다.

# Ⅱ. 설계 및 제작

### 1. RF 인터페이스 및 신호처리 하드웨어 시스템

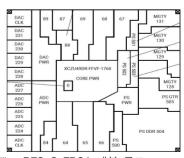

테라헤르츠 대역 레이다에 필요한 시제작을 위해서는 설계 및 제작이 요구되나 제작 전에 RF Sub-Array 방식의 Phased MIMO 레이다 방식의 실시간 알고리즘 검증이 필요하므로 상용 60 GHz RF Sub-Array 방식의 송수신모듈을 사용하여 구현하고자 한다. 이 송수신모듈은 16 패치 안테나로 구성되며 송신용 안테나 2개, 그리고 수신안테나 2개의 RF Sub-Array 방식으로 구성되어 있다. 상용 RF 송수신모듈에 필요한 DAC 및 ADC를 활용하여 각각 신호발생부 및 수신신호처리부에 적합하도록 아래와 같이 Xilinx RFSoC FPGA 하드웨어를 활용하였다. RF 인터페이스 및 신호처리를 위한 xilinx사의 RFSoC FPGA 보드를 활용하였으며 xilinx 사의 ZCU216 보드를 이용한다. 아래 그림 1은 ZCU216 보드에 사용된 xilinx XCZU49DR의 내부 구조를 보여준다.

XCZU49DR 내부에는 4개의 DAC 블록과 4개의 ADC 블록이 포함되어 있는 고성능 FPGA이다. 각 블록에는 4개의 DAC 또는 ADC가 포함되어 있고 XCZU49DR에는 16개의 DAC와 ADC가 포함되어 있으며 각 DAC와 ADC의 성능은 다음과 같다.

ADC : 14-bit, 최대 2.5 Gsps DAC : 14-bit, 최대 10.0 Gsps

그림 1. Xilinx RFSoC FPGA 내부 구조 Figure 1. Internal Structure of Xilinx RFSoC FPGA

2. 레이다용 RF Sub-Array MIMO 방식 송신부 알 고리즘 구현

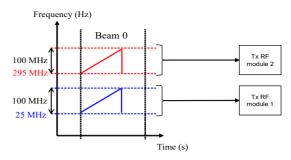

먼저 송신 목적의 송신부는 DAC를 활용하여 Frequency Division Multiple Access (FDMA)방식의 MIMO 기술에 적합하도록 2개의 주파수대역에 대하여 FMCW 신호를 발생한다. 낮은 주파수 대역 신호는 25 MHz ~ 125 MHz 대역폭으로 발생하고, 높은 주파수 대역 신호는 295 MHz ~ 395 MHz 대역폭으로 발생한 다. 한편 각 주파수 대역의 신호는 그림 2와 같이 각각 의 송신용 RF 모듈을 통해서 전송된다. 낮은 주파수대 역과 높은 주파수 대역의 FMCW 신호는 하나만 구현 하고 두 주파수 대역의 중심주파수 차이인 270 MHz 신호를 이용하여 상향 변환하여 생성하였다. 한편, 본 개발에서는 낮은 주파수 대역과 높은 주파수 대역의 FMCW 신호를 각각 생성하지 않았다. 위의 신호 특성을 보면, 각 주파수 대역의 FMCW는 대역폭은 100 MHz로 동일하며 단지 중심주파수만 다르다는 것을 알 수 있다. 이에 본 개발에서는 FMCW 신호 발생회로는 하나만 구 현을 하고 높은 주파수 대역 신호는 두 주파수 대역의 중 심주파수 차이인 270 MHz 신호를 이용하여 upconversion 하여 생성하였다. 위에서 보이는 바와 같이 생 성 신호의 최대 주파수는 395 MHz 이다. 이를 만족시키 기 위해서 본 개발에서는 DAC의 sampling rate를 2 Gsps 로 하였다. 2 Gsps의 sample 정보를 하나의 신호선으로 DAC로 전달할 수 있는 방법은 없다.

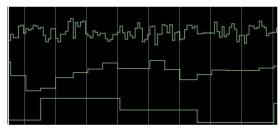

이에 본 연구에서는 125 MHz로 동작하는 신호선 16개를 병렬로 DAC로 전달하여 2 Gsps의 동작이 가능하도록하였다. 또한, FMCW 신호 발생부의 디지털 회로 또한 FPGA에서 2 GHz로 동작하는 것은 불가능하며 이에 각신호선 마다 FMCW 신호 발생부를 구현하였다. 위의 구현 방향을 만족하도록 구현한 신호 발생부의 구조는 Verilog HDL 언어로 구현하였으며 신호 발생부 Verilog HDL 회로의 모의 실험 결과는 위와 같다. 위의 결과를 살펴보면, 16개의 FMCW 신호가 발생하며, 각 발생 신호사이의 위상차가 동일하게 발생하는 것을 확인할 수 있다.

그림 2. 송신용 발생신호 특성 및 무선 전송 Figure 2. Generated Signals for transmission and Wireless transmission

3. 레이다용 RF Sub-Array MIMO 방식 수신부 알 고리즘 구현

#### 1) 수신부 신호처리 구조

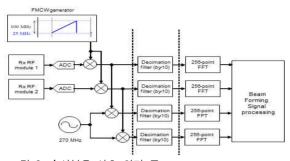

수신 목적의 수신부는 ADC를 위주로 하여 구현하게 되는데 Beat 신호 생성회로, Filter, Range-FFT 및 Beam forming 신호처리회로로 그림 3과 같이 구성된 다. Beat 신호 생성 회로는 송신 FMCW와 수신 FMCW 신호의 혼합으로 구현되어 있고 이때 하향 변 환을 위하여 270 MHz 신호생성기를 추가하였다.

#### 2) Decimation filter

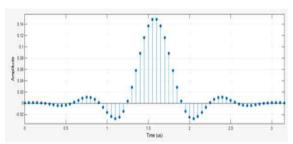

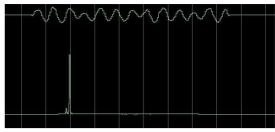

Filter의 경우 레이다 탐지거리를 고려하여 레이다 레이더의 탐색 범위가 150 m라고 가정하면, 레이더 신호의 왕복을 고려하면 그 시간은 1 usec가 되면, 그 시간동안의 송신 FMCW 신호와 수신 FMCW 신호의 주파수 차이는 2 MHz가 되며 이를 만족하는 레이더 신호처리용신호 rate는 4 Msps이다. 이를 위하여 Decimation Filter를 이용하여 설계된 Filter를 활용한 복잡도 등을고려해서 전체 구조에서 보인 바와 같이 3개의 decimation filter를 연속으로 통과시키는 방식으로 구현하였다. 최종 Impulse Response 응답은 아래 그림 4와 같으며 decimation filter 블럭의 verilog HDL 실험 결과는그림 5와 같이 확인할 수 있었으며 Decimation filter의 단계를 거치면서 출력 data의 sample rate가 낮아짐을 확인할 수 있다.

그림 3. 수신부용 신호 처리 구조 Figure 3. Signal processing structure of receiver

그림 4. 설계된 Filter를 이용한 Impulse Response 특성 Figure 4. Impulse Response Characteristics Using Designed Filters

그림 5. Decimation Filter 블록 HDL의 시험 결과 Figure 5. Test Results of Decimation Filter block HDL

#### 3) 거리 FFT

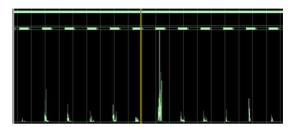

Range FFT는 기본적으로 Beat 응답 신호가 포함하는 거리에 비례하는 주파수의 연속파를 포함하며 Range FFT 연산을 수행함으로서 거리에 해당하는 주파수 성분을 추축할 수 있다. 본 연구에서는 256-FFT로 Range FFT를 구현하였으며 256-point FFT는 16-point FFT를 2 stage로 구성해서 구현하였다고 거리 FFT후 레이다에 대한 정상 신호인 경우의 특성을 그림 6에서 확인할 수 있었다.

그림 6. Range FFT HDL의 시험 결과 Figure 6. Test Results of Range FFT HDL

그림 7. Beam forming 신호처리 HDL의 실험 결과 Figure 7. Test Results of Beam forming Signal processing HDL

4) Phased MIMO Beam forming 신호처리 알고리즘 Beam forming 신호처리 회로에서는 각 경로의 FFT 결과에 수학적 알고리즘에 기반한 beam forming coefficient를 곱하고 특정 메모리 위치에 저장된 값과 합하여 동일한 위치에 update하여 저장한다. 이러한 beam forming 신호처리 시험 결과는 그림 7과 같다.

## Ⅲ. 실험 및 결과

RF Sub-Array 방식의 Phased MIMO 알고리즘을 구현하고 그림 8과 같은 실제 야외 시험을 진행하면 ZCU216 보드에서의 연산 결과를 XEM6010 보드로 전달받게 된다. 이 때, ZCU216 보드와 XEM6010 보드는 16 bit 병렬 data 형태로 전달되며, 최대 전달 속도는 62.5 Mword/sec이다. 그런데, FPGA에서의 연산결과는 32 bit 이기 때문에 의미있는 최종 결과의 최대 전달속도는 31.25 Msample/sec이다. XEM6010에서는 전달받은 data를 FIFO 등 제어회로를 거쳐서 USB 2.0 표준을 이용하여 PC로 전달되는데 PC로 전달된 data는 Matlab 소프트웨어에서 GUI 그래픽 기술을 이용하여 화면으로 표현된다.

아래 그림 9는 전체 시스템이 동작하는 환경에서 PC에 표현된 결과 출력 화면을 보여준 것으로 왼쪽 그래프는 결과 값을 z 축 즉, 높이로 표현하고, x 축은 각도이고, y

축은 레이더로부터의 거리이다. 실제 실시간으로 알고리 즘을 검증 결과 탐지 거리 10 m 이상에서 각도 분해능은 0.9도 이하를 검증할 수 있었다.

그림 8. 야외 시험 셋업 Figure 8. Ourdoor test setup

그림 9. RF Sub-Array 방식의 Phased MIMO 레이다 실 시간 알고리즘 처리 결과

Figure 9. Phased MIMO radar real-time algorithm processing result of RF Sub-Array method.

표 1. RF Sub-Array 방식의 Phased MIMO 알고리즘 실시간 레이다 검증 결과

Table 1. Phased MIMO radar real-time algorithm processing result of RF Sub-Array method.

| 구 분    | 검증 내용 및 결과                                        | 비고     |

|--------|---------------------------------------------------|--------|

| 빔포밍 방식 | RF Sub-Array MIMO                                 |        |

| 변조 방식  | FMCW                                              |        |

| 안테나 채널 | 2 + 2 (RF Sub-Array 기준)<br>32 + 32 (Patch 안테나 기준) | 실시간 동작 |

| 탐지 거리  | ≥ 10 m                                            |        |

| 각도 분해능 | ≤ 0.9 도                                           |        |

## IV. 결 론

본 논문에서는 미확보 기술인 RF Sub-Array 방식의 하드웨어를 적용한 Phased MIMO 레이다 알고리즘을 실시간 가능하도록 구현 및 검증하였다. 이를 위하

여 광대역 Multiple-Input Multiple-Output (MIMO) FMCW 레이더의 디지털 송수신 신호처리 하드웨어를 개발하고. MIMO FMCW 레이더의 여러 대역에 광대 역 FMCW 신호를 동시에 송신 및 수신하는 구조에 대 한 RF Sub-Array 방식의 Phased MIMO 레이다 알고 리즘을 실시간 구현하였다. 테라헤르츠 레이다에 적용 할 목적으로 핵심기술인 RF Sub-Array 방식의 MIMO 레이다 알고리즘을 실시간 구현하였으며 결과적으로 실제 실시간으로 알고리즘을 검증 결과 탐지 거리 10 m 이상에서 각도 분해능은 0.9 도 이하를 검증할 수 있 었다. 특히 구현된 핵심기술은 테라헤르츠 대역 다채널 어레이 MFC 칩 및 패키징 기술과 안테나 배열 등 관 런 기술을 확보하고 시제작 후 적용하여 관련 핵심 기 술을 활용하면 테라헤르츠 레이다 등에 필요한 핵심 기 술 확보를 통하여 최적으로 응용할 수 있을 것으로 판 단된다.

# References

- [1] An Official Gazette No 16322, Radio Wave Research Institute No 2006-84, 2006. 8. 23.

- [2] Shinichi Honma, Naohisa Uehara "Millimeter –Wave Radar Technology for Automotive Application," Technical Reports. 2001, pp.11–13.

- [3] Junhyeok Choi, Shin myoung Park, Changhyun Lee, Seungyeol Baek, Milim Lee "Design and Implementation of FMCW Radar Based on two-chip for Autonomous Driving Sensor" JIIBC Vol. 22, No. 6, pp.43–49, Dec.31, 2022

- DOI: https://doi.org/10.7236/JIIBC.2022.22.6.43

- [4] Seokchul Lee "W-band Multichannel FMCW Radar Sensor with Switching-TX Antennas," IEEE Sensor Journal. Vol. 16, No. 14, July 15, 2016

- [5] Wansik Kim, "Development of W-band Transceiver Module using Manufactured MMIC", The Journal of The Institute of Internet, Broadcasting and Communication(JIIBC), Vol. 17, No. 2, pp. 233–237, Apr 2017. DOI:https://doi.org/10.7236/JIIBC.2017.17.2.233.

- [6] Seokchul Lee "W-band dual-channel receiver with active power divider and temperature-compensated circuit" Electronics Letters. Vol. 52, No. 10, May 12, 2016. DOI: https://doi.org/10.1049/el.2015.3781

- [7] Wansik Kim, "Development and Manufacture of W-band MMIC Chip and manufacture of Transceiver", The Journal of The Institute of Internet, Broadcasting and Communication (JIIBC), Vol. 19, No.6, pp. 175–181, Dec 2019. DOI: https://doi.org/10.7236/JIIBC.2019.19.6.175.

- [8] Wansik Kim, Jongpil Kim, Mihui Seo, Sosu Kim "Domestic Development and Module manufacturing Results of W-band PA and LNA Chip" IIBC Vol. 21, No. 3, pp.29-34, Jun.30, 2021 DOI: https://doi.org/10.7236/JIIBC.2021.21.3.29

- [9] Ilgwon Kim, Wansik Kim, Songcheol Hong "A D-band Variable-Gain LNA with Triple inductive Coupling Gm-boosting" IEEE International Symposium on Radio - Frequency Integration Technology (RFIT) pp.194-196, Dec.31, 2022 Aug. 29, 2022 DOI: https://10.1109/ RFIT54256.2022.9882404

- [10] Wansik, Kim "D-band multi-channel array MFC chip and MIMO radar & Communication" KIMST Annual Conference Proceedings. pp2107, 2022

- [11]Eunhee Kim, Ilkyu Kim, Wansik Kim "Non-Uniform MIMO Array Design for Radar Systems Using Multi-Channel Transceivers" 2023,1,78. DOI: https://doi.org/10.3390/rs15010078

- [12]Hyunji Koo·Ilgwon1 Kim·Jae-Yong Kwon2· Tae-Weon Kang·Chihyun Cho·Wansik Kim· Songcheol Hong "On-wafer Measurement of a D-band Device" KJKIEES vol. 34, No. 1, Jan. 2023. DOI:https://dx.doi.org/10.5515/KJKIEES.202 3.34.1.15

- [13] Wansik, Kim, Hwanyong Yeo "Pre-Validation of Real-time Algorithms for D-band RF Sub-Array MIMO Radar" KIMST Annual Conference Proceedings. pp2107, 2023

- ※ 이 연구는 2023년 정부(방위사업청)의 재원으로 국방과학연구소의 지원을 받아 수행된 미래도전국방기술 연구개발사업임 (No.915027201)