J. Adv. Navig. Technol. 28(1): 129-135, Feb. 2024

# 비주기 전자기 밴드갭이 국소 배치된 고속 패키지/PCB 전원분배망 해석 방안

# Analytical Method for Aperiodic EBG Island in Power Distribution Network of High-Speed Packages and PCBs

## 김명회

한경국립대학교 ICT로봇기계공학부 초연결기술융합연구실

#### Myunghoi Kim

School of ICT, Robotics and Mechanical Engineering, Hankyong National University, Gyeonggi-do, 17579, Korea

# [요 약]

본 연구에서는 고속 반도체 패키지 및 PCB 내 노이즈 저감에 활용되는 비주기 전자기 밴드갭 기반 전원분배망에 대한 해석 방안을 제안한다. 비주기 전자기 밴드갭은 고속 반도체 시스템 성능 저하의 주요 원인 중 하나인 고주파·광대역 전원 노이즈를 효율적으로 감쇠할 수 있는 방안이지만 해석 시간 증대로 인해서 노이즈 감쇠 특성을 예측하는 데 어려움이 있다. 제안하는 해석적 방법에서는 전자기 밴드갭 단위셀 결합 구조에 대한 임피던스 파라미터를 도출하며 국소 배치된 전자기 밴드갭 구조를 포함하는 전원분배망의 전체 임피던스 파라미터를 도출한다. 국소배치된 전자기 밴드갭 구조의 임피던스 파라미터와 기존 전원분배망 구조의 임피던스를 효율적으로 등가치환할 수 있는 수식적인 방안을 제시한다. 제안하는 해석적 방법을 검증하기 위해서 전자기 밴드갭 구조가 국소배치된 PCB 테스트 샘플을 제작했다. 이 구조에 대한 3차원 전자장 시뮬레이션 결과, 측정결과, 제안 방안 결과를 비교한 결과 제안하는 해석적 방안은 높은 정확도를 보여줬으며 기존 3차원 전자장 시뮬레이션 기반 해석 방법 대비 99.7% 해석 시간 단축을 달성했다.

#### [Abstract]

In this paper, an analytical approach for the design and analysis of an aperiodic electromagnetic bandgap (EBG)-based power distribution network (PDN) in high-speed integrated-circuit (IC) packages and printed circuit boards (PCBs) is proposed. Aperiodic EBG is an effective method to solve the noise problem of high-speed IC packages and PCBs. However, its analysis becomes challenging due to increased computation time. To overcome the problem, the proposed analytical method entails deriving impedance parameters for EBG island and the overall PDN, which includes locally placed EBG structures. To validate the proposed method, a test vehicle is fabricated, demonstrating good agreement with the measurements. Significantly, the proposed analytical method reduces computation time by 99.7 % compared to the full-wave simulation method.

Key word: Electromagnetic bandgap, Electromagnetic compatibility, IC package, Power/ground noise.

http://dx.doi.org/10.12673/jant.2024.28.1.129

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-CommercialLicense(http://creativecommons

.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Received 27 January 2024; Revised 22 February 2024 Accepted (Publication) 24 February 2024 (29 February 2024)

\*Corresponding Author: Myunghoi Kim

**Tel:** +82-31-670-5295 **E-mail:** mhkim80@hknu.ac.kr

# │. 서 론

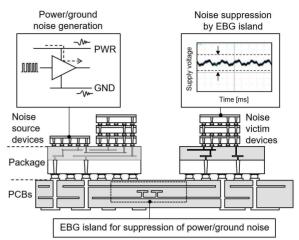

최근 들어서 반도체 시스템의 동작 속도와 데이터 전송속도의 급격한 증가로 인하여 반도체 패키지 및 보드 (PCBs; printed circuit boards) 레벨에서의 고주파·광대역 전원 노이즈 문제가 심각해지고 있다. 반도체 고주파 전원 노이즈는 그림 1에서 보는 것처럼 주로 고속으로 동작하는 반도체로부터 생성되어서 패키지/PCB 전원분배망을 통해서 전파하는 특성을 가진다. 이런 패키지/PCB 레벨의 전원노이즈 감쇠를 위한 기존 방법은 부품 형태의 디커플링 커패시터를 사용하는 것이다. 하지만 실제 제작된 디커플링 커패시터의 기생 인덕터스문제로 인해서 GHz에 이르는 고주파 대역에서 감쇠 성능이크게 저하된다. 따라서 이 문제를 해결하고 고주파 대역에서 전원 노이즈를 효과적으로 감쇠시킬 새로운 방법이 필요하게되었다 [1],[2].

고속 패키지/PCB 고주파·광대역 전원 노이즈 감쇠를 위해서 전자기 밴드갭 (EBG; electromagnetic bandgap) 구조가 소개되었다 [3]. EBG 구조는 고주파·광대역 노이즈 감쇠 특성, 매우 높은 감쇠 레벨, 기판에 집적할 수 있는 구조 형태의 장점들로 인해서 많은 연구가 수행되었다 [4]-[8]. 초기 연구들은 EBG 구조의 특성 최대화를 위해서 패키지 및 PCB 전원분배망 전체에 주기적으로 배치하는 방법에 초점을 맞추었다. 하지만 주기성 확보를 위해서 전역적으로 배치하는 방식은 EBG 구조 이외에 다른 인터커넥트와 접지 구조들과 간섭을 유발하는 문제점이 있었다. 이를 해결하기 위해서 EBG 구조를 국소배치하는 방안에 대한 연구들이 소개되었다.

하지만 EBG 구조의 국소 배치는 주기성을 보장하지 않는 문제가 있다. 주기성이 확보되지 않으면 EBG 구조의 노이즈 감쇠 특성 예측을 위해서 주로 사용하는 Floquet 이론 기반 분 산 (dispersion) 해석을 수행할 수 없게 된다. Floquet 이론 기반 분산 해석은 EBG 단위셀 만을 해석하기 때문에 해석 시간이 짧은 장점이 있다. 하지만 이 방법을 사용하지 못하기 때문에 전체 전원분배망에 대해서 3차원 전자장 시뮬레이션 수행을 해야 한다. 이때, 전자기 밴드갭이 국소 배치된 전원분배망은 전원/접지층으로 구성되는 일반적인 전원분배망과 전자기 밴 드갭 구조가 혼합되어 있는 이종 구조 형태라서 3차원 전자장 시뮬레이션 해석에 있어 많은 시간이 걸리는 문제가 있다. 일 반적으로 전자기 밴드갭 기반 전원분배망 설계 시 다양한 형 태에 대해서 다수의 해석이 필요하므로 긴 연산 시간은 전자 기 밴드갭 구조의 최적화 된 설계를 어렵게 만드는 원인이 된 다.

본 논문에서는 전자기 밴드갭 기반 전원분배망의 임피던스 파라미터를 신속하게 도출하기 위한 해석적 방안을 제안한다. 전자기 밴드갭 단위셀들로 구성된 비주기 국소 배치 구조의 임피던스 파라미터 및 전체 전원분배망 구조의 임피던스 파라미터를 수식 기반으로 도출하는 방안을 제시한다. 본 논문의 구성을 살펴보면, I장에서는 연구 필요성에 대한 서론을 기술

그림 1. 고속 패키지/PCB 전원분배망 노이즈 감쇠 개념도

**Fig. 1.** Power/Ground noise suppression in high-speed packages and PCBs.

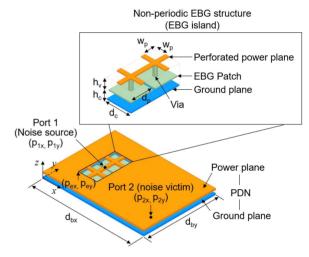

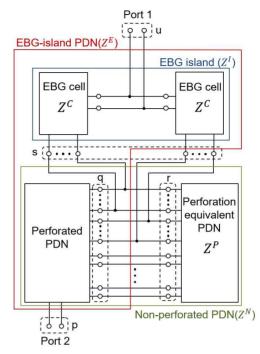

그림 2. 비주기 전자기 밴드갭 기반 전원분배망

Fig. 2. Aperiodic EBG-based power distribution network.

하고 II장에서는 해석 방안에 대해서 제안한다. III장에서는 제안하는 해석 방안을 검증하며 끝으로 IV장에서는 결론에 대해서 기술한다.

# Ⅱ. 비주기 전자기 밴드갭 전원분배망 해석 방안

고속 반도체 시스템용 패키지 및 PCB에서 구성 가능한 비주기 전자기 밴드갭 기반 전원분배망의 예를 그림 2에 나타내었다. 이 전원분배망은 전원 및 접지 공급을 위하여 유전체를 사이에 두고 서로 마주 보는 직사각형 형태의 전도체 평면으로 구성된다. 고주파/광대역 전원노이즈 감쇠를 위하여 전원 평면에는 비주기 전자기 밴드갭 구조가 삽입되어 있다. 비주기 전자기 밴드갭 구조 (EBG island)는 2개의 EBG 단위셀 구조가 나란히 연결된 구조이다. EBG 단위셀 구조는 다공성 전원 평면, EBG 패치, via, 접지 평면으로 구성된다. 다공성 전원 평면, EBG 패치, via, 접지 평면으로 구성된다. 다공성 전원 평

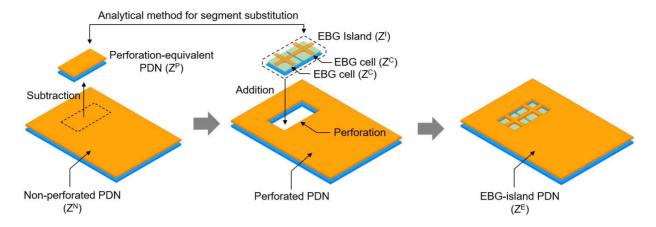

그림 3. 일반 PDN에서 EBG island를 등가 치환하는 해석적 방안 개념과 주요 구조의 임피던스 파라미터 표현 Fig. 3. Analytical approach based on segment substitution and representation of impedance parameters.

면과 EBG 패치는 via를 통해서 연결된다. 전원 평면의 다공성 구조 형상은 직사각형 형태이며 이를 통해서 EBG 단위셀의 전원 평면은 고주파 해석 측면에서 좁은 폭을 가지는 전송선으로 간주할 수 있으며 노이즈 감쇠 특성 역시 향상시킬 수 있다 [6]. EBG 단위셀 연결 부위에 노이즈 소스 가능성이 높은 고속 디지털 반도체 회로를 연결할 수 있으며 전원 노이즈에 민감한 RF 회로 같은 경우에는 EBG island 외부에 위치시킬수 있다. 그림 2에서 노이즈 소스 연결 위치는 port 1으로 노이즈 민감 회로 연결 부위는 port 2로 정의한다. 이 전원분배망 예시에서 보여주는 EBG island, 노이즈 소스, 노이즈 민감 회로의 위치는 설계 편의성 및 회로 배치 특성에 따라서 달라질수 있으며 이 논문에서 제안하는 수식 기반 해석적 방법도 위치 변경에 대해서 확장 적용 가능하다.

제안하는 해석적 기법은 EBG island가 포함되지 않은 일반적인 전원분배망에서 EBG island가 배치될 부분을 차지하고 있는 일반 전원분배망 부분을 제거하고 동시에 EBG island를 해당 부분에 삽입하는 단계를 수식 기반으로 도출한 것이다. 그림 3에서 보는 것처럼, 노이즈 감쇠 기능이 없는 일반적인 전원분배망 (non-perforated PDN)의 한 부분에 EBG island를 삽입해서 비주기 전자기 밴드갭 기반 전원분배망 (EBG-island PDN)을 형성한다. 이때, EBG island가 대체하게 되는 non perforated PDN의 부분은 perforation-equivalent PDN이라 한다. 해석적 기법의 주요 구성 요소를 정리해 보면, non-perforated PDN, perforation-equivalent PDN, EBG cell로 구성된 EBG island, EBG-island PDN 이다. 이 구성요소들의 전기적 특성을 나타내는 임피던스 파라미터를 각각  $Z^{N}, Z^{C}, Z^{C}, Z^{C}, Z^{C}$ 로 정의하다.

#### 2-1 Full-cavity mode resonator model

본 논문의 해석적 방법에서 필요로 하는  $Z^N$ ,  $Z^C$ 를 구하기 위해서 full-cavity mode resonator model을 활용한다 [10]. 이모델은 직사각형 형태의 전원분배망의 임피던스 파라미터를

아래와 같은 수식 기반으로 도출할 수 있게 해준다.

$$\begin{split} Z_{ij}^{CAV} &= \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \left( \frac{j\omega\mu h \, C_m^2 \, C_n^2}{d_x d_y \left( k_{xm}^2 + k_{yn}^2 - k^2 \right)} \cos \left( k_{ym} \, T_{yi} \right) \right. \\ &\times \cos \left( k_{xm} \, T_{xi} \right) \cos \left( k_{ym} \, T_{yj} \right) \cos \left( k_{xm} \, T_{xj} \right) \\ &\times \sin \left( \frac{k_{ym} L_{yi}}{2} \right) \sin \left( \frac{k_{xm} L_{xi}}{2} \right) \sin \left( \frac{k_{ym} L_{yj}}{2} \right) \\ &\times \sin \left( \frac{k_{xm} L_{xj}}{2} \right) \right), \end{split} \tag{1}$$

여기서, i,j는 임피던스 파라미터 원소를 구성하는 포트 번호를 나타내며  $T_{xi}$ ,  $T_{yi}$ ,  $T_{xj}$ ,  $T_{yj}$ 는 i 번째, j 번째 포트의 x,y 좌표를 의미한다.  $d_x$ ,  $d_y$ 는 전원분배망 크기를 나타내고  $L_{xi}$ ,  $L_{yi}$ ,  $L_{xj}$ ,  $L_{yj}$  는 포트 크기를 나타낸다. 그리고  $k=\omega\sqrt{\mu\epsilon}$ ,  $k_{yn}=(n\pi/d_y)$ ,  $k_{xm}=(m\pi/d_x)$  이다. m=0 일 때  $C_m=1$ ,  $m\neq0$  일 때  $C_m=\sqrt{2}$ , n=0 일 때  $C_m=1$ ,  $n\neq0$  일 때  $C_m=\sqrt{2}$  이다.

#### 2-2 EBG island 임피던스 도출을 위한 해석적 방안

EBG island의 임피던스를 도출하기 위해서는 EBG 단위셀의 임피던스 파라미터와 이 임피던스 파라미터를 등가적으로 결합하는 방안이 필요하다. EBG 단위셀의 임피던스 파라미터는 [9]에서 소개된 것처럼 EBG 단위셀을 전송선과 직사각형형태의 cavity 구조로 분할 한 후 각각의 임피던스인  $Z_{TL}$ ,  $Z_{CAV}$ 를 산술적으로 합하는 방식을 적용한다. 이를 정리하면 다음과 같다.

$$Z^C = Z^{TL} + Z^{CAV} \tag{2}$$

$$Z_{ii}^{TL} = Z_A^{TL} - \frac{Z_B^{TL} Z_C^{TL}}{Z_D^{TL}} + \left(\frac{Z_B^{TL}}{Z_D^{TL}}\right)^2 \left(j\omega L_v + \frac{4}{Z_D^{TL}}\right)^{-1}, (i = 1, 2, 3, 4)$$

(3)

131 www.koni.or.kr

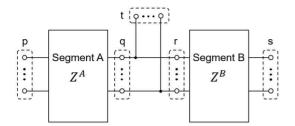

그림 4. EBG 단위셀이 결합된 EBG island 임피던스 도출을 위한 임피던스 연결도

Fig. 4. Impedance diagram for recombination of EBG unit cells.

$$Z_{ij}^{TL} \!=\! \left(\frac{Z_{B}^{TL}}{Z_{D}^{TL}}\right)^{\!\!2} \!\! \left(j\omega L_{v} + \frac{4}{Z_{D}^{TL}}\right)^{\!\!-1}, \left(i,j=1,2,3,4,i\neq j\right) \quad \text{(4)}$$

$$Z_A^{TL} = Z_D^{TL} = -jZ_0 \cot(\beta d_o/2)$$

(5)

$$Z_B^{TL} = Z_C^{TL} = -jZ_0 \csc(\beta d_c/2)$$

(6)

여기서,  $Z_{ii}^{TL}$ ,  $Z_{ij}^{TL}$ 은 EBG 단위셀 전송선 부분의 self-, transferimpedance를 나타낸다. EBG 단위셀의 직사각형 형태의 cavity 구조의 임피던스 파라미터인  $Z^{CAV}$ 는 full-cavity mode resonator model을 이용해서 얻어진다.

EBG island의 임피던스를 구하기 위해서는 위에서 구한 EBG 단위셀 임피던스  $Z_c$ 를 결합하는 해석적 방안이 필요하다. 본 논문에서 고려하는 EBG 단위셀은 4개의 포트로 구성되며 이 중 하나의 포트가 이웃하는 EBG 단위셀과 연결되는 구조이다. 하지만 일반적인 경우에 적용 가능한 해석적 방안을 도출하기 위해서 그림 4와 같이 임의의 포트에 대한 임피던스결합을 고려한다. Segment A, B는 포트 그룹 q, r을 통해서 서로 연결되며 이때, 연결 완료된 포트가 노이즈 소스가 연결되는 포트 그룹 t가 된다. 그리고 segment A, B의 나머지 포트 그룹인 p, s는 외부 전원분배망과 연결되는 역할을 한다. Segment A, B의 임피던스 파라미터는 각각  $Z^A$ ,  $Z^B$ 로 나타낸다. 그러면 포트 그룹 p, s, t의 전압-전류 관계는 다음과 같이 나타낼수 있다.

$$\begin{pmatrix} V_{p} \\ V_{s} \\ V_{t} \end{pmatrix} = (Z^{A})^{+} (Z^{B}) \begin{pmatrix} I_{p} \\ I_{s} \\ I_{t} \end{pmatrix} = Z^{I} \begin{pmatrix} I_{p} \\ I_{s} \\ I_{t} \end{pmatrix}, \tag{7}$$

여기서.

$$Z^{A'} = \begin{pmatrix} E & 0 & Z_{pq}^A (Z_{rr}^B)^{-1} \\ 0 & E & Z_{sr}^B (Z_{qq}^A)^{-1} \\ 0 & 0 & E + Z_{rr}^B (Z_{qq}^A)^{-1} \end{pmatrix}, \tag{8}$$

그림 5. 비주기 전자기 밴드갭 기반 전원분배망 임피던스 도출을 위한 임피던스 연결도

Fig. 5. Impedance diagram for extraction of impedance parameters of EBG-island PDN

$$Z^{B} = \begin{pmatrix} Z_{pp}^{A} & Z_{pq}^{A} (Z_{rr}^{B})^{-1} Z_{rs}^{B} & Z_{pq}^{A} \\ Z_{sr}^{B} (Z_{qq}^{A})^{-1} Z_{qp}^{A} & Z_{ss}^{B} & Z_{sr}^{B} \\ Z_{rr}^{B} (Z_{qq}^{A})^{-1} Z_{qp}^{A} & Z_{rs}^{B} & Z_{rr}^{B} \end{pmatrix}, \tag{9}$$

그리고 E는 단위행렬을 나타낸다. 위에서 도출한 임피던스 결합 해석적 방안에서  $Z^A = Z^C$ ,  $Z^B = Z^C$  로 설정하면 EBG island의 임피던스 파라미터  $Z^I$ 를 구할 수 있다.

최종적으로 EBG island 기반 전원분배망의 임피던스 파라 미터  $Z^f$ 를 구하기 위한 해석적 방안을 도출한다. 이를 위해서 그림 5에 보는 것과 같은 임피던스 관계도를 구성한다. 이 구성도는 그림 3에 나타낸 것과 같이 EBG island의 임피던스 파라미터  $Z^I$ , non-perforated PDN의  $Z^N$ , perforation equivalent PDN의  $Z^P$ 의 관계를 보여준다. non-perforated PDN은 perforated PDN과 perforation equivalent PDN이 연결된 구조이다.

Perforated PDN의 경우에는 임피던스 파라미터 도출이 복잡한 문제를 가지고 있다. 하지만 본 논문에서 도출하는 해석적방안에서는 임피던스 파라미터 도출이 복잡한 임피던스 파라미터 도출이 필요 없다는 장점을 가지고 있다.  $Z^N$ ,  $Z^P$ 의 경우에는 앞서 소개한 full-cavity mode resonator model을 적용하여구할 수 있고  $Z^1$ 의 경우에는 앞서 제안한 해석적 방안을 통해서 구할 수 있다. 이렇게 구한 임피던스 파라미터를 활용하여 최종적으로 비주기 저자기 밴드갭 기반 전원분배망의 임피던

표 1. 해석 방법 검증을 위한 예시 구조 설계 변수 및 치수 **Table. 1.** Design parameters and dimensions of test

vehicles for verifying a proposed analysis method

| Parameter       | Dimensions (mm) | Parameter       | Dimensions (mm) |

|-----------------|-----------------|-----------------|-----------------|

| $d_c$           | 6               | $d_p$           | 5.8             |

| $h_{\rm v}$     | 0.8             | h <sub>c</sub>  | 0.1             |

| d <sub>bx</sub> | 70              | $d_{by}$        | 50              |

| p <sub>1x</sub> | 34.25           | p <sub>1y</sub> | 25              |

| p <sub>2x</sub> | 6.8             | $p_{2y}$        | 10.2            |

| p <sub>ex</sub> | 31.5            | p <sub>ey</sub> | 19              |

| Wp              | 2.75            | via radius      | 0.2             |

스 파라미터를 다음과 같이 구할 수 있다. 여기서 port 그룹 p는 노이즈 소스가 연결되는 port 1을 포함할 수 있으며, 포트그룹 p는 노이즈 민감 회로가 연결되는 port 2를 포함할 수 있다.

$$\begin{pmatrix} V_{p} \\ V_{u} \\ V_{s} \end{pmatrix} = (Z^{A''})^{-1} (Z^{B''}) \begin{pmatrix} I_{p} \\ I_{s} \\ I_{t} \end{pmatrix} = Z^{E} \begin{pmatrix} I_{p} \\ I_{s} \\ I_{t} \end{pmatrix}, \tag{10}$$

여기서.

$$Z^{A''} = \begin{pmatrix} E & 0 & -Z_{ps}^{N} \left[ \left( Z_{rr}^{P} \right)^{-1} - \left( Z_{tt}^{I} \right)^{-1} \right] \\ 0 & E & -Z_{ut}^{I} \left( Z_{tt}^{I} \right)^{-1} \\ 0 & 0 & E - Z_{ss}^{F} \left[ \left( Z_{rr}^{P} \right)^{-1} - \left( Z_{tt}^{I} \right)^{-1} \right] \end{pmatrix}, \tag{11}$$

$$Z^{B''} = \begin{pmatrix} Z_{pp}^{N} & Z_{ps}^{N} (Z_{tt}^{I})^{-1} Z_{tu}^{I} & Z_{ps}^{N} \\ 0 & Z_{uu}^{I} - Z_{ut}^{I} (Z_{tt}^{I})^{-1} Z_{tu}^{I} & 0 \\ Z_{sp}^{N} & Z_{ss}^{N} (Z_{tt}^{I})^{-1} Z_{tu}^{I} & Z_{ss}^{N} \end{pmatrix}.$$

(12)

# Ⅲ. 해석 방안 검증

#### 3-1 측정 구성

본 연구에서 제안하는 해석 방안을 검증하기 위해서 고속 반도체 시스템 패키지 및 PCB에서 많이 활용되는 그림 3과 같은 구조를 예시로 고려했다. 이 구조에 대한 3차원 전자장 시뮬레이션 결과와 측정 결과를 제안하는 해석적 방안 결과와 비교했다. 3차원 전자장 시뮬레이션은 유한요소해석법 (finite element method) 기반 Ansys사의 HFSS 상용 소프트웨어를 이 용했다. 표 1에는 그림 3에 나타난 예시 구조의 설계 변수에 대 한 치수 값이 나타나 있다.

전체 전원분배망 크기는 70 mm × 50 mm 이다. EBG island 를 구성하는 EBG 단위셀의 크기는 6 mm × 6 mm 이며 EBG patch 크기는 5.8 mm × 5.8mm 이다. 전원 평면에 형성하는 다 공성 구조 길이  $\mathbf{w}_p = 2.75$  mm 이다. 전원분배망 하단 좌측에 위치하는 원점을 기준으로 EBG island 시작점 위치  $(x_l, y_l) =$

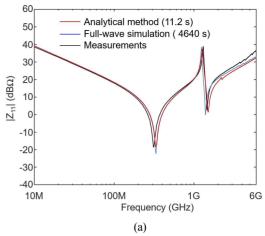

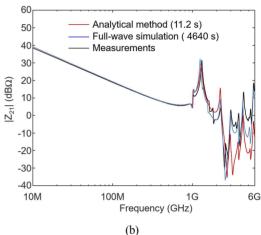

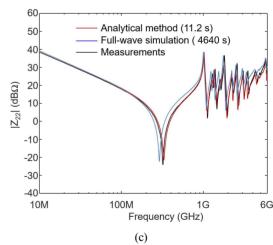

**그림 6.** 제안 해석 방안 검증을 위한 임피던스 파라미터 도출 결과 비교 (a) Z<sub>11</sub>, (b) Z<sub>21</sub>, (c) Z<sub>22</sub>

Fig. 6. Comparison of impedance parameters (a)  $Z_{11}$ , (b)  $Z_{21}$ , (c)  $Z_{21}$  for validation of proposed analytical method

(31.5 mm, 19 mm) 이다. Port 1과 port 2의 위치는 각각 (34.25 mm, 25 mm), (6.8 mm, 10.2 mm) 이다.

133 www.koni.or.kr

전원분배망의 전원 평면과 접지 평면 사이 유전체 두께는 0.9 mm이고 유전체 종류는 FR-4 ( $\epsilon_r = 4.4$ ,  $\tan \delta = 0.02$ )이다. EBG 단위셀에서 전원 평면과 EBG patch 사이의 유전체 두께는 0.8 mm 이고 EBG patch와 접지면 사이 두께는 0.1 mm 이다. 유전체는 FR-4를 사용한다. PCB 공정을 이용해서 제작한 샘플의 scattering parameters를 벡터망분석기를 이용해서 측정한후 최종적으로 임피던스 파라미터로 변환한다.

#### 3-2 검증 결과

비주기 전자기 밴드갭 구조 기반 전원분배망 예시 구조에 대한 3차원 전자장 시뮬레이션 결과, 측정결과, 해석적 방안 결과를 그림 6에서 비교한다. 그림 6 (a), (b), (c)는 각각  $Z_{11}$ ,  $Z_{21}$ ,  $Z_{22}$  결과를 보여준다. 전원분배망 구조의 경우 수동회로 여서 상호성 (reciprocity) 특성을 가지기 때문에  $Z_{12}$  특성은  $Z_{21}$  과 동일하다. 제안하는 해석적 방안 결과와 시뮬레이션 결과, 측정결과가 전체적으로 매우 유사함을 알 수 있다. 노이즈 소스가 연결되는 port 1의 self-impedance 특성을 보여주는  $Z_{11}$  결과를 살펴보면 저주과 영역에서 capacitive, inductive 특성을 보여주며 뒤이어 모드 공진이 발생하는 것을 확인할 수 있다.

Port 2에서도 비슷한 형태로 임피던스 특성이 나타나는 것을 확인할 수 있다. 다만, EBG island의 영향으로  $Z_{11}$ 에서 모드 공진이 적게 발생하는 것을 알 수 있다. 노이즈 저감 특성을 보여주는  $Z_{21}$ 의 경우에도 GHz 대역의 고주파 영역에서 낮은 임 피던스 특성을 보여주는 것을 확인할 수 있다. 다만 고주파 대역에서 해석 방안이 보여주는 오차는 EBG 단위셀과 주변 전원분배망 구조의 간섭 성분을 추가함으로써 개선할 수 있을 것이다. 그림 6에서 보는 것처럼 제안하는 해석방안 결과는 기존 3차원 전자장 시뮬레이션 결과 및 측정결과와 높은 유사성을 보여준다.

기존 3차원 전자장 시뮬레이션으로부터 해석 결과를 얻는데 걸리는 시간은 4640 s로 결과를 얻는데까지 매우 긴 연산시간을 필요로 한다. 하지만 제안하는 해석 방안의 연산시간은 11.2 s로 기존 방법 대비 99.7% 의 해석시간 단축을 달성했다. 비주기 전자기 밴드갭 기반 전원분배망을 설계하고 최적화하는데 1번의 해석이 아닌 다수의 해석이 필요함을 고려할때 제안하는 해석 방안이 달성한 연산시간 단축은 비주기 전자기 밴드갭 기반 전원 분배망 설계와 최적화에 있어서 매우큰 의미를 갖는다.

#### □V. 결 론

본 연구에서는 비주기 전자기 밴드갭 구조 기반 전원분배 망 특성을 분석하기 위한 해석적 방안을 제안했다. 제안하는 해석적 방안에서는 EBG 단위셀 임피던스 결합 방안, EBG island 치환 임피던스 산출 방안을 수식 기반으로 도출했다. 제 안하는 해석적 방안을 검증하기 위해서 비주기 전자기 밴드갭

구조 기반 전원분배망 예시 구조를 고려했으며 이 구조에 대한 3차원 전자장 시뮬레이션 결과, 측정결과, 제안 방법 결과 비교를 통하여 제안방법의 정확성에 대해서 검증했다. 제안하는 해석방법은 높은 정확도를 보여줬으며, 기존 3차원 전자장 시뮬레이션 대비 99.7 % 의 연산시간 단축 성능을 보여줬다. 제안하는 해석적 방법을 통해서 비주기 전자기 밴드갭 전원분배망의 신속한 설계와 최적화를 수행할 수 있으며 이를 통해서 고속 반도체 패키지 및 PCB 상의 전원 노이즈 저감에 크게 기여할 수 있다.

### **Acknowledgments**

본 연구는 2021년도 한경국립대학교 연구년 경비의 지원에 의한 것임

#### References

- [1] E. -P. Li et al., "Progress review of electromagnetic compatibility analysis technologies for packages, printed circuit boards, and novel interconnects," *IEEE Transactions* on *Electromagnetic Compatibility*, Vol. 52, No. 2, pp. 248-265, May 2010.

- [2] T. -L. Wu, H. -H. Chuang and T. -K. Wang, "Overview of power integrity solutions on package and PCB: Decoupling and EBG isolation," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 52, No. 2, pp. 346-356, May 2010.

- [3] R. Abhari and G. V. Eleftheriades, "Metallo-dielectric electromagnetic bandgap structures for suppression and isolation of the parallel-plate noise in high-speed circuits," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 51, No. 6, pp. 1629-1639, June 2003.

- [4] J. Lee, H. Kim and J. Kim, "High dielectric constant thin film EBG power/ground network for broad-band suppression of SSN and radiated emissions," *IEEE Microwave Wireless Components Letters*, Vol. 15, No. 8, pp. 505-507, Aug. 2005.

- [5] M. S. Zhang, Y. S. Li, C. Jia and L. P. Li, "A Power Plane With Wideband SSN Suppression Using a Multi-Via Electromagnetic Bandgap Structure," IIEEE Microwave Wireless Components Letters, Vol. 17, No. 4, pp. 307-309, Apr. 2007.

- [6] M. Kim, K. Koo, C. Hwang, Y. Shim, J. Kim and J. Kim, "A compact and wideband electromagnetic bandgap structure using a defected ground structure for power/ground noise suppression in multilayer packages and PCBs," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 54,

- No. 3, pp. 689-695, June 2012.

- [7] Y. Kasahara, H. Toyao and E. Hankui, "Compact and multiband electromagnetic bandgap structures with adjustable bandgaps derived from branched open-circuit lines," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 65, No. 7, pp. 2330-2340, July 2017.

- [8] C. Zhi, G. Dong, Z. Zhu and Y. Yang, "A TSV-based 3-D electromagnetic bandgap structure on an interposer for noise suppression," *IEEE Transactions on Components*,

- Packaging and Manufacturing Technology, Vol. 12, No. 1, pp. 147-154, Jan. 2022.

- [9] M. Kim, "Unit-cell-based domain decomposition method for efficient simulation of a truncated electromagnetic bandgap structure in high-speed PCBs," *Electronics*, Vol. 7, No. 9, pp. 1-14, Sep. 2018.

- [10] G.-T. Lei, R. W. Techentin and B. K. Gilbert, "High-frequency characterization of power/ground-plane structures," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 47, No. 5, pp. 562-569, May 1999.

#### 김 명 회 (Myunghoi Kim)

2003년 2월: KAIST 전기 및 전자공학과 (공학사), 2005년 2월: KAIST 전기 및 전자공학과 (공학석사) 2012년 8월: KAIST 전기 및 전자공학과 (공학박사). 2005년 2월 ~ 2008년 7월 : 국방과학연구소

2012년 9월 ~ 2015년 8월 : 한국전자통신연구원, 2015년 9월 ~ 현재 : 한경국립대학교 ICT로봇기계공학부 부교수

※관심분야: Signal Integrity, EMI/EMC, 반도체 패키지 설계, Microwave 회로

135 www.koni.or.kr